Навигация

Подчиненный последовательный резким

6.1.1. Подчиненный последовательный резким

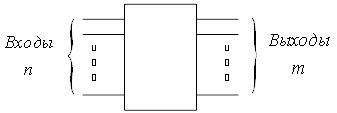

В этом режиме FPGA принимает конфигурационные данные в последовательной форме от последовательного ПЗУ или от другого источника последовательных конфигурационных данных.

Данные последовательного битового потока (bitstream) должны быть установлены на входе DIN незадолго до появления нарастающего фронта сигнала, генерируемого внешним источником и подаваемого на вход CCLK.

Несколько микросхем FPGA могут быть соединены в цепочку для конфигурирования от единого внешнего источника конфигурационных данных. После того как одна из микросхем сконфигурирована, данные для следующей появляются на выходе DOUT. Изменение данных на выходе DOUT происходит после нарастающего фронта сигнала на входе CCLK.

Процесс стробирования данных, подаваемых на вход DIN по нарастающему фронту CCLK, отличается от аналогичного процесса в старых семействах микросхем FPGA, но это не приводит к возникновению проблем для смешанных конфигурационных цепочек. Такое изменение сделано для увеличения скоростей последовательного конфигурирования цепочек FPGA, состоящих только из микросхем Virtex.

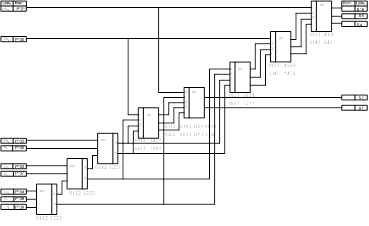

На Рис. 12 изображена полная схема, совмещающая подчиненные режимы и ведущий режим. FPGA Virtex, конфигурируемые в подчиненном режиме, должны быть подключены так же, как устройство, изображенное третьим слева.

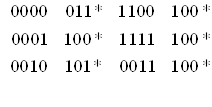

Подчиненный последовательный режим выбирается заданием кода <111> на входах режима конфигурирования (М2, Ml, М0). Внутренние высокоомные резисторы на режимных контактах «подтягивают» данные входы в состояние высокого логического уровня и, таким образом, задают этот режим по умолчанию, если выходы не имеют внешних подключений. На Рис. 13 изображена временная диаграмма для данного режима.

В Табл. 10 содержится более подробная информация для величин, приведенных на Рис. 13. Для FPGA, соединенных в цепочку, процесс конфигурирования должен быть задержан до тех пор, пока на контактах всех микросхем цепочки не появится высокий логический уровень.

Таблица 10. Параметры сигналов подчиненного и ведущего режимов| Параметр | Обозначение | Значение | ||

| min | max | |||

| Предустановка/удержание входного сигнала DIN, подчиненный режим | 1/2* | 5.0 нс/0 нс | ||

| Предустановка/удержание входного сигнала DIN, ведущий режим | 1/2* | 5.0 нс/0 нс | ||

| Задержка сигнала DOUT | 3* | 12 нс | ||

| Длительность высокого уровня | 4* | 5.0 нс | ||

| Длительность низкого уровня | 5* | 5.0 нс | ||

| Частота | 66 МГц | |||

| *См. рис. 13. | ||||

6.1.2. Ведущий последовательный резким

В ведущем последовательном режиме с выхода CCLK FPGA сигнал подается на соответствующий вход микросхемы ППЗУ, которая передает данные на DIN-вход той же микросхемы FPGA. Прием данных в FPGA осуществляется по каждому нарастающему фронту сигнала CCLK. После полного конфигурирования микросхемы, данные для следующих устройств, соединенных цепочкой, появляются на выходе DOUT после каждого нарастающего фронта сигнала CCLK. Данные конфигурирования, поступающие на все микросхемы FPGA, соединенные в цепочку, обязательно начинаются с блока, называемого преамбулой.

Интерфейс, поддерживающий этот режим, идентичен интерфейсу подчиненного режима, за исключением того, что для генерации синхросигнала конфигурирования используется внутренний осциллятор FPGA. Частота для этого синхросигнала может быть выбрана из широкого диапазона значений, но по умолчанию всегда используется низкая частота. Переключение на более высокую частоту происходит данными, которые распознаются микросхемой в самом конфигурационном потоке, после чего оставшаяся часть потока загружается уже с новой скоростью. Переключение снова на более низкую частоту запрещается. Частота синхронизации CCLK устанавливается выбором ConfigRate в программе генерации конфигурационного потока. Максимальная частота CCLK, которая может быть выбрана — 60 МГц. Выбирая конкретную частоту CCLK, необходимо убедиться, что используемые ПЗУ и все соединенные в цепочку микросхемы FPGA рассчитаны на конфигурирование в таком темпе.

После включения питания, частота CCLK равна 2.5 МГц. Эта частота используется до момента загрузки битов ConfigRate, после чего частота меняется на новое значение, определенное этими битами. Если в проекте не задается другая частота, то используемая по умолчанию частота равна 4 МГц.

На Рис. 12 показана полная система, содержащая кристалл в ведущем и кристалл в подчиненном режимах. В этой схеме крайнее левое устройство работает в ведущем последовательном режиме. Остальные устройства работают в подчиненном последовательном режиме. На вход микросхемы ППЗУ подается сигнал с контактов микросхемы FPGA. Аналогично, на вход — с выхода DONE. При этом в зависимости от выбранной стартовой последовательности существует конфликт потенциалов на контакте DONE.

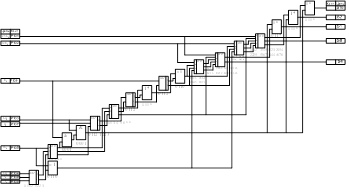

Для последовательного конфигурирования микросхем FPGA необходимо использовать последовательность, изображенную в виде алгоритма на Рис. 14.

Временная диаграмма для ведущего последовательного режима показана на Рис. 15. Данный режим выбирается заданием кода <000> или <100> на входах М2, Ml, М0. Необходимую временную информацию для этого режима содержит Табл. 10.

Время нарастания напряжения питания от уровня 1 В до минимально допустимого значения не должно превышать 50 мс, в противном случае необходимо удерживать сигнал в состоянии низкого логического уровня до момента достижения допустимого уровня .

Похожие работы

... значительно снизить их себестоимость. До недавнего времени, несмотря на все достоинства ПЛИС Xilinx, существовало обстоятельство сдерживающее их применение (особенно недорогих кристаллов при разработке несерийных устройств) — необходимость дополнительных затрат на приобретение пакета программных средств проектирования и программирования. Чтобы устранить это препятствие, фирма Xilinx предоставила ...

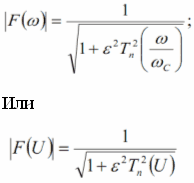

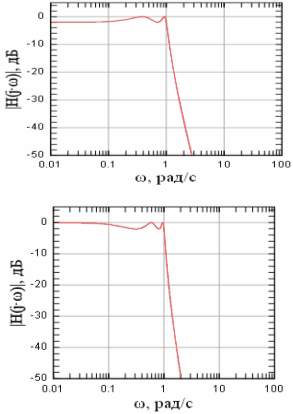

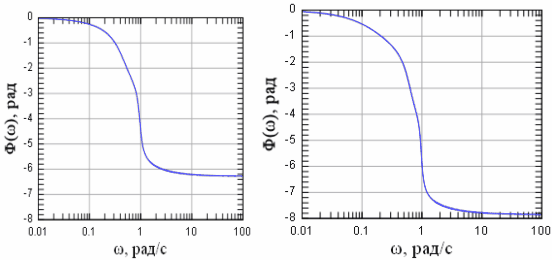

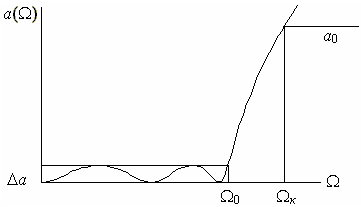

... диаграмм с сохранением результатов в стандартном формате VCD (Value Change Dump), воспринимаемом всеми системами работы с временными диаграммами. [1] 2.МЕТОД ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ Методика проектирования фильтров по рабочим параметрам основана на нахождении значений элементов, нармированных по частоте и сопротивлению нагрузки, путём аппроксимации или с ...

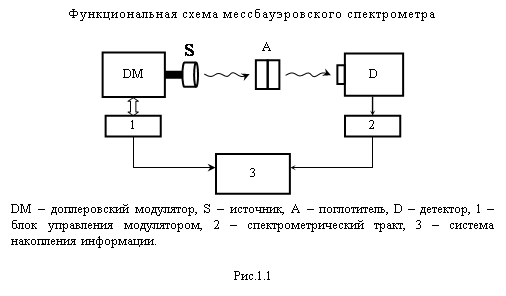

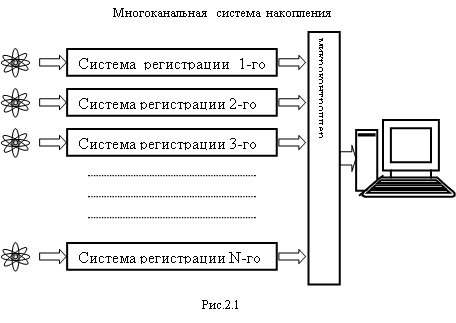

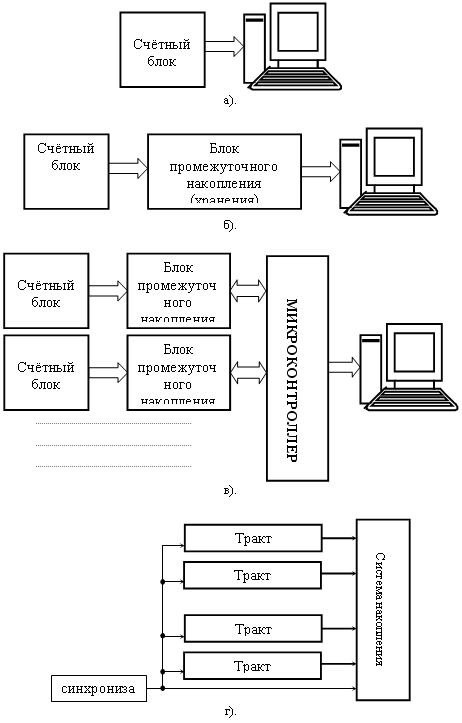

... программирование микроконтроллера, как инструмента накопления данных и управления ресурсами, с учётом необходимой и достаточной степени доступа к конечной аппаратуре. Модуль накопления для задач многомерной мессбауэровской спектрометрии спроектирован с учётом следующих условий: - Синхронизация накопителя с системой доплеровской модуляции осуществляется внешними тактовыми импульсами “старт” и ...

0 комментариев