Навигация

Повторять шаги 2 и 3 до тех пор, пока не будут переданы все данные

4. Повторять шаги 2 и 3 до тех пор, пока не будут переданы все данные.

5. Перевести сигналы и в неактивное состояние.

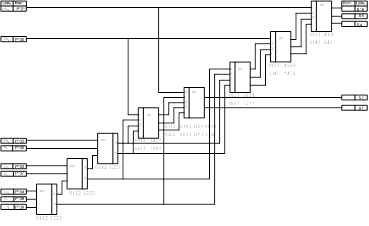

Алгоритм процедуры записи показан на Рис. 17. Отметим, что если сигнал CCLK медленнее, чем , FPGA не будет выставлять сигнал BUSY, в этом случае обмен подтверждениями готовности после реального приема данных не нужен, и данные могут просто вводиться в FPGA по каждому циклу сигнала CCLK.

Преждевременное прекращение процедуры

После установки активного уровня сигнала , пользователь не может переключаться с записи на чтение или наоборот. В противном случае такое действие приведет к преждевременному прекращению текущей пакетной команды. Устройство будет оставаться в состоянии BUSY (занято) до тех пор, пока прерванная процедура будет завершена. После прекращения процедуры, для продолжения приема пакета, необходимо повторить передачу того слова, которое было прервано не на границе слова.

Для того чтобы инициировать преждевременное прекращение процедуры записи, необходимо перевести сигнал в неактивное состояние. Как показано на Рис. 18, прекращение процедуры начнется с приходом нарастающего фронта CCLK.

6.1.4. Использование резкима периферийного сканирования для конфигурирования Virtex

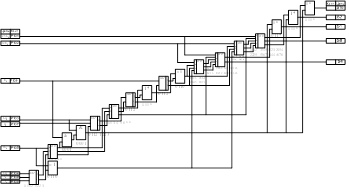

Для конфигурирования в режиме периферийного сканирования используются только специальные контакты порта тестового доступа (Test Access Port — ТАР) в соответствии со стандартом IEEE 1149.1.

Конфигурирование через порт ТАР выполняется с помощью специальной команды CFG_IN. Эта команда позволяет преобразовать входные данные, поступающие на вход TDI, в пакет данных для внутренней шины конфигурирования.

Для конфигурирования FPGA через порт периферийного сканирования необходимо выполнить следующие действия:

1. Загрузить команду CFG_IN во внутренний регистр команд (instruction register — IR).

2. Ввести состояние Shift-DR (SDR).

3. Выдать стандартный конфигурационный bitstream на TDI.

4. Возвратиться к состоянию Run-Test-Idle (RTI).

5. Загрузить в регистр IR команду JSTART.

6. Ввести состояние SDR.

7. Выдать ТСК для длины последовательности (длина программируемая).

8. Возвратиться к состоянию RT1.

Как отмечалось ранее, конфигурирование и обратное считывание всегда доступно в режиме периферийного сканирования. Для выборки режима необходимо подать код <101> или <001> на контакты М2, Ml, М0.

6.2. Последовательность конфигурации

Конфигурирование устройств Virtex -- процесс, состоящий из трех фаз. В первой фазе конфигурирования очищается память. Следующая фаза — загрузка данных в конфигурационную память. Наконец, активизируется логика (фаза Start-Up).

Обычно процесс конфигурирования запускается автоматически после подачи напряжения питания, однако, как будет описано далее, он может быть задержан пользователем. Конфигурационный процесс может также быть инициирован установкой активного уровня сигнала . Переход сигнала в состояние ‘1’ означает окончание фазы очистки памяти, а установка активного уровня сигнала DONE (‘1’) означает окончание процесса в целом.

Временная диаграмма для конфигурационных сигналов после подачи напряжения питания показана на Рис. 19, а соответствующие временные характеристики — в Табл. 12.

6.2.1. Задержка конфигурирования

Конфигурирование FPGA может быть задержано удержанием сигнала на контакте в, состоянии низкого логического уровня до момента готовности системы к конфигурированию. На протяжении фазы очистки конфигурационной памяти последовательность операций состоит из повторения цикла очистки памяти по всем адресам. Эти операции продолжаются до окончания одного полного цикла очистки памяти по всем адресам после установки сигнала на входе в состояние ‘1’. Таким образом, задержка процесса конфигурирования равнозначна продолжению фазы очистки памяти.

Таблица 12. Значения временных параметров при подаче питания.

| Параметр | Значение | |

| min | max | |

| 2.0 мс | ||

| 100 мкс | ||

| 0.5 мкс | 4.0 мкс | |

| 300 нс | ||

Другой вариант — подача от источника с открытым стоком сигнала низкого уровня на вход . Источник сигнала с открытым стоком необходим потому, что контакт — двунаправленный и работает как выход, имеющий низкий логический уровень во время фазы очистки памяти. Увеличение времени удержания низкого логического уровня на этом контакте приводит, к тому, что конфигурационный автомат продолжает выполнять фазу очистки памяти. Таким образом, процесс конфигурирования задерживается, не входя в фазу загрузки данных.

Похожие работы

... значительно снизить их себестоимость. До недавнего времени, несмотря на все достоинства ПЛИС Xilinx, существовало обстоятельство сдерживающее их применение (особенно недорогих кристаллов при разработке несерийных устройств) — необходимость дополнительных затрат на приобретение пакета программных средств проектирования и программирования. Чтобы устранить это препятствие, фирма Xilinx предоставила ...

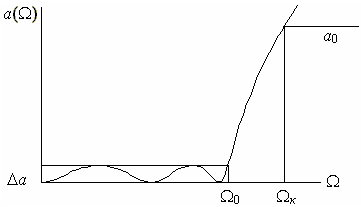

... диаграмм с сохранением результатов в стандартном формате VCD (Value Change Dump), воспринимаемом всеми системами работы с временными диаграммами. [1] 2.МЕТОД ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ Методика проектирования фильтров по рабочим параметрам основана на нахождении значений элементов, нармированных по частоте и сопротивлению нагрузки, путём аппроксимации или с ...

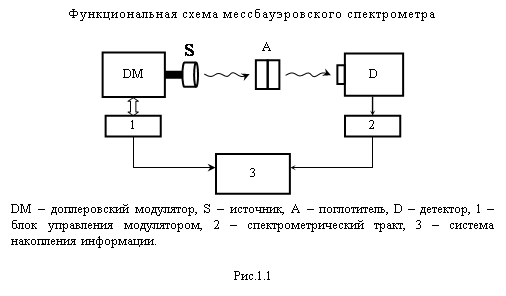

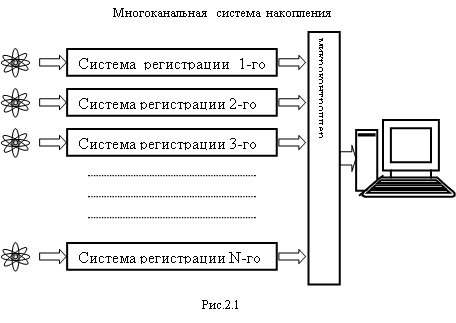

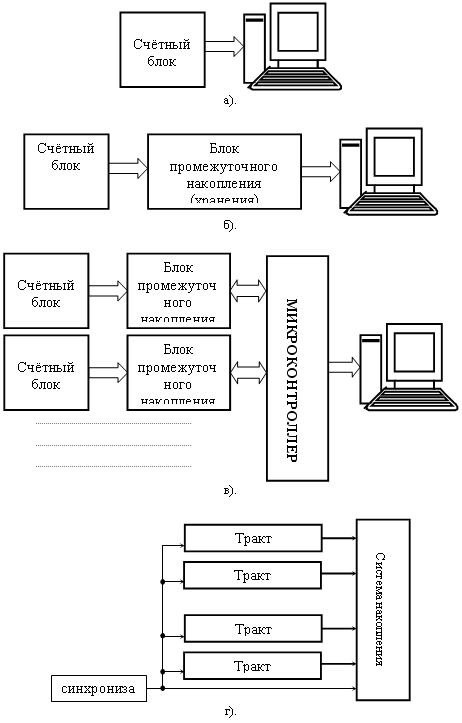

... программирование микроконтроллера, как инструмента накопления данных и управления ресурсами, с учётом необходимой и достаточной степени доступа к конечной аппаратуре. Модуль накопления для задач многомерной мессбауэровской спектрометрии спроектирован с учётом следующих условий: - Синхронизация накопителя с системой доплеровской модуляции осуществляется внешними тактовыми импульсами “старт” и ...

0 комментариев