Навигация

Размещение проекта в кристалл

5.1. Размещение проекта в кристалл

Программное средство размещения и трассировки (place and route — PAR) обеспечивает автоматическое протекание процесса размещения проекта в кристалл, которое описывается ниже. Процедура разбиения на физические блоки получает исходную информацию о проекте в виде перечня связей формата EDIF и осуществляет привязку абстрактных логических элементов к реальным физическим ресурсам архитектуры FPGA (БВВ, КЛБ). Затем процедура размещения определяет наилучшее место для их размещения, руководствуясь информацией о межсоединениях и желаемом быстродействии. В завершении, процедура трассировки выполняет соединения между блоками.

Алгоритмы программы PAR поддерживают автоматическое выполнение большинства проектов. Тем не менее, в некоторых приложениях пользователь при необходимости может осуществлять контроль и управление процессом. Ни этапе ввода проекта пользователь может задавать свою информацию для разбиения, размещения и трассировки.

В программное обеспечение встроено средство Timing Wizard, управляющее процессом размещения и трассировки с учетом требований к временам распространения сигналов. При вводе проекта пользователь задает эту информацию в виде временных ограничений для определенных цепей. Процедуры анализа временных параметров связей анализируют эти, заданные пользователем, требования и пытаются удовлетворить им.

Временные требования вводятся в схему в виде непосредственных системных ограничений, таких, как минимально допустимая частота синхронизации, или максимально допустимая задержка между двумя регистрами. При таком подходе результирующее быстродействие системы с учетом суммарной протяженности путей автоматически подгоняется под требования пользователя. Таким образом, задание временных ограничений для отдельных цепей становится не нужным.

5.2. Верификация проекта

В дополнение к обычному программному моделированию FPGA, пользователь может использовать метод непосредственной отладки реальных цепей. Благодаря неограниченному количеству циклов перепрограммирования кристаллов FPGA, работоспособность проектов можно проверить в реальном масштабе времени, вместо того чтобы использовать большой набор тестовых векторов, необходимых при программном моделировании.

Система проектирования устройств Virtex поддерживает и программное моделирование и метод отладки непосредственно аппаратных цепей. Для выполнения моделирования система извлекает временную информацию, полученную после размещения из базы данных проекта, и вводит ее в сетевой :перечень. Пользователь может и сам проверить критичные по времени части проекта, используя статический временной анализатор TRACE.

Для непосредственной отладки цепей к системе проектирования поставляется кабель для загрузки конфигурационных данных и обратного считывания данных из микросхемы. Этот кабель соединяет персональный компьютер или рабочую станцию с микросхемой FPGA, установленной в законченное устройство. После загрузки проекта в FPGA, пользователь может выполнить один шаг изменения логического состояния схемы, затем выполнить обратное считывание состояния триггеров в компьютер и проанализировать правильность работы схемы. Простейшие модификации проекта при этом можно осуществлять в считанные минуты.

6. Конфигурирование кристалла в устройстве

Микросхемы Virtex конфигурируются путем загрузки конфигурационных данных во внутреннюю конфигурационную память. Часть специальных контактов, которые при этом используются, не могут применяться для других целей, в то же время некоторые из них могут после завершения конфигурирования служить в качестве контактов ввода-вывода общего назначения.

К специальным контактам конфигурирования относятся следующие:

- контакты режима конфигурирования (М2, Ml, М0);

- контакт синхронизации процесса конфигурирования (CCLK);

- контакт ;

- контакт DONE;

- контакты порта периферийного сканирования (TDI, ТОО,

TMS, ТСК).

В зависимости от выбранного режима конфигурирования контакт CCLK может быть либо источником сигнала синхронизации, либо наоборот — приемником сигнала от внешнего генератора синхросигналов.

6.1. Режимы конфигурирования

Virtex поддерживает следующие четыре режима конфигурирования:

— подчиненный последовательный режим (Slave-serial);

— ведущий последовательный режим (Master-serial);

— режим SelectMap;

— режим периферийного сканирования (Boundary Scan — JTAG).

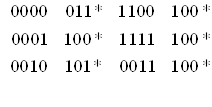

Комбинация кодов на специальных входных контактах (М2, Ml, М0) позволяет выбрать один из режимов конфигурирования, при этом четыре из восьми кодов соответствуют «подтянутому» (pull-up) состоянию входов блоков ввода-вывода до начала процедуры конфигурирования, и еще четыре комбинации состоянию неопределенного потенциала блоков ввода-вывода. Соответствие этих кодов необходимому режиму приведено в Табл. 9.

Таблица 9. Конфигурационные коды.

| Режим | М2 | М1 | М0 | CCLK | Разрядность данных | Последовательный выход DOUT | Контакты «подтянуты» |

| Master-serial | 0 | 0 | 0 | Выход | 1 | Есть | Нет |

| Boundary-scan | 1 | 0 | 1 | 1 | Нет | Нет | |

| SelectMAP | 1 | 1 | 0 | Вход | 8 | Нет | Нет |

| Slave-serial | 1 | 1 | 1 | Вход | 1 | Есть | Нет |

| Master-serial | 1 | 0 | 0 | Выход | 1 | Есть | Да |

| Boundary-scan | 0 | 0 | 1 | 1 | Нет | Да | |

| SelectMAP | 0 | 1 | 0 | Вход | 8 | Нет | Да |

| Slave-serial | 0 | 1 | 1 | Вход | 1 | Есть | Да |

Конфигурирование микросхемы FPGA через порт периферийного сканирования доступно всегда, независимо от значения этого кода. Задание кода отключает другие режимы. Все три контакта режима конфигурирования имеют внутренние «подтягивающие» резисторы и по умолчанию задают, таким образом, состояния высокого логического уровня, если отсутствуют внешние подключения.

Похожие работы

... значительно снизить их себестоимость. До недавнего времени, несмотря на все достоинства ПЛИС Xilinx, существовало обстоятельство сдерживающее их применение (особенно недорогих кристаллов при разработке несерийных устройств) — необходимость дополнительных затрат на приобретение пакета программных средств проектирования и программирования. Чтобы устранить это препятствие, фирма Xilinx предоставила ...

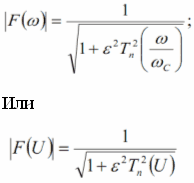

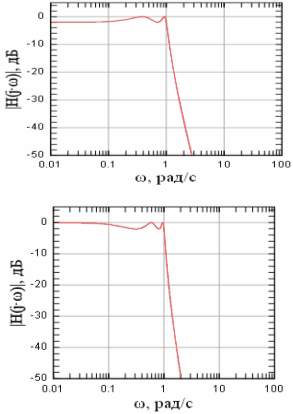

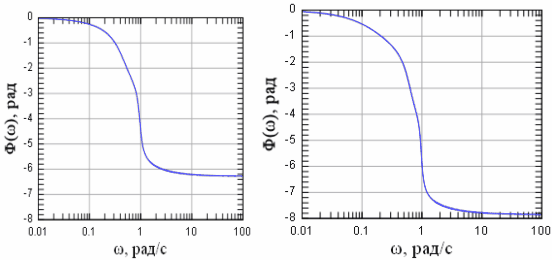

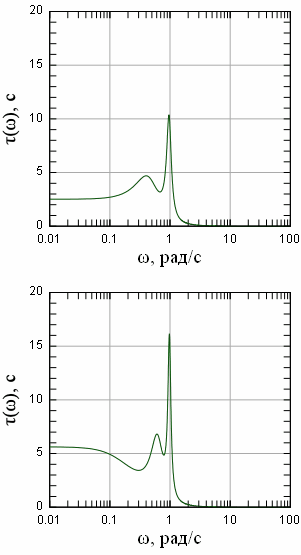

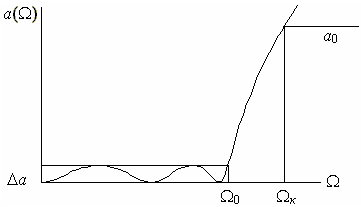

... диаграмм с сохранением результатов в стандартном формате VCD (Value Change Dump), воспринимаемом всеми системами работы с временными диаграммами. [1] 2.МЕТОД ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ Методика проектирования фильтров по рабочим параметрам основана на нахождении значений элементов, нармированных по частоте и сопротивлению нагрузки, путём аппроксимации или с ...

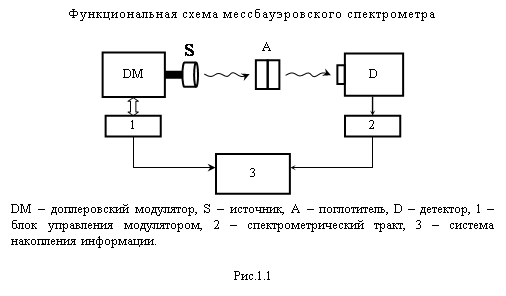

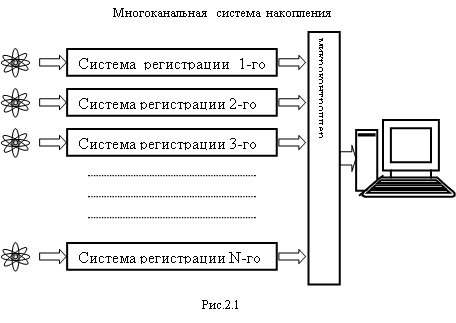

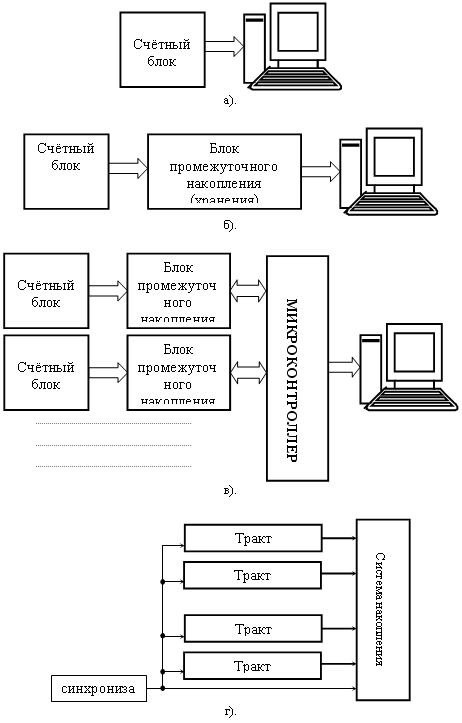

... программирование микроконтроллера, как инструмента накопления данных и управления ресурсами, с учётом необходимой и достаточной степени доступа к конечной аппаратуре. Модуль накопления для задач многомерной мессбауэровской спектрометрии спроектирован с учётом следующих условий: - Синхронизация накопителя с системой доплеровской модуляции осуществляется внешними тактовыми импульсами “старт” и ...

0 комментариев