Навигация

Последовательность вхождения в штатный режим работы

6.2.2. Последовательность вхождения в штатный режим работы

При выполнении вхождения в штатный режим работы по умолчанию глобальный сигнал управления третьим состоянием (global tristate - GTS) активизируется через один цикл CCLK после перехода сигнала DONE в состояние ‘1’. Это позволяет выходам FPGA включиться надлежащим образом.

Одним циклом CCLK позже активизируются сигнал глобальной установки/сброса (Global Set/Reset — GSR) и глобального разрешения записи (Global Write Enable — GWE). Это создает условия для начала нормальной работы внутренних запоминающих элементов.

Временная диаграмма для этих событий может быть изменена. Кроме того, события GTS, GSR и GWE могут активизироваться после перехода всех выходов DONE в высокое состояние при конфигурировании множественных устройств FPGA, что позволяет начинать их работу в штатном режиме синхронно. Во время выполнения последовательности допускается включение на любой фазе паузы до момента нормального захвата следящей системы схемы автоподстройки задержки (DLL).

6.3. Формат потока конфигурационных данных

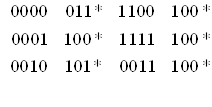

Кристаллы Virtex конфигурируются последовательной загрузкой в них фреймов данных, которые объединены в двоичный поток (bitstream). В Табл. 13 представлены объемы конфигурационной последовательности для кристаллов Virtex.

Таблица 13. Размер конфигурационной последовательности для различных микросхем семейства Virtex

| Кристалл | Конфигурационные биты |

| XCV50 | 559 200 |

| XCV100 | 781 216 |

| XCV150 | 1 040 096 |

| XCV200 | 1 335 840 |

| XCV300 | 1 751 808 |

| XCV400 | 2 546 048 |

| XCV600 | 3 607 968 |

| XCV800 | 4 715 616 |

| XCV1000 | 6 127 744 |

7. Обратное считывание

Конфигурационные данные, записанные в конфигурационной памяти FPGA, могут быть считаны обратно для выполнения верификации. Наряду с этими данными возможно обратное считывание содержимого всех триггеров/защелок, LUTRAMs, BlockRAMs. Эта возможность используется для выполнения отладки проектов в реальном масштабе времени.

8. Характеристики микросхем семейства Virtex по постоянному току

В Табл. 14 приведены максимально допустимые значения параметров микросхем семейства Virtex по постоянному току.

Таблица 14. Диапазон максимально допустимых значений параметров микросхем семейства Virtex по постоянному току

| Обозна-чение | Описание | Значение | Единица измерения | |

| Напряжение питания ядра относительно GND | -0.5…3.0 | В | ||

| Напряжение питания выходных каскадов относительно GND | -0.5…4.0 | В | ||

| Входное опорное напряжение | -0.5…3.6 | В | ||

| Напряжение входного сиг-нала относительно GND | Используя | -0.5…3.6 | В | |

| Не используя | -0.5…5.5 | В | ||

| Напряжение, прикладываемое к 3-стабильному выходу | -0.5…5.5 | В | ||

| Максимальное время нарастания напряжения питания от 1 до 2.375 В | 50 | мс | ||

| Температура хранения (окружающей среды) | -65…+150 | °C | ||

| Максимальная температура припоя | +260 | °C | ||

| Максимальная рабочая температура контактов | +125 | °C | ||

Внимание! Превышение максимальных значений ведет к повреждению кристалла.

В Табл. 15 приведены рекомендуемые значения параметров микросхем семейства Virtex по постоянному току.

Таблица 15. Рекомендуемые значения| Обозна-чение | Описание | Значения | Единица измерения | |

| min | max | |||

| Напряжение питания ядра при =0…+85 °C (коммерческое исполнение) | 2.5 - 5% | 2.5 + 5% | В | |

| Напряжение питания ядра при =0…+85 °C (промышленное исполнение) | 2.5 – 5% | 2.5 + 5% | В | |

| Напряжение питания выходных каскадов при =0…+85 °C (коммерческое исполнение) | 1.4 | 3.6 | В | |

| Напряжение питания выходных каскадов при =0…+85 °C (промышленное исполнение) | 1.4 | 3.6 | В | |

| Время передачи входного сигнала | 250 | нс | ||

Похожие работы

... значительно снизить их себестоимость. До недавнего времени, несмотря на все достоинства ПЛИС Xilinx, существовало обстоятельство сдерживающее их применение (особенно недорогих кристаллов при разработке несерийных устройств) — необходимость дополнительных затрат на приобретение пакета программных средств проектирования и программирования. Чтобы устранить это препятствие, фирма Xilinx предоставила ...

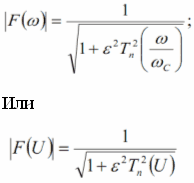

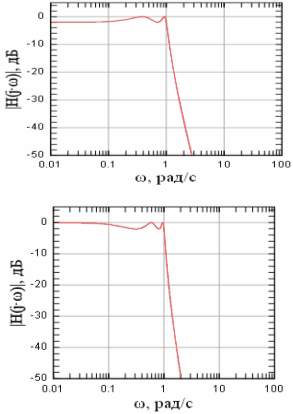

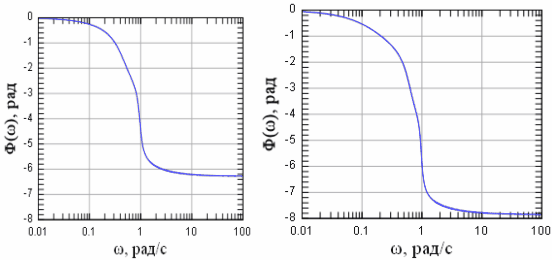

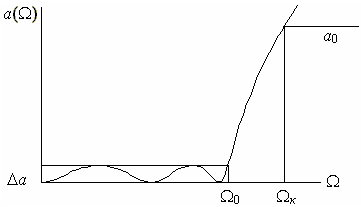

... диаграмм с сохранением результатов в стандартном формате VCD (Value Change Dump), воспринимаемом всеми системами работы с временными диаграммами. [1] 2.МЕТОД ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ Методика проектирования фильтров по рабочим параметрам основана на нахождении значений элементов, нармированных по частоте и сопротивлению нагрузки, путём аппроксимации или с ...

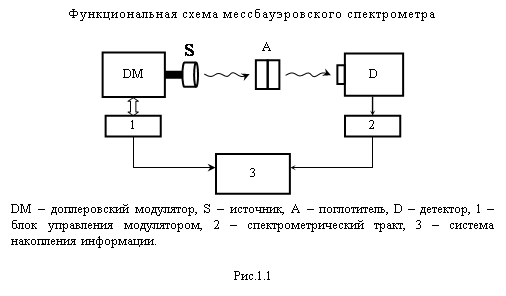

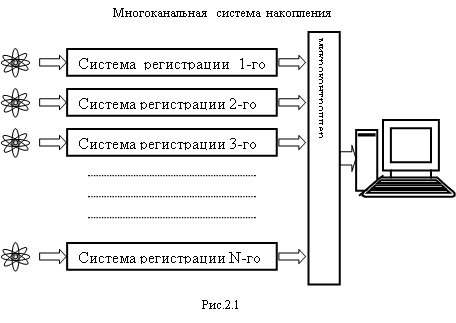

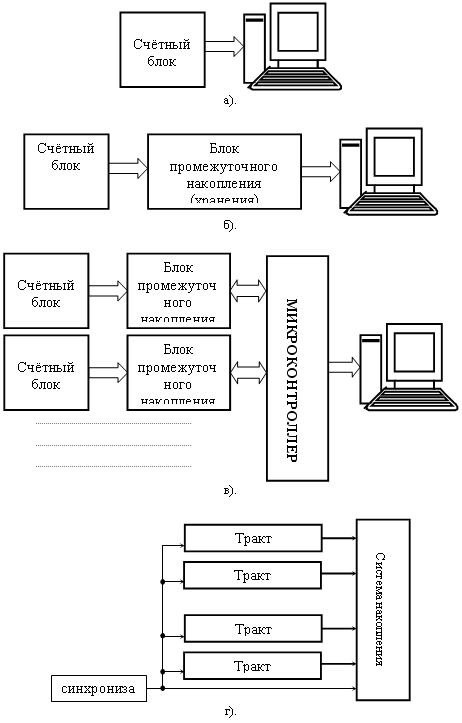

... программирование микроконтроллера, как инструмента накопления данных и управления ресурсами, с учётом необходимой и достаточной степени доступа к конечной аппаратуре. Модуль накопления для задач многомерной мессбауэровской спектрометрии спроектирован с учётом следующих условий: - Синхронизация накопителя с системой доплеровской модуляции осуществляется внешними тактовыми импульсами “старт” и ...

0 комментариев