Навигация

Матричный метод умножения

4. Матричный метод умножения

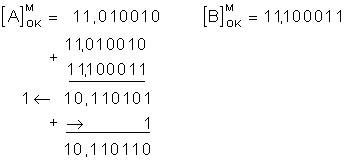

Когда множимое и множитель расположены в регистрах машины, нетрудно образовать сразу все частичные произведения. Следовательно, при наличии дополнительных сумматоров можно складывать сразу несколько частичных произведений, а в предельном случае и все. В этом случае формирование произведения можно себе представить как спуск по дереву сумматоров от слагаемых к их общей сумме. Время спуска по дереву будет зависеть от его организации и типа применяемых сумматоров. Рассмотрим схему умножения на примере двух четырехразрядных чисел:

| А= | а4 | а3 | а2 | а1 | |||

| В= | b4 | b3 | b2 | b1 | |||

| a4b1 | a3b1 | a2b1 | a1b1 | ||||

| a4b2 | a3b2 | a2b2 | a1b2 | ||||

| a4b3 | a3b3 | a2b3 | a1b3 | ||||

| a4b4 | a3b4 | a2b4 | a1b4 | ||||

| c8 | c7 | c6 | c5 | c4 | c3 | c2 | c1 |

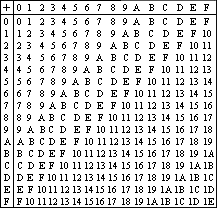

Эту схему умножения можно представить в виде матрицы (таблица 3), каждый элемент которой равен 0 или 1 для р=2. Для получения произведения двух чисел элементы матрицы надо суммировать в соответствии с порядком.

Таблица 3

| аi | ||||

| bi | а4 | а3 | а2 | а1 |

| b1 | a4b1 | a3b1 | a2b1 | a1b1 |

| b2 | a4b2 | a3b2 | a2b2 | a1b2 |

| b3 | a4b3 | a3b3 | a2b3 | a1b3 |

| b4 | a4b4 | a3b4 | a2b4 | a1b4 |

| a3b2 | a4b1 | a2b2 | a3b1 | a1b2 | a2b1 | a1b1 | ||||||||||||||||||||||||

| С | м | С | м | С | м | |||||||||||||||||||||||||

| a3b3 | a4b2 | a2b3 | a1b3 | C1 | ||||||||||||||||||||||||||

| С | м | С | м | С | м | C2 | ||||||||||||||||||||||||

| a4b4 | a3b4 | a4b3 | a2b4 | a1b4 | ||||||||||||||||||||||||||

| С | м | С | м | С | м | |||||||||||||||||||||||||

| C3 | ||||||||||||||||||||||||||||||

| П | а | р | а | л | л | е | л | ь | н | ы | й | с | у | м. | ||||||||||||||||

| C8 | C7 | C6 | C5 | C4 | ||||||||||||||||||||||||||

Рисунок 1- Схема устройства для реализации матричного метода

Элементы, составляющие каждый і-й столбец матрицы, просуммируем с помощью обычных трехвходовых двоичных сумматоров. 3начения переносов с этих сумматоров должны быть слагаемыми для (i+1)-гo столбца. Это приведет к тому, что в каждом (i+1)-м столбце появление слагаемых будет происходить с запаздыванием по времени относительно i-гo столбца.

Схема устройства для реализации этого дерева спуска, которое представляет собой одну из разновидностей матричного алгоритма умножения, представлена на рис. 1.

Для одноразрядных сумматоров время образования суммы больше, чем время образования переноса τп, поэтому наибольшее время спуска по дереву данного вида есть Туск= (n-1)(τсмì+τn); если только все конъюнкции вида aibjпоступают на дерево спуска одновременно. Это время складывается из спуска по самой длинной вертикали, а затем последовательного распространения переноса через сумматоры нижнего ряда вплоть до самого левого. Рассмотренная структура дерева спуска не единственная Время спуска можно еще уменьшить, преобразовав дерево спуска.

5. Выполнение операции деления в ЭВМ

Операция деления встречается сравнительно редко (Р=0,02), однако, реализация ее по подпрограмме занимает достаточно большое время. Поэтому в большинстве современных ЭВМ деление реализуется специальными операционными блоками.

Деление в ЭВМ, также как и умножение, проще всего выполняется в прямом коде. Но в отличие от умножения дробных чисел, где не может возникнуть переполнение разрядной сетки, при делении правильных дробей такое переполнение возможно в случае, когда делимое больше делителя. Признаком переполнения является появление целой части в частном, что грубо искажает результат.

Знак частного при делении определяется сложением по модулю 2 знаковых разрядов делимого и делителя и присваивается частному в конце операции деления.

Частное определяется путем деления модулей исходных чисел. При этом во избежание переполнения разрядной сетки должно соблюдаться условие:

|А|<|В|

где А - делимое, В - делитель. Кроме того: В¹0.

Известны два основных алгоритма выполнения операции деления:

- деление с восстановлением остатков ;

- деление без восстановления остатков.

5.1 Деление чисел с восстановлением остатковПусть необходимо разделить А на В. Тогда частное от деления

Yi=А/В = 0,у1у2у3... уі-1уі= у1 2-1 +у22-2 +у32-3 ... уі-12-і -1+уі2-і (1.1.)

При любом значении і должно выполняться неравенство:

0 ≤ А - ВYi ≤ В2-і

т.е. остаток от деления должен быть меньше делителя, умноженного на 2-і , или:

0 ≤ (А - В Yi )2і ≤ В, обозначим (А - В Yi ) 2і =Rі и получим:

0 ≤ Rі ≤ В. (1.2)

При делении цифры частного определяются последовательно, начиная со старшего разряда. Допустим, что в результате выполнения і циклов получены старшие і разрядов частного, т.е. приближенное значение частного Yi. В следующем (і+1)-цикле будет получено значение (і+1)-го разряда частного. Исходными данными для этого цикла являются Yi и Rі.

Цифра уі+1 может иметь одно из двух значений:

1 или 0. Если уі+1=0, то

Yі+1= Yі+ уі+1х 2-(і+1)= Yі; (1.3.)

Rі+1=(А-В Yі+1) х 2і+1= 2 Rі, (1.4.)

т.е. в частном записывается 0 при условии 0 ≤ Rі+1=2Ri < В. (1.5.)

Если уі+1=1, то Yі+1= Yі+ 2-(і+1); (1.6.)

Rі+1=(А-В х Yі+1) х 2і+1= (А - В х Yi-B х 2-(і+1) 2(і+1)=2 Rі- В, (1.7.)

т.е. цифра частного равна 1, если выполняется условие:

0 ≤ Rі+1=2Ri -В < В (1.8.)

или В ≤ 2Ri < 2В. (1.9.)

Так как всегда выполняется одно из условий (1.5.) или (1.9.), то для определения текущей цифры частного достаточно проверить одно из них.

Обычно проверяют условие (1.5.). Левая часть этого неравенства выполняется заведомо, так как согласно (1.2.) 0 ≤ Rі, то есть очередной остаток перед началом следующего шага деления всегда является положительным числом.

Для проверки правой части неравенства сравним разность (2Rі-В) сравним с нулем. Если эта разность окажется отрицательной, то в (і+1) разряд частного запишем 0 и для подготовки исходных данных для (і+2)-го цикла определим Rі+1 следующим образом:

Rі+1=(2Ri -В) + В =2Ri . (1.10.)

Если разность 2Ri -В окажется положительной, то запишем в (і+1) разряд частного 1, а в качестве исходного значения для следующего (і+2)-го цикла используем вычисленную разность (см. 1.7.): Rі+1=2 Rі- В,

Исходными данными для 1-го цикла являются:

Y0=0

R0=(А-ВY0)20= А< В

т.е. по условию неравенства (1.2.) выполняется и перед началом первого цикла. После окончания n-го цикла получим n-значное частное Yn, вычисленное с недостатком Rn=(A - BYn)2n,который равен остатку от деления А на В, сдвинутому влево на n разрядов.

Правило деления с восстановлением остатков формулируется следующим образом.

Делитель вычитается из делимого и определяется знак нулевого (по порядку) остатка. Если остаток положительный, т.е. |A|>|В|, то в псевдознаковом разряде частного проставляется 1, при появлении которой формируется признак переполнения разрядной сетки и операция прекращается. Если остаток отрицательный, то в псевдознаковом разряде частного записывается 0, а затем производится восстановление делимого путем добавления к остатку делителя. Далее выполняется сдвиг восстановленного делимого на один разряд влево и повторное вычитание делителя. Знак получаемого таким образом остатка определяет первую значащую цифру частного: если остаток положителен, то в первом разряде частного записывается 1, если отрицательный, то записывается 0. Далее, если остаток положителен, то он сдвигается влево на 1 разряд и из него вычитается делитель для определения следующей цифры частного. Если остаток отрицателен, то к нему прибавляется делитель для восстановления предыдущего остатка, затем восстановленный остаток сдвигается на 1 разряд влево и от него вычитается делитель для определения следующей цифры частного и т.д. до получения необходимого количества цифр частного с учетом одного разряда для округления, т. е. до обеспечения требуемой точности деления.

Пример.

А=0,10011; В=0,11001; [-B]доп= 11,00111; |В|= 0,11001

Похожие работы

... с их использованием, имеют свою устойчивую долю рынка. В данной курсовой работе на примере цифрового сигнального процессора семейства ADSP-21xx производится разбор команд умножения и деления, выполняемых в АЛУ. Обобщенная структурная схема персонального компьютера Центральный процессор в персональных компьютерах представляет собой микропроцессор, то есть построен на одной микросхеме (БИС,СБИС). ...

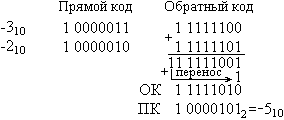

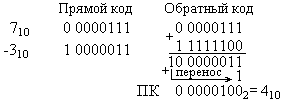

... нельзя рассматривать как единое целое. Кроме того, необходимо кроме сумматора иметь и вычитатель. В результате этого прямой код не применяется для выполнения операции алгебраического сложения, но применяется для выполнения операций умножения и деления. 1.1.3 Дополнительный код В дополнительном коде операция вычитания заменяется операцией алгебраического сложения. При этом знаковый разряд и ...

... позволит технически реализовать четыре действия арифметики в одном устройстве, называемом арифметико-логическом (АЛУ), используя одни и те же электрические схемы. 1.4.1. Представление чисел со знаками При выполнении арифметических операций в ЭВМ применяют прямой, обратный и дополнительный коды. Как уже говорилось выше, кодом называют такую запись числа, которая отличается от естественной и ...

... , связанный с формированием представлений о системно-информационном подходе к анализу окружающего мира, о роли информации в управлении, специфике самоуправляемых систем, общей закономерности информационных процессов в системах различной природы. Основой мировоззрения, главным его компонентом является научная картина мира, рассматриваемая как высший уровень систематизации и обобщения научных ...

0 комментариев