Московский Государственный Университет

Экономики, Статистики и Информатики.

Институт информационных систем.

Кафедра вычислительных систем, сетей и телекоммуникаций.

Курсовая работа по теме:

“Анализ состава АЛУ и принципы выполнения операций умножения и деления в конкретной модели ЭВМ”

| Выполнил студент группы ДП-201: | Зеленов А.В. |

| Руководитель: | профессор Черняк Н. Г. |

Москва, 1998 год.

Задание на курсовую работу на тему:

“Анализ состава АЛУ и принципы выполнения операций умножения и деления в конкретной модели ЭВМ”

студента группы ДП-201 Зеленова А.В.

Введение ( структурная схема ЭВМ , место АЛУ и его взаимодействие с другими устройствами )

Основные параметры и классификация АЛУ

Алгоритм выполнения операций умножения и деления в АЛУ конкретной модели ЭВМ

Заключение ( сравнительный анализ выполнения арифметических команд )

| Исполнитель : | Зеленов А.В. |

| Руководитель : | профессор Черняк Н. Г. |

30

Введение

Создание фирмой Intel первого микропроцессора в 1971 году положило начало эпохе компьютеризации. “Благодаря микропроцессорам компьютеры стали массовым, общедоступным продуктом ”,- заявил Тед Хофф, один из изобретателей первого процессора. Его имя, вместе с именами его коллег - Федерико Феджина и Стива Мейзора, внесено в список лауреатов Национального зала славы изобретателей США, а само изобретение признано одним из величайших достижений ХХ века.

За чуть более чем четвертьвековую историю микропроцессоры прошли поистине гигантский путь. Первый чип Intel 4004 работал на частоте 750 Кгц, содержал 2300 транзисторов и стоил около 200 долларов. Производительность его оценивалась в 60 тысяч операций в секунду. На сегодняшний день рекордные показатели принадлежат микропроцессорам Alpha 21264 фирмы DEC и составляют: 600 МГц, 15.2 миллиона транзисторов, 2 миллиарда операций в секунду и около 300 долларов соответственно.

Сравнение приведенных значений подтверждает оценку успехов микропроцессорной индустрии, данную основателем и председателем совета директоров фирмы Intel Гордоном Муром: “Если бы автомобилестроение эволюционировало со скоростью полупроводниковой промышленности, то сегодня “Роллс-Ройс” стоил бы 3 доллара, мог бы проехать полмиллиона миль на одном галлоне бензина и было бы дешевле его выбросить, чем платить за парковку” [ “Intel на Comtek’98” CDROM - perspectives.html ].

Такое интенсивное развитие технологий в обществе, где основным предметом труда становится информация, является следствием растущего спроса на новые орудия труда - компьютеры. На сегодняшний день компьютеризация является одним из главных направлений научно-технического прогресса и концентрированным его выражением. Количество и качество производимых в стране компьютеров, степень насыщенности вычислительной техникой самых разных отраслей становится одним из основных критериев ее экономического и военного потенциала.

В формируемом ежегодно в США группой экспертов перечне “критических технологий”, охватывающем практически все направления производства, исследований и разработок, оказывающих влияние на военный и экономический статус страны, микроэлектронные технологии традиционно занимают первое место.

В микропроцессорах - наиболее сложных микроэлектронных устройствах - воплощены самые передовые достижения инженерной мысли. В условиях свойственной данной отрасли производства жесткой конкуренции и огромных капиталовложений, выпуск каждой новой модели микропроцессора - так или иначе связан с очередным научным, конструкторским, технологическим прорывом.

Типы микропроцессоровУниверсальные микропроцессоры предназначаются для применения в вычислительных системах : персональных ЭВМ, рабочих станциях, а в последнее время и в массово-параллельных супер-ЭВМ. Основной их характеристикой является наличие развитых устройств для эффективной реализации операций с плавающей точкой над 64 разрядными и более длинными операндами. Предназначаются в основном для проведения научно-технических расчетов.

Цифровые сигнальные процессоры рассчитаны на обработку в реальном времени цифровых потоков, образованных путем оцифровывания аналоговых сигналов. Это обусловливает их сравнительно малую разрядность и преимущественно целочисленную обработку. Однако современные сигнальные процессоры способны проводить вычисления с плавающей точкой над 32-40 разрядными операндами. Кроме того, появился класс медийных процессоров, представляющих собой законченные системы для обработки аудио- и видеоинформации.

Наибольшей специализацией и разнообразием функций обладают микроконтроллеры, используемые во встроенных системах управления, в том числе и в бытовых приборах. Общее число кристаллов с различными системами команд превышает 500, и все они, в силу существования изделий с их использованием, имеют свою устойчивую долю рынка.

В данной курсовой работе на примере цифрового сигнального процессора семейства ADSP-21xx производится разбор команд умножения и деления, выполняемых в АЛУ.

Обобщенная структурная схема персонального компьютера

Центральный процессор в персональных компьютерах представляет собой микропроцессор, то есть построен на одной микросхеме (БИС,СБИС). В его состав входят:

Центральное устройство управления - комплекс средств автоматического управления процессами передачи и обработки информации;

Арифметико-логическое устройство - устройство, осуществляющее обработку информации и выработку признаков управляющих сигналов.

Внутренняя память процессора :

Регистровая память

Постоянная память устройства управления

Модули оперативной и постоянной памяти, связаны с микропроцессором напрямую. Остальные устройства ( монитор, клавиатура, накопители на магнитных носителях и т.д.) связаны с микропроцессором через контроллеры ввода-вывода, которые, в свою очередь, связаны с микропроцессором через системную шину.

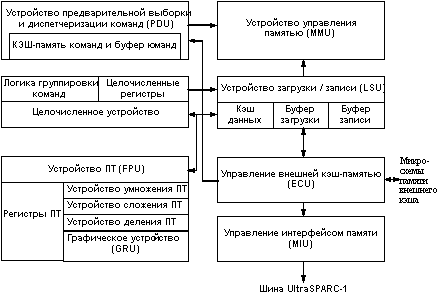

Микропроцессор является ядром ЭВМ (рис.1). Он осуществляет обработку данных и функции управления системой. К функциям управления системой относятся :

инициирование операций ввода-вывода

управление доступом к основной памяти ( работа с виртуальной памятью )

обработка системных событий - прерываний

организация многозадачных режимов работы

Организация центрального процессора определяется архитектурой и принципами работы ЭВМ ( состав и форматы команд, организация памяти ). Логическая структура включает ряд функциональных средств:

средства обработки информации

локальная память

средства управления системой и программами

управление интерфейсом и каналами

Структурно эти средства разбиваются на центральное устройство управления, АЛУ, внутреннюю память и управляющие устройства, связанные с конкретными устройствами вычислительной машины.

Центральное устройство управления принимает и расшифровывает команды, формирует адреса команд и операндов, формирует последовательности управляющих сигналов и обеспечивает координацию работы всех функциональных узлов, посредством выработки синхронизирующих сигналов.

Внутренняя память входит в состав первого уровня и связана с АЛУ и другими блоками центрального процессора непосредственно и имеет скорость работы соизмеримую со скоростью работы блоков процессора.

Управляющая память входит в состав центрального устройства управления и относится к классу постоянной памяти. Этот вид памяти используется для хранения микропрограмм. Ее отличает очень высокое быстродействие и небольшая емкость, определяющаяся количеством команд в системе команд центрального процессора.

Регистровая память выполнена на триггерных элементах и входит в состав центрального процессора. Емкость ее невысока, скорость высокая, но меньше, чем у управляющей памяти. Основной характеристикой данного типа памяти является разрядность

Арифметико-логическое устройство Общие сведения, функции и классификацияАрифметико-логическое устройство функционально можно разделить на две части :

а) микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

б) операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд).

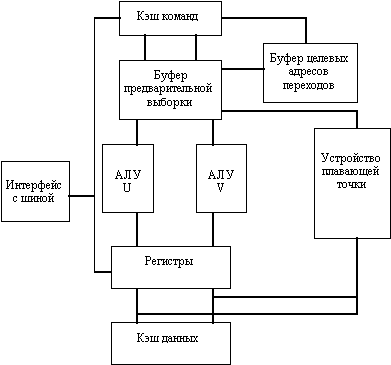

Структурная

схема АЛУ и его

связь с другими

блоками машины

показаны на рисунке 2. В состав

АЛУ входят

регистры Рг1

– Рг7, в которых

обрабатывается

информация

, поступающая

из оперативной

или пассивной

памяти N1, N2,

...NS; логические схемы, реализующие

обработку слов

по микрокомандам,

поступающим

из устройства

управления.

Закон переработки информации задает микропрограмма М, которая записывается в виде последовательности микрокоманд A1,A2, ..., Аn-1,An. При этом различают два вида микрокоманд: внешние, то есть такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нем те или иные преобразования информации (на рис. 2 микрокоманды A1,A2,..., Аn), и внутренние, которые генерируются в АЛУ и воздействуют на микропрограммное устройство, изменяя естественный порядок следования микрокоманд. Например, АЛУ может генерировать признаки в зависимости от результата вычислений j,w,Q и др. (j – признак переполнения, w – признак отрицательного числа, Q – признак равенства 0 всех разрядов числа), На рис. 2 эти микрокоманды обозначены р1, p2,..., рm.

Результаты вычислений из АЛУ передаются по кодовым шинам записи у1, у2, ...,уs, в ОЗУ.

Функции регистров, входящих в АЛУ:

Рг1 – сумматор (или сумматоры) – основной регистр АЛУ, в котором образуется результат вычислений;

Рг4 – адресный регистр (или адресные регистры), предназначен для запоминания (иногда и формирования) адреса операндов и результата;

Ргб – k индексных регистров, содержимое которых используется для формирования адресов;

Рг7 – l вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Часть операционных регистров является программно-доступной, то есть они могут быть адресованы в команде для выполнения операций с их содержимым. К ним относятся :

сумматор,

индексные регистры,

некоторые вспомогательные регистры.

остальные регистры программно-недоступные, так как они не могут быть адресованы в программе . Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу обработки информации и логической структуре. Подробная классификация АЛУ показана на рис. 3.

Сложность логической структуры АЛУ в определенной степени можно охарактеризовать количеством отличающихся друг от друга микроопераций, необходимых для выполнения всего комплекса задач, поставленных перед АЛУ. На входе каждого регистра собраны соответствующие логические схемы, обеспечивающие такие связи между регистрами, что позволяют реализовать заданный набор микроопераций.

Выполнение операций над словами сводится к выполнению последовательности микрокоманд, которые управляют передачей слов в АЛУ и действиями по преобразованию слов. Порядок выполнения микрокоманд определяется алгоритмом выполнения операций. Следовательно, связи между регистрами АЛУ и функции, которые должны выполнять регистры, зависят в основном от принятой методики выполнения операций : арифметических, логических и специальной арифметики.

Перечень операций, выполняемых в АЛУ, зависит от назначения цифровой вычислительной машины и от функций, выполняемых АЛУ при обеспечении работы остальных устройств машины. При представлении операций в виде последовательностей микроопераций АЛУ должно состоять из элементов; реализующих эти микрооперации.

Таким образом, структура АЛУ определяется набором микроопераций, необходимых для выполнения заданных арифметических, логических и специальных операций , а задачу построения АЛУ можно свести к задаче определения набора микроопераций, который позволяет составить микропрограмму любой из заданных операций. Такой набор легко получить. если записать микропрограммы всех операций, выполняемых в АЛУ, и выбрать из них все микрооперации, входящие в микропрограммы хотя бы один раз. Однако, если при этом алгоритм операций выбирать произвольно, то количество микроопераций, входящих в полный набор, может оказаться слишком большим и, следовательно, АЛУ будет сложным.

Для получения более простой схемы АЛУ алгоритмы арифметических и логических операций следует выбирать из условия получения минимального набора микроопераций. При этом необходимо учитывать требование обеспечения заданного быстродействия АЛУ: слишком ограниченный набор микроопераций может привести к “длинным микропрограммам некоторых операций”, что увеличивает время выполнения данных операций.

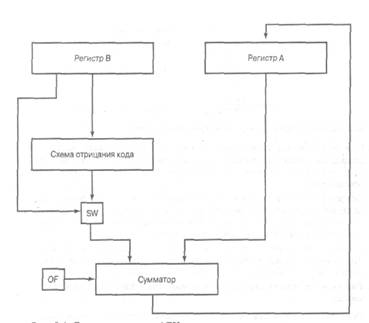

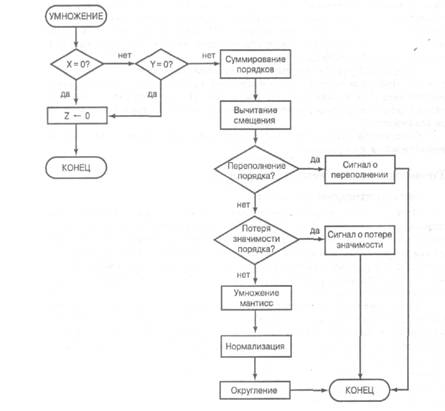

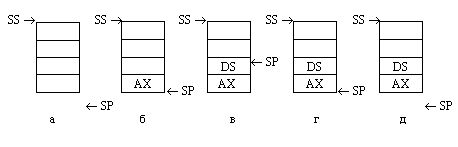

Алгоритмы сложения (вычитания) и умножения в АЛУСтруктурная схема микропрограммы сложения показана на рис. 4. Выполнение этого алгоритма состоит в следующем:

Первое слагаемое а устанавливается на Рг1, анализируется его знак: если знак отрицательный, то операнд инвертируется и передается на Рг3, если положительный - передается без инверсии через Рг2 на Рг3

Второе слагаемое также устанавливается на Рг1 и анализируется его знак: если знак отрицательный, то операнд инвертируется, если положительный - сразу начинается суммирование операндов на Рг2 ( сумматоре )

После суммирования анализируется знак результата: если результат отрицательный, то он инвертируется, если положительный - добавляется “+1” ЦП к младшему разряду результата и выполняется анализ признаков переполнения

Для того, чтобы структурная схема, показанная на рис. 4 могла выполнять операцию вычитания, достаточно перед выполнением операции проинвертировать знак второго слагаемого.

В начале операции все регистры устанавливаются в нулевое состояние.

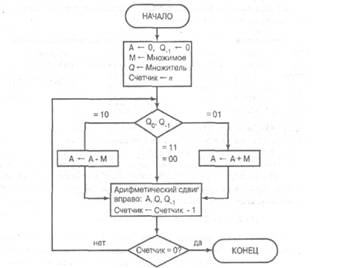

Множимое и множитель располагаются в определенных регистрах, предусматриваются также регистры, в которых образуется сумма частичных произведений.

Анализируется младший разряд множителя: если он имеет значение “1”, то к сумме частичных произведений прибавляется множимое.

Действия 3 и 4 повторяются n раз ( n - разрядность сомножителей )

Структурная схема микропрограммы умножения показана на рис. 6. Ввиду громоздкости деление здесь не рассматривается.

Теперь, можно приступать к рассмотрению конкретного АЛУ, что и будет сделано. В качестве примера возьмем АЛУ цифрового сигнального процессора - специализированного процессора с RISC архитектурой, предназначенного для решения задач цифровой обработки сигналов. Трудно найти такую область техники, где не могли бы применяться сигнальные процессоры. Это цифровая фильтрация, кодирование и декодирование информации, обработка звука и распознавание речи, обработка изображений, медицина, измерительная техника, управляющие системы и многое другое.

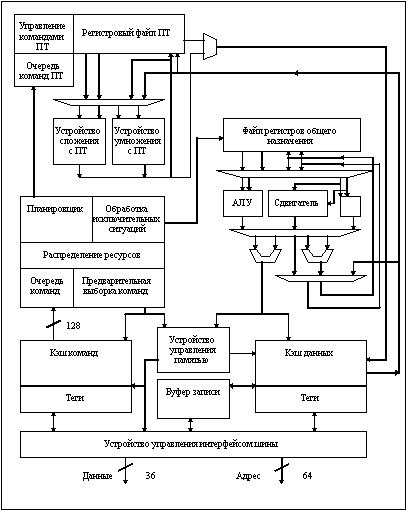

Цифровые сигнальные процессорыЧем же отличается цифровой процессор от обычного микропроцессора ? В первую очередь - архитектурой и системой команд. В основу построения DSP (Digital Signal Processor) положены следующие принципы :

использование гарвардской архитектуры

сокращение длительности командного цикла

применение конвейеризации

применение аппаратного умножителя

включение в систему команд специальных команд цифровой обработки сигнала

Гарвардская архитектура подразумевает хранение программ и данных в двух раздельных запоминающих устройствах. Соответственно на кристалле имеются раздельные шины адреса и данных ( в некоторых типах процессоров - несколько шин данных и адреса ). Это позволяет совмещать во времени выборку и исполнение команд

Конвейерный режим используется для сокращения командного цикла. Обычно применяется двух- или трехкаскадный конвейер, что позволяет на различных стадиях выполнения одновременно обрабатывать две или три инструкции.

Аппаратный умножитель применяется для сокращения времени выполнения одной из основных операций цифровой обработки сигнала - умножения. В процессорах общего назначения эта операция используется за несколько тактов сдвига и сложения ( см. рис.5 ) и занимает много времени, а в DSP благодаря специализированному умножителю - один цикл.

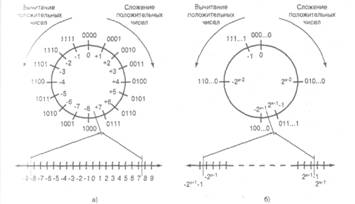

Алгоритм выполнения сложения и деления в арифметико-логическом устройстве, на примере цифрового сигнального процессора семейства ADSP-21xx.Все устройства в процессорах этого семейства 16-и битные с фиксированной точкой. Почти все операции подразумевают представление знаковых чисел в форме дополнения до двух. Остальные же используют беззнаковые числа или просто строки битов. Специальная поддержка имеется для многословных вычислений и блочной плавающей арифметики.

Арифметика и типы данных Строки битовЭто простейшая форма записи; 16 бит составляют строку битов. Примерами операций, в которых используется этот формат, являются логические операции NOT,AND,OR,XOR. Эти операции, исполняемые АЛУ, считают, что их аргументы строки битов и не заботятся о знаке или о положении десятичной точки

Числа без знакаБеззнаковые двоичные числа могут принимать только положительные значения и потому имеют почти вдвое больший диапазон, чем знаковые числа той же длины. Младшие слова чисел с увеличенной точностью используются как беззнаковые числа.

Числа со знаком в форме дополнения до двухДля арифметики процессоров семейства термин “знаковый” всегда обозначает числа. Записанные в форме дополнения до двух. Многие инструкции процессора подразумевают или поддерживают арифметику по модулю 2.

Дробь 1.15Арифметические инструкции процессоров семейства оптимизированы для операций в дробном двоичном формате 1.15. В этом формате левый бит числа обозначает его знак, и 15 оставшихся бит представляют собой числа от -1 до почти 1 ( из-за несимметричности представления знаковых чисел ).

Арифметические операции АЛУВсе арифметико-логические операции трактуют свои операнды и получают результаты как 16 разрядные битовые строки, за исключением примитивов знакового деления (DIVS). Различные флаги трактуют результаты как числа со знаком: флаг переполнения (AV) и флаг отрицательного числа (AN).

Логика флага переполнения основана на арифметике по модулю 2. Он устанавливается если знаковый бит изменялся непредсказуемым образом. Например при сложении двух положительных чисел, результат также должен быть положителен. Если же происходит переполнение ( перенос в знаковый бит, устанавливающий его в единицу, так что результат получается отрицательным ), то устанавливается бит AV.

Логика флага переноса основана на беззнаковой арифметике. Этот флаг устанавливается в том случае, если генерируется перенос из старшего разряда числа, который не может быть записан в результат. Этот флаг очень полезен при операциях с многословными представлениями чисел для младших слов.

Арифметика МАСРезультаты умножения представляют собой битовые строки. Операнды же обрабатываются так, как это указано в самой инструкции ( умножение знаковых, умножение беззнаковых, умножение знакового на беззнаковое или операция округления ). 32-битный результат из умножителя считается знаковым, так как происходит знаковое расширение на все 40 бит наборов регистра умножителя ( MR ).

Все процессоры семейства поддерживают два формата коррекции результата умножения :

дробный (1.15 )

целый ( также называется 16.0 )

Когда процессор умножает два 1.15 операнда, результат является числом в формате 2.30 ( два знаковых бита и 30 дробных бит ). В дробном режиме МАС автоматически сдвигает результат умножения влево на один бит перед переносом его в регистр результата ( MR ). После этого сдвига формат результата становится 1.31, что позволяет округлить его до формата 1.15.

В целочисленном режиме сдвиг влево не происходит. Например, если операнды формата 16.0, то 32-битный результат умножения будет в формате 32.0. Более того здесь сдвиг не нужен, ибо он изменит значение результата.

Арифметика устройства сдвигаМногие сдвиговые операции созданы специально для знаковых или беззнаковых чисел: логические сдвиги предполагают беззнаковые операнды, тогда как арифметические сдвиги предполагают знаковые операнды.

Экспоненциальная логика предполагает знаковые операнды и поддерживает блочную плавающую точку, которая тоже базируется на формате дополнения до двух.

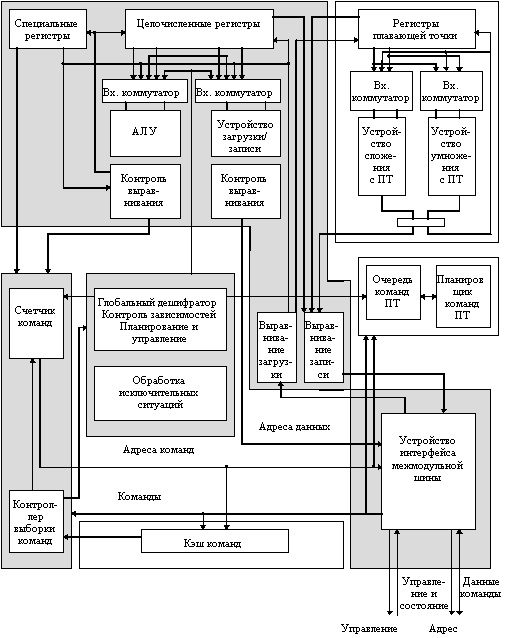

АЛУАрифметико-логическое устройство обеспечивает стандартный набор арифметических и логических операций. Также имеется два примитива деления, которые позволяют реализовывать многоцикловое деление.

Структура АЛУНа рисунке 7 показана блок-схема АЛУ.

АЛУ имеет три 16-битных регистра, доступных для программиста : X,Y -регистры операндов, а R - регистр результата. АЛУ использует входной сигнал переноса ( CI ), который означает бит переноса в регистре арифметического состояния ( ASTAT ). АЛУ генерирует шесть статусных сигналов :

результат 0 ( AZ )

отрицательный ( AN )

перенос ( AC )

переполнение результата ( AV )

знак (AS )

состояние частного ( AQ )

В конце цикла все сигналы арифметического статуса изменяют состояния соответствующих битов в регистре арифметического статуса ( ASTAT ).

Входной порт X может принимать данные из двух источников : из блока регистров АХ или с шины результата. Шина результатов ( R ) соединяет выходные регистры всех вычислительных устройств, позволяя им быть непосредственно операндами инструкций. Блок регистров АХ состоит из двух регистров : АХ0 и АХ1. Эти регистры читаемы и могут быть записаны через шину DMD. Выход блока регистров АХ таков, что один из них может

обеспечивать операнд для АЛУ, в то время, как другой может записываться в память через шину DMD.

Входной порт Y также может принимать данные из двух источников : из набора регистров АY или из регистра обратной связи AF. Блок регистров AY состоит из двух регистров AY0 и AY1. Эти регистры читаемы и могут быть записаны через шину DMD, а также могут быть записаны через шину PMD. Выход блока регистров AY совпадает по своим возможностям с блоком регистров АХ.

Результат работы АЛУ загружается либо в регистр обратной связи AF, либо в регистр результата AR. Регистр обратной связи - внутренний регистр АЛУ, который позволяет использовать результат непосредственно, как операнд Y. Регистр результата AR может записываться как на шину DMD, так и на шину результатов. Он также непосредственно загружаем с шины DMD.

Набор инструкций позволяет осуществить чтение этих регистров с шины PMD, но при этом нужно использовать устройство обмена между DMD-PMD шинами.

Любые регистры, связанные с АЛУ могут как читаться, так и писаться в одном цикле. Регистры читаются в начале цикла и записываются в конце. Новое значение, записанное в регистр, не может быть считано до начала следующего цикла.

АЛУ содержит два набора регистров AR, AF, АХО, АХ1, AYО, AY1. В каждый момент времени домен лишь один набор. Дополнительный набор регистров может быть сделан активным (например, при обработке прерывания) для очень быстрого переключения контекстов. Новая задача, такая, как обработка прерывания, может быть выполнена без запоминания текущего состояния регистров АЛУ.

Выбор первичного или вторичного набора регистров контролируется битом 0 в регистре режима и статуса процессора (MSTAT). Если этот бит нулевой, используется первичный набор, если же он единица, то используется вторичный набор регистров.

Стандартные функцииВот список стандартных функций АЛУ:

| R=X+Y | сложение Х и Y |

| R=X+Y+Cl | сложение Х и Y с переносом |

| R=X – Y | вычесть Y из Х |

| R=X – Y – Cl – 1 | вычесть Y из Х с заемом |

| R=Y – Х | вычесть Х из Y |

| К=Y – X – Cl – 1 | вычесть Х из Y с заемом |

| R= – X | арифметическое отрицание Х |

| R= – Y | арифметическое отрицание Y |

| R=Y+1 | инкремент Y |

| R=Y – 1 | декремент Y |

| R=PASS Х | результат равен операнду Х |

| R=PASS Y | результат равен операнду Y |

| R=O (PASS 0) | очистить результат |

| R=ABS Х | результат равен абсолютному значению Х |

| R=X AND Y | логическое и (AND) Х и Y |

| R=X OR У | логическое или (OR) Х и У |

| R=X XOR У | исключающее логическое или (XOR) Х и У |

| R=NOT Х | логическое отрицание Х |

| R=NOT Y | логическое отрицание У |

Для обработки чисел с повышенной точностью предусмотрен сигнал переноса и флаг переноса (AC). Операция сложения с переносом (+Cl) предназначена для сложения "верхних" частей чисел с повышенной точностью. Вычитание с заемом (+CI-1) предназначено для вычитания "верхних" частей чисел с повышенной четностью.

Режим “насыщения” и “защелки”Регистр AR имеет режим работы когда он автоматически устанавливается в максимальное положительное или максимальное отрицательное число при возникновении переполнения Этот режим включается установкой бита 3 в регистре режима и статуса процессора (MSTAT) . При включенном режиме насыщения, значение, получаемое в АR, зависит от флагов переноса и переполнения, сгенерированных АЛУ в текущем цикле. Ниже приведена таблица, показывающая содержимое AR в зависимости от флагов при включенном режиме насыщения.

Реализация режима насыщения существенно отличается от таковой в МАС-е, где режим насыщения указывается в самой инструкции.

Регистр АF не подчиняется режиму насыщения, поэтому если результатом операции, является регистр АF, произойдет циклический переход, но флаги отразят тот факт, что результат был насыщен.

Режим "защелки" переполнения АLU, разрешаемый битом 2 в регистре режима и статуса процессора (MSTAT), приводит к тому, что флаг переполнения АV остается поднятым после переполнения, несмотря на то, что последующие инструкции могут не генерировать переполнения. В этом режиме флаг АV может быть очищен только прямой записью нуля через шину DMD.

ДелениеФункция деления реализуется дополнительной сдвиговой логикой, не показанной на рисунке 7. Деление достигается с помощью двух примитивов деления. Они используются для получения невосстанавливаемого условного алгоритма делением, использующего сложения и вычитания. Деление может быть знаковым и беззнаковым; однако, делитель и делимое должны быть одинакового типа.

Деление с одинарной точностью, с 32-битным делимым и 16-битным делителем, дающее 16-битное частное, выполняется за 16 циклов. Также могут быть вычислены частные меньшей и большей разрядности. Делитель может содержаться в АХ0, АХ1 или любом из R регистров. Старшая часть знакового делимого может содержаться в АY1 или AF. Старшая часть беззнакового делимого может содержаться только в AF. Младшая часть делимого должна быть в АY0. После завершения операции деления частное находится в AY0.

Первый из двух примитивов деления, "делить знак" (DIVS), выполняется в начале деления при делении знаковых чисел. Эта инструкция получает знаковый бит делимого, проведя операцию “исключающее или” со знаками делимого и делителя. Регистр AY0 сдвигается на 1 разряд, так что вычисленный знаковый бит помещается в самый младший (правый) разряд. Полученный знаковый бит также загружается во флаг АQ регистра арифметических флагов. Самый старший (левый) бит AYO сдвигается в младший бит AF, а оставшиеся старшие 15 бит AF загружаются из 15 младших бит регистра R из АЛУ, что в свою очередь пересылает содержимое входного регистра Y прямо в регистр результата R. Последовательный эффект состоит в том, чтобы сдвинуть влево пару регистров AF-AYO и переслать знак частного в самый младший разряд. Рисунок 8 иллюстрирует операцию DIVS.

При делении

беззнаковых

чисел инструкция

DIVS не используется. Вместо этого

флаг АQ в регистре

арифметического

состояния

должен быть вручную очищен.

Этот бит сигнализирует

последующим

операциям о

том, что частное

должно быть

положительным.

Второй примитив деления – инструкция "делить частное" (DIVQ), которая генерирует 1 бит частного за цикл и выполняется повторно, чтобы подсчитать оставшиеся разряды частного. Для беззнакового деления с одинарной точностью инструкция DIVQ выполняется 16 раз, чтобы получить 16 бит частного. Для знакового деления с одинарной точностью инструкция DI VQ выполняется 15 раз, после вычисления знакового бита инструкцией DI VS. Инструкция сдвигает регистр AYO влево на 1 бит так, что новый бит частного помещается в младший бит. Состояние флага АQ (полученное во время предыдущих операций) определяет инструкцию, используемую для получения частичного остатка. Если AQ=1, то АЛУ добавляет делитель к частичному остатку в AF. Если AQ=O, то АЛУ вычитает делитель из частичного остатка в AF. Регистр результата К загружается со смещением в AF так, как это описано для инструкции DIVS. Флаг AQ считается как исключающее логическое или (XOR) старшего бита делителя и старшего бита регистра результата АЛУ, а очередной бит частного получается инвертированием этого значения. Полученный бит частного загружается в младший бит регистра АYО, который затем сдвигается влево на 1 бит. Рисунок 9 иллюстрирует операцию DlVQ.

Формат частного для любого представления может быть определен из формата делимого и делителя. Пусть NL равно количеству бит слева от десятичной точки, NR равно количеству бит справа от десятичной точки делимого; DL равно количеству бит слева от десятичной точки, DR равно количеству бит справа от десятичной точки делителя; тогда количество бит

слева от

десятичной

точки частного

есть NL–DL+l ,a количество

бит справа от

десятичной

точки частного

есть NR–DR–1.

Некоторые изменения формата должны использоваться чтобы гарантировать правильность частного. Например, если оба операнда знаковые и полностью дробные (делимое в формате 1.31 и делитель в формате 1.15), результат полностью дробный (в формате 1.15) и поэтому делимое должно быть меньше делителя для получения верного результата.

Чтобы разделить 2 целых (делимое в формате 32.0 и делитель в формате 16.0) и получить целый результат (в формате 16.0),надо сдвинуть делимое на 1 бит влево (получить формат 1.31) перед делением.

Переполнение алгоритма случается в том случае, если частное не может быть представлено в формате частного или если делитель равен нулю или меньше допустимого.

МАС (умножитель/аккумулятор)МАС обеспечивает высокоскоростное умножение, умножение с накоплением данных (разности), насыщение и очистку результата. Обратная связь позволяет части результата MAC использоваться в качестве одного из множимых в следующем цикле.

Блок-схема МАСРисунок 10 показывает блок-схему МАС. Умножитель имеет два входных 16-битных порта – Х и У и один 32-битный выходной порт результата Р. 32-битное произведение передается 40-битному сумматору, который прибавляет или вычитает текущий результат к регистру результата (MR) или непосредственно помещает текущий результат в регистр MR. Ширина регистра MR составляет 40 бит. Фактически он состоит из трех регистров: MRО и MR1, 16-битных, и 8-ми битного MR2.

Сумматор имеет

ширину, большую

чем 32 бита для

того, чтобы разрешить

промежуточные

переполнения

при выполнении

нескольких операций подряд.

Флаг МV (multiplier overflow,

переполнение

умножителя) устанавливается,

если значащие

биты появились

выше 32-битной

границы регистра

МR.

Входные/выходные регистры МАС, а также запись/чтение в них, аналогичны таковым для АЛУ.

Результат работы сумматора загружается либо в регистр обратной связи МF, либо в регистр результата MR. Регистр обратной связи MF позволяет использовать биты 16-31 результата непосредственно, как операнд Y в следующем цикле. Регистр результата (MR) шириной 40 бит состоит из трех регистров: MR0,MR1 и MR2. Каждый из этих регистров может быть напрямую загружен через шину DMD и записан через шину DMD или на шину промежуточных результатов R.

MАС, аналогично АLU, содержит второй банк регистров, как показано на рисунке 4.6, за первичными регистрами. Выбор первичного или вторичного набора регистров контролируется битом 0 в регистре режима и статуса процессора (MSTAT).

Операции МАССписок выполняемых МАС-ом операций :

Х*Y MR+X*Y MR–X*Y 0 | умножить Х на Y умножить Х на Y и добавить результат к содержимому MR умножить Х на Y и вычесть результат из содержимого MR очистить регистр результата MR |

МАС обеспечивает два стандартных режима умножения/аккумулирования: дробный режим (для чисел в формате 1.15) и целый режим для целых в формате 16.0.

В дробном режиме формат 32-битного выходного регистра регулируется, то есть, происходит знаковое расширение и сдвиг содержимого на 1 бит влево перед добавлением в MR. Например, 31-ый бит регистра Р соответствует 32-му биту регистра MR (что в свою очередь соответствует биту 0 регистра MR2), a нулевой бит регистра Р соответствует 1-му биту регистра MR (что в свою очередь соответствует биту 1 регистра MRO). Младший бит MR просто очищается. Оставшиеся семь бит MR2 заполняются знаком регистра Р (то есть 31 битом Р).

В целом режиме 32-битный регистр результата не сдвигается при добавлении к регистру MR. Восемь бит MR2 заполняются знаком Р.

Режим выбирается 4-ым битом регистра режима и состояния (MSTAT). Единица в этом бите означает целочисленный режим; ноль означает дробный режим. В обоих режимах содержимое регистра Р подается на вход сумматора, который прибавляет или вычитает новое произведение из текущего содержимого регистра MR, чтобы сформировать окончательный результат в R.

Для реализации вычислений с повышенной точностью, умножитель позволяет осуществлять любые комбинации операндов Х и Y (умножать знаковое на знаковое (SS),беззнаковое на знаковое (US), беззнаковое на беззнаковое (UU), знаковое на беззнаковое (SU) ).

Форматы операндов записываются как часть инструкции. Поэтому они динамически выбираются из каждой инструкции умножения.

8-битный регистр MR2 при записи/чтении располагается в восьми младших битах шин данных. При чтении MR2 через шину DMD или на шину промежуточных результатов (R) происходит его знаковое расширение до 16 бит. MR1 также имеет возможность автоматического расширения знака. Тогда MR1 загружается с шины DMD, все биты в MR2 автоматически заполняются знаковым битом МR1, так что MR2 служит расширением MR1. Чубы загрузить в регистр МR2 значение, отличное от знакового расширения MR1, надо загружать MR2 после загрузки МR1. Загрузка же MR0 не влияет ни на один из оставшихся регистров; знаковое расширение не происходит при загрузке MR0.

Переполнение, насыщение и окружение в МAССумматор генерирует флаг переполнения МV, который загружается в регистр арифметического статуса процессора (АSТАТ) после выполнения каждой операции MАС-ом. Этот бит устанавливается в случае, если результат аккумулятора, интерпретируемый как число с дополнением до 2, (MR) пересекает 32-битную границу (МR1/МR2) .То есть флаг МV устанавливается, если верхние девять бит MR не все одновременно равны 0 или 1.

Регистр МR имеет возможность выполнять операцию насыщения, то есть устанавливаться в максимальное положительное (отрицательное) число при переполнении. Операция насыщения зависит от флага МV в регистре ASTAT и знакового бита регистра MR2. Следующая таблица показывает эффект операции насыщения МR

| Флаг MV | Старший бит МR2 | Результат после насыщения |

| 0 | 1 или 0 | без изменения |

| 1 | 0 | 00000000 0111111111111111 1111111111111111 -максимальное положительное число |

| 1 | 1 | 11111111 1000000000000000 0000000000000000 - максимальное отрицательное число |

Насыщение в МАС – это операция (в отличии от режима в АЛУ). Она предполагается для использования после умножений/аккумуляций, так чтобы предварительные результаты не вызывали насыщения, ибо это приведет к потере точности.

Переполнение выше 40-го бита регистра MR2 не должно допускаться. Знак числа теряется безвозвратно при этом и насыщение может получить совершенно противоположный результат. Но требуется более 255 простых переполнений (типа MV), чтобы такое могло случиться.

Аккумулятор имеет возможность округлить 40-битный результат R до 16-битного. Округление должно быть указано в инструкции с помощью опции (RND). Округленный результат направляется в регистр MR или MF. Когда происходит округление с регистром MR в качестве выходного, содержимое MRl представляет из себя округленный 16-битный результат, а содержимое регистров MR2 и MR1 может рассматриваться как результат, округленный до 24 бит.

Аккумулятор использует несмещенную схему округления. Обычный метод смещенного округления производится добавлением числа 0х8000 к MR (то есть если MR0 больше или равно 0х8000, то MR1/MR2 инкрементируются), при этом округленный результат находится в MR2 и MR1. Но этот метод приводит к общему положительному смещению, т.к. при среднем значении (когда регистр MRO равен 0x8000) число округляется вверх. Аккумулятор же устраняет это смещение, всегда устанавливая бит 0 MR1 в ноль после округления, если МR0 содержит 0х8000. Таким образом, происходит округление четных значений MR1 вниз и нечетных значений MR1 вверх, что в свою очередь приводит к равнозначности операции округления на больших выборках чисел.

Пример типичной операции округления:

| Пример 1 | MR2 | MR1 | MR0 |

| Неокругленные данные | xxxxxxxx | xxxxxxxx00100110 | 1xxxxxxxxxxxxxxx |

| Бит 15=1 Добавим 1 к 15-му биту и учтем перенос | 1 ( 0х8000) | ||

| Округленное значение | xxxxxxxx | xxxxxxxx00100111 | 0xxxxxxxxxxxxxxx |

Компенсация становится видимой, если MRO=0x8000.

| Пример 2 | MR2 | MR1 | MR0 |

| Неокругленные данные | xxxxxxxx | xxxxxxxx00100110 | 100000000000000 |

| Бит 15=1 Добавим 1 к 15-му биту и учтем перенос | 1 ( 0х8000) | ||

| Так как бит 16 =1, присвоим ему 0 | |||

| Округленное значение | xxxxxxxx | xxxxxxxx00100111 | 000000000000000 |

Закончив рассмотрение АЛУ DSP, попробуем сравнить его производительность по арифметическим операциям, например, с i486DX - достаточно мощным универсальным процессором. Начнем с того, что в АЛУ цифрового сигнального процессора любая инструкция исполняется за один цикл, вместо нескольких циклов во втором процессоре. Работает такой процессор на частоте до 33.3 Мгц ( при этом i486DX работает на частоте 50 Мгц, а улучшенные версии на частотах до 133 Мгц ). Операции с плавающей точкой имеют 40 разрядные операнды, вместо 80 разрядных в FPU i486DX. Остальные параметры ( конвейеризация, архитектурные решения ) практически идентичны. Для примера ниже дана таблица, отображающая время исполнения программы “быстрого преобразования Фурье” на 1024 точки для процессоров i486DX2-66 и ADSP-21xx

| Операция | Время выполнения | ||

| i486DX2-66 | ADSP-21xx | ||

| БПФ на 1024 точки | 20 ms | 2.23 ms | |

Получаются довольно странные результаты. У более мощного процессора время выполнения в 10 раз больше, чем у менее мощного. Из-за чего так происходит ? Прежде всего надо отметить, что аппаратно реализованное умножение в DSP дает основной выигрыш в скорости. Во-вторых, DSP менее универсален, по сравнению с i486, поэтому арифметические операции у него оптимизированы для работы в реальном времени, то есть скорость их выше. Конечно скорость достаточно сильно зависит от алгоритмов умножения, деления и сложения. Ведь какой бы ни была скорость процессора плохо оптимизированный алгоритм будет приводит к лишним схемным решениям, потере времени на выполнение лишних микрокоманд и, как следствие, ухудшение параметров процессора. В некоторых процессорах ( уже практически отсутствующих на рынке, например i8080 или его преемник Zilog Z80 ) команд умножения и деления нет. В этом случае данные арифметические операции реализовывались программно, через сложение и сдвиги. Соответственно производительность при вычислениях падала в несколько раз.

На сегодняшний день производительность процессоров при выполнении арифметических операций является довольно значительным параметром. Сегодняшний компьютер невозможно представить без средств мультимедиа , а мультимедиа - это огромные объемы оцифрованной графики и звука, причем сжимаемые и разжимаемые в реальном времени ( форматы MPEG, GSM ). Конечно многие из обязанностей центрального процессора берут на себя контроллеры ввода-вывода ( звуковая и видеокарты ), но чаще всего в них нет встроенной поддержки кодирования и декодирования информации. Еще пример: сейчас используются базы данных с максимальным размером около 4 Тб. Соответственно, такие объемы информации требуют значительных вычислительных возможностей для ускорения поиска и обращения к записям.

Таким образом получается, что тщательно продуманные реализации алгоритмов арифметических операций и схемных решений ведут к увеличению быстродействия центрального процессора и, как следствие, получению более широких возможностей работы с информацией.

Список литературы

Справочник по цифровой вычислительной технике ( процессоры и память ), ”Технiка”,1979

Цифровые сигнальные процессоры, “Микроарт“, 1996

Григорьев “Микропроцессор i486“,1993

СD-ROM “Intel на Comtek’98” ( образ российского веб-сайта Intel )

CD-ROM “Intel Architecture Information Library”

Лекции по курсу “Вычислительные машины и сети”

Введение 3

Типы микропроцессоров 4

Обобщенная структурная схема персонального компьютера 4

Арифметико-логическое устройство 6

Общие сведения, функции и классификация 6

Алгоритмы сложения (вычитания) и умножения в АЛУ 10

Цифровые сигнальные процессоры 13

Алгоритм выполнения сложения и деления в арифметико-логическом устройстве, на примере цифрового сигнального процессора семейства ADSP-21xx. 13

Арифметика и типы данных 13

Строки битов 13

Числа без знака 14

Числа со знаком в форме дополнения до двух 14

Дробь 1.15 14

Арифметические операции АЛУ 14

Арифметика МАС 14

Арифметика устройства сдвига 15

АЛУ 15

Структура АЛУ 15

Стандартные функции 18

Режим “насыщения” и “защелки” 19

Деление 19

МАС (умножитель/аккумулятор) 22

Блок-схема МАС 23

Операции МАС 24

Переполнение, насыщение и окружение в МAС 25

Сравнительный анализ выполнения арифметических команд в различных типах процессоров 27

Список литературы 29

Похожие работы

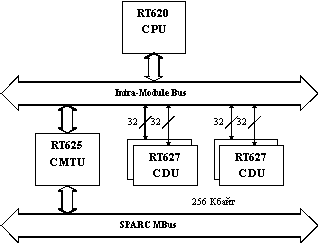

... версия этого микропроцессора. Как и его предшественник, новый кристалл Alpha 21066A помимо интерфейса PCI содержит на кристалле интегрированный контроллер памяти и графический акселератор. Эти характеристики позволяют значительно снизить стоимость реализации систем, базирующихся на Alpha 21066A, и обеспечивают простой и дешевый доступ к внешней памяти и периферийным устройствам. Alpha 21066A ...

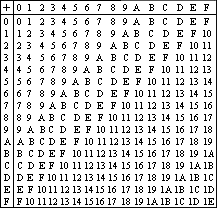

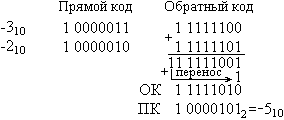

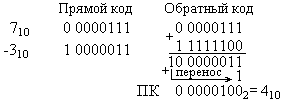

... вычитания. Представление чисел в формате с плавающей точкой В формате с фиксированной точкой, в частности в дополнительном коде, можно представлять положительные и отрицательные числа в диапазоне, симметричном на числовой оси относительно точки 0. Расположив воображаемую разделяющую точку в середине разрядной сетки, можно в этом формате представлять не только целые, но и смешанные числа, а ...

... , связанный с формированием представлений о системно-информационном подходе к анализу окружающего мира, о роли информации в управлении, специфике самоуправляемых систем, общей закономерности информационных процессов в системах различной природы. Основой мировоззрения, главным его компонентом является научная картина мира, рассматриваемая как высший уровень систематизации и обобщения научных ...

... исключающего ИЛИ двух операндов. Результат операции помещается в первый операнд. Эту операцию удобно использовать для инвертирования или сравнения определенных битов операндов.2. Структура и выполнение EXE-файла. EXE-модуль, созданный компоновщиком, состоит из следующих двух частей: 1) заголовок - запись, содержащая информацию по управлению и настройке программы и 2) собственно загрузочный ...

0 комментариев