Навигация

Присвоение знака результату

5. Присвоение знака результату.

Первые три операции могут выполняться одновременно, так как они независимы. Наличие операции определения знака произведения предполагает, что умножение мантисс выполняется в прямом коде.

При выполнении операции умножения в машине с плавающей запятой может получиться переполнение отрицательного порядка, которое будет интерпретировано как машинный нуль, если программой пользователя игнорируется признак исчезновения порядка. Может также возникнуть положительное переполнение порядка. В этом случае в первую очередь необходимо нормализовать мантиссу результата. Если и после этого переполнение порядка не устраняется, то машиной формируется признак переполнения порядка.

3. Методы ускорения операции умножения

Любое ускорение операции умножения даже ценой усложнения арифметических и логических схем позволяет существенно повысить производительность ЭВМ, т.к. примерно 70% машинного времени затрачивается на выполнение этой операции.

Известны способы ускорения умножения, направленные на сокращение общего количества и времени выполнения операций сложения, необходимых для образования произведения. Эти способы делятся на логические и аппаратные.

Под аппаратными понимают такие способы, которые требуют для своей реализации введения дополнительного оборудования в основные арифметические цепи, благодаря чему достигается совмещение во времени отдельных составных частей процесса умножения. Они подразделяются на способы 1-го и 2-го порядков. Для реализации способов 1-го порядка необходимо количество оборудования, пропорциональное числу разрядов машинного слова n. Для реализации способов 2-го порядка требуется объем оборудования, пропорциональный n2.

Под логическими понимают такие способы ускорения, при реализации которых сохраняется основная структура арифметических цепей умножителя, а ускорение достигается только за счет усложнения схемы управления.

Простейшим логическим способом является пропуск тактов суммирования в тех случаях, когда очередная цифра множителя равна 0.

В среднем, количество сложений при этом сокращается вдвое.

Можно сократить и среднее и максимальное количество суммирований при использовании как прямых, так и инверсных передач множимого в сумматор. Здесь учитывается то обстоятельство, что время умножения значительно сокращается, если при наличии в разрядах множителя нескольких нулей подряд производить его сдвиг сразу на несколько разрядов. Для этого видоизменяют код множителя с целью представления его с меньшим количеством разрядов, содержащих единицу. Например, группу единиц в множителе 011. ..110 можно преобразовать в группу 100...0![]() 0, т.е. перейти к системе с цифрами 1,0,

0, т.е. перейти к системе с цифрами 1,0,![]() .

.

Таким образом, в основе способа лежит представление числа как совокупности следующих последовательностей: нулей, единиц, нулей с изолированными единицами, единиц с изолированными нулями. При этом: два или более соседних нулей или соседних единиц рассматриваются как последовательность. Например, если умножение начинается с младших разрядов и множитель содержит последовательность единиц, то производится вычитание множимого с соответствующим (младшим) весом, а затем сдвиг через все эти единицы.

Сдвиг через последовательность единиц прекращается на первом нуле. Если сразу за этим нулем расположена единица, то множимое вычитается и выполняется сдвиг через последовательность единиц. Если за этим нулем непосредственно следует второй нуль, то множимое прибавляется, а затем выполняется сдвиг через последовательность нулей, который прекращается на первой единице.

Если за этой единицей следует ноль, то множимое прибавляется и производится сдвиг через последовательность нулей. Если за этой единицей непосредственно следует вторая единица, то производится вычитание множимого с соответствующим весом данного разряда, а затем выполняется сдвиг через последовательность единиц. Если в старшем разряде множителя стоит 1, входящая в последовательность единиц, то сдвиг необходимо продолжать до первого нуля после старшего разряда множителя.

Следует отметить, что при умножении со старших разрядов применяются несколько другие правила определения оптимального множителя. И в том и в другом случае в среднем на каждую операцию сложения выполняется сдвиг на 2,9 разряда, если схема рассчитана на сдвиг не более, чем на 6 разрядов одновременно.

В пределе среднее число сложений-вычитаний, приходящееся на один разряд множителя, равно 3-1. Это наилучший результат, которого можно достичь при использовании логических методов.

Таким образом, переход от одной разновидности двоичной системы счисления к другой при преобразовании множителя позволяет получить выигрыш во времени выполнения операции в целом. При этом возникают определенной длины последовательности 0 или 1, что, в конечном счете, приводит к необходимости одновременного анализа нескольких разрядов множителя и сдвига на произвольное число разрядов.

Одновременное умножение на два разряда.

Количество циклов, необходимых для реализации в ЭВМ операции умножения, можно сократить, если в каждом цикле анализировать не один, а два или более разрядов множителя, выполняя после анализа одну передачу множимого в сумматор и сдвиг множителя на соответствующее число, т.е. два или более, разрядов. Для организации ускоренного умножения множитель можно разбить на группы по два разряда и преобразовать его таким образом, чтобы каждая группа содержала не более одной единицы, понимая под последней 1 или ![]() .

.

Для младшей пары разрядов при умножении с младших разрядов возможны следующие комбинации единиц и нулей в разрядах: 00, 01, 10 и 11.

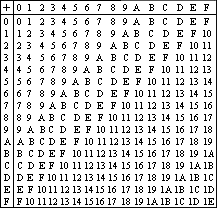

Для первой комбинации не производится ни сложение, ни вычитание, для второй - суммирование множимого, для третьей - суммирование сдвинутого на 1 разряд влево множимого, т.е. умноженного на два, а для четвертой - вместо двух сложений при умножении без ускорения выполняется одно вычитание множимого и одно сложение после сдвига множимого на 2 разряда, т.е. пара разрядов множителя преобразуется к виду 10![]() . Поскольку сложение после сдвига приходится на умножение на следующую пару разрядов, то вместо того, чтобы его выполнять добавляют единицу в следующую за данной пару разрядов. С учетом этого действия при умножении выполняются в соответствии с таблицей 2.

. Поскольку сложение после сдвига приходится на умножение на следующую пару разрядов, то вместо того, чтобы его выполнять добавляют единицу в следующую за данной пару разрядов. С учетом этого действия при умножении выполняются в соответствии с таблицей 2.

Описанная процедура повторяется для всех пар разрядов множителя, а также для одной пары разрядов левее запятой, т.к. может оказаться необходимым добавить к ней (к ее нулям) единицу.

Таблица 2

| Анализируемая пара разрядов | Перенос из предыдущей пары разрядов | Преобразованная пара разрядов | Примечание |

| 00 | 0 | 00 | |

| 01 | 0 | 01 | |

| 10 | 0 | 10 | Предварительный сдвиг множимого |

| 11 | 0 | 01 | Запоминается 1 для следующей пары разрядов |

| 00 | 1 | 01 | |

| 01 | 1 | 10 | Предварительный сдвиг множимого |

| 10 | 1 | 01 | Запоминается 1 для следующей пары |

| 11 | 1 | 10 | разрядов |

Следует отметить, что в общем случае при умножении на 2 разряда множителя двух знаковых разрядов в сумматоре недостаточно. Здесь возможны случаи при А →1, когда даже во втором знаковом разряде появляется единица переполнения, т.е. будет искажен знак частного произведения. Следовательно, при данном способе умножения сумматор должен иметь три знаковых разряда.

Следует отметить, что объем оборудования АУ при умножении на 2 разряда увеличивается незначительно по сравнению с АУ, работающим без ускорения.

Одновременное умножение на три и более разряда, для реализации которого применим подобный способ ускорения, используется реже, так как при этом увеличивается количество требуемых типов передач. Это приводит к значительному усложнению схем, реализующих умножение.

Похожие работы

... с их использованием, имеют свою устойчивую долю рынка. В данной курсовой работе на примере цифрового сигнального процессора семейства ADSP-21xx производится разбор команд умножения и деления, выполняемых в АЛУ. Обобщенная структурная схема персонального компьютера Центральный процессор в персональных компьютерах представляет собой микропроцессор, то есть построен на одной микросхеме (БИС,СБИС). ...

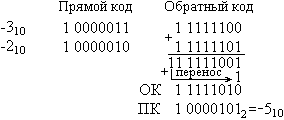

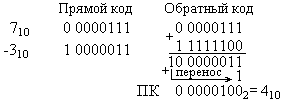

... нельзя рассматривать как единое целое. Кроме того, необходимо кроме сумматора иметь и вычитатель. В результате этого прямой код не применяется для выполнения операции алгебраического сложения, но применяется для выполнения операций умножения и деления. 1.1.3 Дополнительный код В дополнительном коде операция вычитания заменяется операцией алгебраического сложения. При этом знаковый разряд и ...

... позволит технически реализовать четыре действия арифметики в одном устройстве, называемом арифметико-логическом (АЛУ), используя одни и те же электрические схемы. 1.4.1. Представление чисел со знаками При выполнении арифметических операций в ЭВМ применяют прямой, обратный и дополнительный коды. Как уже говорилось выше, кодом называют такую запись числа, которая отличается от естественной и ...

... , связанный с формированием представлений о системно-информационном подходе к анализу окружающего мира, о роли информации в управлении, специфике самоуправляемых систем, общей закономерности информационных процессов в системах различной природы. Основой мировоззрения, главным его компонентом является научная картина мира, рассматриваемая как высший уровень систематизации и обобщения научных ...

0 комментариев