Навигация

Выполнение операций умножения и деления в ЭВМ

СОДЕРЖАНИЕ

Введение

1. Выполнение операции умножения в ЭВМ 2. Умножение чисел, представленных в форме с плавающей запятой 3. Методы ускорения операции умножения4. Матричный метод умножения

5. Выполнение операции деления в ЭВМ 5.1 Деление чисел с восстановлением остатков 5.2 Деление без восстановления остатков 6. Способы ускоренного деления 7. Деление чисел в машинах с плавающей запятойВыводы

Литература

Введение

Тема реферата «Выполнение операций умножения и деления в ЭВМ».

Цель работы – ознакомится с выполнением операций умножения и деления в ЭВМ, как с фиксированной, так и с плавающей запятой.1. Выполнение операции умножения в ЭВМ

Операция умножения является наиболее частой после сложения. Умножение может выполняться суммированием сдвинутых на один или несколько разрядов частичных произведений, каждое из которых является результатом умножения множимого на соответствующий разряд (разряды) множителя.

При точном умножении двух чисел количество значащих цифр произведения может в пределе достичь двойного количества значащих цифр сомножителей. Еще сложнее возникает ситуация при умножении нескольких чисел. Поэтому в произведении только в отдельных случаях используют двойное количество разрядов.

Наиболее просто операция умножения выполняется в прямом коде. При этом на первом этапе определяется знак произведения путем сложения знаковых разрядов сомножителей по модулю 2, затем производится перемножение модулей сомножителей согласно двоичной таблице умножения. Результату присваивается полученный знак.

Так как умножение производится в двоичной системе счисления, частные произведения либо равны 0 (при умножении на 0), либо самому сомножителю (при умножении на 1), сдвинутому на соответствующее количество разрядов.

Произведение можно получить двумя путями:

1) сдвигом множимого на требуемое количество разрядов и прибавлением полученного очередного частичного произведения к ранее накопленной сумме частичных произведений;

2) сдвигом суммы ранее полученных частичных произведений на каждом шаге на 1 разряд и последующим прибавлением к сдвинутой сумме неподвижного множимого либо 0.

Причем каждый из этих методов может различаться еще и тем, с младших или со старших разрядов начинается умножение.

Пример.

А=0,1101; В=0,1011;

1а) 0,1101 1б) 0,1101

0,1011 0,1011

1101 1101

1101 0000

0000 1101

1101 1101

10001111 10001111

Основываясь на вышеизложенном можно создать 4 основных метода машинного умножения в прямом коде:

1) умножение младшими разрядами множителя со сдвигом накапливаемой суммы частных произведений вправо;

2) умножение младшими разрядами множителя со сдвигом множимого влево;

3) умножение старшими разрядами множителя со сдвигом накапливаемой суммы частных произведений влево;

4) умножение старшими разрядами множителя со сдвигом множимого вправо;

Рассмотрим более детально каждую из схем умножения.

1) умножение младшими разрядами множителя со сдвигом накапливаемой суммы частных произведений вправо.

Алгоритм получения результата по данному методу может быть следующим:

1) содержимое сумматора обнуляется;

2) множимое умножается на очередной разряд множителя;

3) результат суммируется с содержимым сумматора;

4) содержимое сумматора сдвигается на 1 разряд вправо;

5) пункты 2, 3, 4 повторяются n-1 раз.

Пример.

Заданы операнды А=0,0101; В=0,1011, выполнить операцию умножения.

Таблица 1

| № | Раз-ряд | Наимено-вание | ||||||||

| п/п | мн-ля | операции | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| обнуление | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 1 | В1=1 | Ах В1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

| å | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | ||

| ® | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | ||

| 2 | В2=1 | Ах В2 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

| å | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | ||

| ® | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | ||

| 3 | В3=0 | Ах В3 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| å | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | ||

| ® | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | ||

| 4 | В4=1 | Ах В4 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

| å | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | ||

| ® | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | ||

С=0,00110111.

2) умножение младшими разрядами множителя со сдвигом множимого влево.

Алгоритм получения результата по данному методу может быть следующим:

1) содержимое сумматора обнуляется;

2) множимое умножается на очередной разряд множителя;

3) результат суммируется с содержимым сумматора;

4) множимое сдвигается на 1 разряд влево;

5) пункты 2, 3, 4 повторяются n-1 раз.

Выполнение умножения по 3-му и 4-му способам умножения можно рассмотреть по аналогии к выше рассмотренным способам.

Анализ приведенных схем умножения показывает, что длительность процесса умножения по любой схеме составляет n циклов:

Ту=nτц.

Однако длительность циклов в разных схемах одинакова. Так во второй и четвертой схемах τц=τсм и, учитывая, что τсм >τсдв, эти схемы позволяют ускорить процесс выполнения операции умножения за счет совмещения операции сложения частичных произведений и сдвигов множимого;

2) по количеству оборудования предпочтение следует отдать первой, а потом третьей схеме умножения.

Наиболее удобными для применения в ЭВМ являются 1 и 4 схемы умножения.

2. Умножение чисел, представленных в форме с плавающей запятой

Если операнды заданы в форме с плавающей запятой:

А=a2ma и B=b2mb , то их произведение С=АхВ и С=с2mc

где C=a*b*2(ma+mb)

Алгоритм умножения нормализованных чисел состоит из следующих этапов:

1. Определение знака произведения путем сложения знаковых разрядов мантисс операндов по модулю 2.

2. Алгебраическое сложение порядков сомножителей в с целью определения порядка произведения.

3. Умножение модулей мантисс сомножителей по правилам умножения чисел с фиксированной запятой.

4. Нормализация и округление мантиссы результата. Следует учесть, что мантиссы сомножителей являются нормализованными числами. Поэтому денормализация мантиссы произведения возможна только на один разряд вправо. Она устраняется путем сдвига мантиссы на один разряд влево и вычитания 1 из порядка результата.

Похожие работы

... с их использованием, имеют свою устойчивую долю рынка. В данной курсовой работе на примере цифрового сигнального процессора семейства ADSP-21xx производится разбор команд умножения и деления, выполняемых в АЛУ. Обобщенная структурная схема персонального компьютера Центральный процессор в персональных компьютерах представляет собой микропроцессор, то есть построен на одной микросхеме (БИС,СБИС). ...

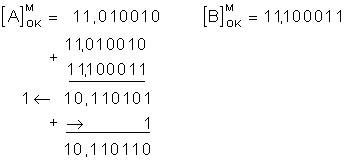

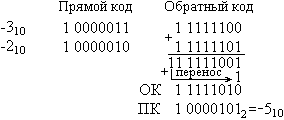

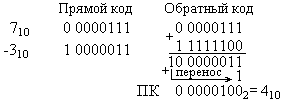

... нельзя рассматривать как единое целое. Кроме того, необходимо кроме сумматора иметь и вычитатель. В результате этого прямой код не применяется для выполнения операции алгебраического сложения, но применяется для выполнения операций умножения и деления. 1.1.3 Дополнительный код В дополнительном коде операция вычитания заменяется операцией алгебраического сложения. При этом знаковый разряд и ...

... позволит технически реализовать четыре действия арифметики в одном устройстве, называемом арифметико-логическом (АЛУ), используя одни и те же электрические схемы. 1.4.1. Представление чисел со знаками При выполнении арифметических операций в ЭВМ применяют прямой, обратный и дополнительный коды. Как уже говорилось выше, кодом называют такую запись числа, которая отличается от естественной и ...

... , связанный с формированием представлений о системно-информационном подходе к анализу окружающего мира, о роли информации в управлении, специфике самоуправляемых систем, общей закономерности информационных процессов в системах различной природы. Основой мировоззрения, главным его компонентом является научная картина мира, рассматриваемая как высший уровень систематизации и обобщения научных ...

0 комментариев