Навигация

Процедура компіляції створеного проекту в системі автоматизованого проектування MAX+PLUS II

5. Процедура компіляції створеного проекту в системі автоматизованого проектування MAX+PLUS II

Спочатку компілятор дістає інформацію про ієрархічні зв’язки між файлами проекту і перевіряє проект на звичайні помилки введення дизайнів. Він створює організаційну карту проекту і потім, комбінуючи всі файли проекту, перетворює їх в базу даних без ієрархії, яку він здатен ефективно обробляти.

Компілятор використовує різноманітні засоби збільшення ефективності проекту і мінімізації використання ресурсів пристрою. Якщо проект занадто великий, щоб бути реалізованим в одній програмувальній логічній інтегральній схемі – компілятор може автоматично розбити його на частини для реалізації в декількох пристроях того ж самого сімейства програмувальних логічних інтегральних схем, при цьому мінімізуються число з’єднань між пристроями. В файлі звітності (.rpt) буде відображено яким чином проект реалізуватиметься: в одному або декількох пристроях.

Компілятор може автоматично компілювати проект. Існують можливості задати обробку проекту у відповідності з точними вказівками розробника. Наприклад, можливо задати стиль логічного синтезу проекту та інші параметри логічного синтезу в рамках всього проекту. Крім того, зручно задавати часові вимоги в рамках всього проекту, точно вказати розбиття великого проекту на частини для реалізації в декількох пристроях і обрати варіанти параметрів пристроїв, що будуть використані для всього проекту в цілому. Користувач здатний обирати кількість виводів і логічних елементів, які залишатимуться не використаними під час плинної компіляції, щоб зарезервувати їх для наступних модифікацій проекту.

Компіляцію можна запустити з будь-якого додатку MAX+PLUS II з вікна компілятора. Компілятор автоматично обробляє всі вхідні файли плинного проекту.

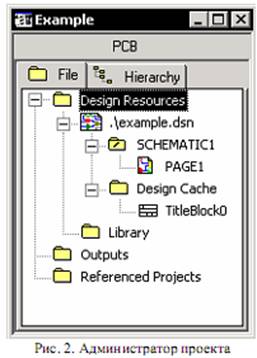

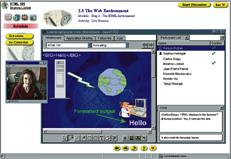

Процес компіляції можна бачити у вікні компілятора (рис. 5.1) в наступному вигляді:

1) спустошується і перевертається пісковий годинник, що вказує на активність компілятора;

2) висвітлюються, за чергою, прямокутники модулів компілятора;

3) під прямокутником модуля компілятора з’являється піктограма вихідного файлу, що був генерований даним модулем;

4) відсоток завершення компіляції поступово збільшується (до 100%);

5) під час розбиття та монтажу кнопка компілятора Stop (Стоп) перетворюється в кнопку Stop/Show Status (Стоп/Показати стан), яку користувач може вибрати для відкриття діалогового вікна, в якому відображається плинний стан розбиття і монтажу проекту;

6) при виявленні в процесі компіляції будь-яких помилок або можливих проблем автоматично відкривається вікно обробника повідомлень, в якому відображається список повідомлень про помилку, що попереджують та інформаційних повідомлень, а також відразу дається довідка по виправленню помилки. Крім того, користувач може визначити джерела повідомлень в файлах проекту або в його порівневому плані призначень.

Рис. 5.1. Процес компіляції проекту

Компілятор системи автоматичного проектування MAX+PLUS II обробляє проект, використовуючи наступні модулі та утиліти:

1) екстрактор списку ланцюгів (Compiler Netlist Extractor), що включає програми для читання форматів EDIF, VHDL, Verilog, XNF;

2) будівник бази даних (Database Builder);

3) логічний синтезатор (Logic Synthesizer);

4) роздільник (Partitioner);

5) трасувальник (Fitter);

6) екстрактор для функціонального тестування (Functional SNF Extractor);

7) екстрактор для тестування часових параметрів (Timing SNF Extractor);

8) екстрактор для тестування компонування (Linked SNF Extractor);

9) програма для запису вихідного файла в формат EDIF (EDIF Netlist Writer);

10) програма для запису вихідного файла в формат Verilog (Verilog Netlist Writer);

11) програма для запису вихідного файла в формат VHDL (VHDL Netlist Writer);

12) модуль асемблера (Assembler);

13) утиліта діагностики проекту (Design Doctor Utility).

Модуль екстрактора форматів (Compiler Netllist Extractor) перетворює кожний файл проекту в один або декілька двійкових файлів з розширенням .cnf (compiler netlist file). Оскільки компілятор підставляє значення всіх параметрів, що використовуються в параметризованих функціях, вміст cnf-файлу може змінюватись при послідовній компіляції, якщо значення параметрів змінюється. Даний модуль також створює і файл ієрархічних взаємозв’язків, з розширенням .hif (hierarchy interconnect file). В цьому файлі документуються ієрархічні зв’язки між файлами проекту, а також інформація, необхідна для показу ієрархічного дерева у вікні “Hierarchy Display”. Крім того, даний модуль створює файл бази даних вузлів з розширенням .ndb (node database), в якому містяться імена вузлів проекту для бази даних призначень ресурсів.

Модуль будівника бази даних (Database Builder) використовує файл ієрархічних зв’язків для компонування створених компілятором cnf-файлів, в яких міститься описання проекту. На основі даних про ієрархічну структуру проекту даний модуль копіює кожний cnf-файл в одну базу даних без ієрархічної структури. Таким чином, ця база даних зберігає електричні зв’язки проекту.

При створенні бази даних модуль досліджує логічну повноту та узгодженість проекту, а також перевіряє прикордонні зв’язки і наявність синтаксичних помилок. На цій стадії компіляції виявляється більшість помилок, які можуть бути тут же легко виправлені. Кожний модуль компілятора послідовно обробляє і поновлює цю базу даних.

Перший раз, коли компілятор обробляє проект, всі файли проекту компілюються. Користувач має можливість обрати “швидку повторну компіляцію” (smart recompile) для створення розширеної бази даних проекту, що дозволяє прискорити наступні компіляції. Використовуючи можливість повної повторної компіляції (total recompile), є можливість зробити вибір між повторною компіляцією лише тих файлів, які редагувались після останньої компіляції, і повною повторною компіляцією.

Модуль логічного синтезу (Logic Synthesizer) використовує ряд алгоритмів, що зменшує використання ресурсів і прибирають дубльовану логіку, забезпечуючи тим самим ефективне використання структури логічного елемента для архітектури цілої родини пристроїв. Крім того логічний синтезатор шукає логіку для не поєднаних вузлів. Якщо він знаходить такий вузол, він прибирає примітиви, що відносяться до такого вузла.

Якщо проект не вміщується при монтажі в одному пристрої, модуль роздільника (Partitioner) розділяє базу даних на декілька ПЛІС однією і тіє ж самої родини, намагаючись при цьому розділити проект на мінімальну кількість пристроїв.

Використовуючи базу даних, поновлену модулем розбиття, модуль трасування (Fitter) приводить у відповідність вимоги проекту з відомими ресурсами одного або декількох пристроїв. Він призначає кожній логічний функції положення логічного елемента, що її реалізує та обирає відповідні шляхи взаємозв’язків і призначень виводів.

Екстрактор для функціонального тестування (Functional SNF Extractor) створює файл для функціонального тестування з розширенням .snf. Компілятор генерує цей файл перед синтезом проекту, він містить всі вузли, що присутні в початкових файлах проекту.

Екстрактор для тестування часових параметрів (Timing SNF Extractor) створює, якщо компіляція проекту пройшла без помилок, файл для тестування часових параметрів, що містить дані про часові параметри проекту. Розширення файлу також - .snf.

Екстрактор для тестування компонування (Linked SNF Extractor) створює файл (.snf) для тестування компонування декількох проектів (на рівні плати). Такий файл комбінує інформацію з snf-файлів двох типів: для тестування часових параметрів і функціонального тестування, що були синтезовані для цих декількох проектів окремо.

Програма для запису вихідного файла в формат EDIF (EDIF Netlist Writer). Компілятор MAX+PLUS II може взаємодіяти з більшістю стандартних програмних засобів системи автоматичного проектування, що можуть читати файли стандартного формату EDIF 200 або EDIF 300. Даний модуль компілятора, що містить програму запису в формат EDIF, створює один або декілька файлів в форматі EDIF, з розширенням .edo.

Програма для запису вихідного файла в формат Verilog (Verilog Netlist Writer). Необов’язковий модуль програми запису в формат Verilog генерує вихідні файли з розширенням .vo, що містять інформацію про функції та їх часові параметри, отримані після проведення синтезу.

Програма для запису вихідного файла в формат VHDL (VHDL Netlist Writer). Необов’язковий модуль компілятора з програмою запису в формат VHDL генерує один або декілька вихідних файлів (.vho) на мові VHDL з синтаксисом 1987 або 1993.

Модуль асемблера (Assembler) перетворює призначення логічних елементів, виводів і пристроїв, зроблених модулем трасування, в програмний образ для пристрою у вигляді одного або декількох двійкових об’єктних файлів для програматора (.pof) і об’єктних файлів SRAM (.sof).

Утіліта діагностики проекту (Design Doctor Utility) перевіряє логіку кожного файлу проекту з метою виявлення елементів, які можуть викликати проблеми надійності на системному рівні. Ці проблеми виявляються лише після запуску пристрою “в залізі”. Існує можливість обирати одне з трьох попередніх правил обробки проекту з різними рівнями.

Похожие работы

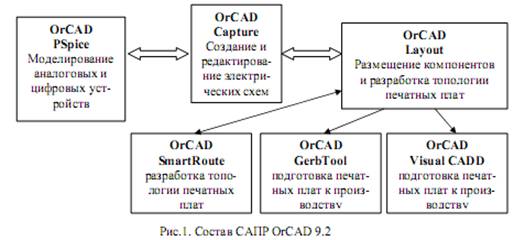

... цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС. Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності бі ...

... КП, відповідно; X Offset, Y Offset – зсув точки підключення траси відносно геометричного центру КП по осях X і Y, відповідно. Таблиця апертур (Apertures) містить опис використовуваних апертур. Таблиця Layers містить список шарів, використовуваних OrCAD Layout. Шари можуть бути наступних типів: Routing – шар трасування; Plane – шар металізації; Drill – шар символів отворів; Jumper – шар ...

... результаты отчета. Они являются кульминационным пунктом отчета и должны быть разумными, хорошо определенными, перечисленными и обоснованными [11].Практика дистанционного образования с использованием Internet Шутилов Ф.В. Особенности заочного образования - в необходимости обеспечить высокий уровень знаний при значительно меньшем времени непосредственного личного общения студентов с преподавателем. ...

0 комментариев