Навигация

Генезис програмувальних логічних інтегральних схем, їх класифікація та архітектура

1. Генезис програмувальних логічних інтегральних схем, їх класифікація та архітектура

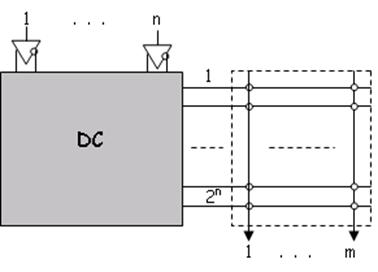

Історія розвитку програмувальних логічних інтегральних схем (ПЛІС) або програмувальних логічних пристроїв (ПЛП - Programmable Logic Devices - PLD) починається з появи на початку 70-х років програмувальних постійних запам'ятовуючих пристроїв (ППЗП - Programmable Read Only Memory - PROM). Перший час програмувальні постійні запам’ятовуючі пристрої використовувалися винятково для збереження даних, пізніше їх стали застосовувати для реалізації логічних функцій. Однак, необхідність приведення логічних функцій до завершеної диз’юнктивної нормальної форми не дозволяло використовувати PROM для реалізації функцій великих розмірів.

Спеціально для реалізації систем булєвих функцій (СБФ) великого числа змінних були розроблені і з 1971 р. стали випускатися промисловістю програмувальні логічні матриці (ПЛМ - Programmable Logic Arrays - PLAs). PLA дуже широко розповсюджені в якості універсальної елементної бази цифрових пристроїв, тому саме PLA можна вважати першими PLD.

Удосконалювання архітектури PLA призвело до появи програмувальних матриць логіки (ПЛМ - Programmable Array Logics - PALs), що дотепер визначають найбільш популярну архітектуру PLD. Перші PAL були розроблені фірмою Monolithic Memories у 1976 році, а вироблятися вони почали з 1977 року фірмою Advanced Micro Devices (AMD). З моменту своєї появи PAL стали успішно конкурувати з PLA і в даний час завдяки ряду позитивних властивостей практично цілком замінили програмувальні користувачем PLA.

Подальше удосконалювання технології виробництва інтегральних схем на початку 90-х років призвело до можливості реалізації на одному кристалі декількох PAL, поєднуваних програмувальними з'єднаннями. Подібні архітектури одержали назва складних ПЛП (Сomplex PLD - CPLD), відповідно всі розроблені раніше PLD стали називати стандартними ПЛУ (Standart PLD - SPLD) або класичними ПЛУ (Classic PLD).

Паралельно з PLD також розвивалися архітектури вентильних матриць (Gate Array - GA) і матриць логічних осередків (Logic Cell Array - LCA), у російськомовній літературі вони отримали назву базових матричних кристалів (БМК). Перші вентильні матриці були напівзамовленими, тобто програмувалися під час виготовлення, що стримувало їх широке практичне використання. Однак у 1985 році фірма Xilinix випустила програмовану користувачем вентильну матрицю (Field Programmable Gate Array — FPGA). Це дало сильний поштовх до широкого поширення вентильних матриць і конкуренції їх з PLD. Хоча FPGA і не є предметом дослідження даної роботи, згадування про них необхідно для порівняльного аналізу архітектур CPLD і FPGA.

В даний час спостерігається бурхливий розвиток архітектур CPLD і FPGA, зниження їхньої вартості, підвищення швидкодії і функціональної потужності (табл. 1.1). Це дозволяє припустити, що в найближчі п'ять років основу елементної бази цифрових систем будуть складати CPLD і FPGA.

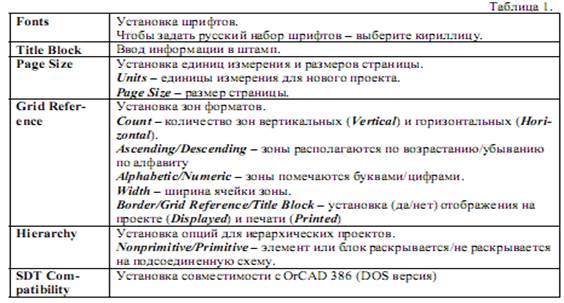

Табл. 1.1. Перспективність складних програмувальних логічних пристроїв (CPLD).

| Параметри | 1985 | 1990 | 1995 | 2000 | 2005 |

| Число вентилів, шт. | 8×102 | 5×103 | 5×104 | 1×106 | 2×106 |

| Число виводів, шт. | 6.4×101 | 2.56×102 | 5×102 | 1×103 | 2×103 |

| Число транзисторів, шт. | 8.5×103 | 2×106 | 6×106 | 2.25×108 | 5×108 |

| Швидкодія, нс | 40 | 15 | 3.5 | 1.5 | 0.75 |

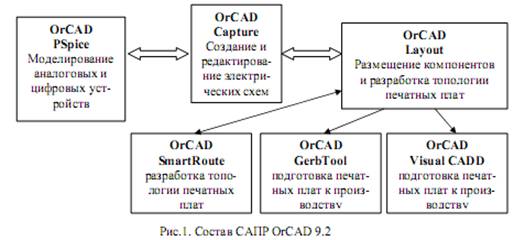

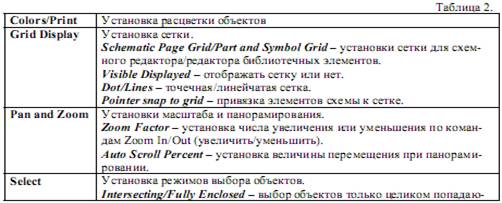

У російськомовній літературі немає чіткого поділу між PLD, PAL, PLA, SPLD, CPLD і FPGA. Найчастіше всі ці пристрої називають програмувальними логічними інтегральними схемами, чому в англомовній літературі відповідає термін programmable logic (рис. 1.1) – програмувальна логіка.

В даний час програмувальні логічні пристрої прийнято поділяти на два великих класи: стандартні програмувальні логічні пристрої (SPLD) і складні програмувальні логічні пристрої (CPLD). За своїми функціональними можливостями, ступенями інтеграції і способові використання до складних програмувальних логічних пристроїв наближаються програмовані користувачем логічні матриці.

Рис. 1.1. Класифікація програмувальних логічних інтегральних схем

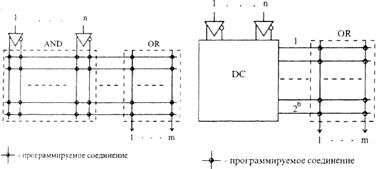

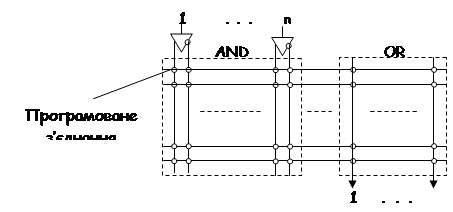

Структуру більшості SPLD умовно можливо подати у вигляді сукупності двох матриць взаємно ортогональних провідників: матриці І (AND) і матриці АБО (OR). Вхідні сигнали звичайно надходять на парафазні входи матриці І, що на ортогональних шинах дозволяє реалізувати будь-які кон’юнкції вхідних змінних. Виходи матриці І з'єднані з входами матриці АБО та на виходах реалізує диз'юнкції сигналів, що надходять.

Сукупність вихідних шин матриці І утворює множину проміжних шин PLD (product terms) або просто термів (terms).

Рис. 1.2. Структура PLA Рис. 1.3. Структура PROM

В залежності від того, яка матриця програмується, матриця І чи матриця АБО, SPLD прийнято поділяти на три класи: PLA, PROM і PAL. У PLA (рис. 1.2) програмуються обидві матриці: матриця І та матриця АБО. У PROM (рис. 1.3) матриця І постійно налаштована на функції повного дешифратора, а програмується тільки матриця АБО.

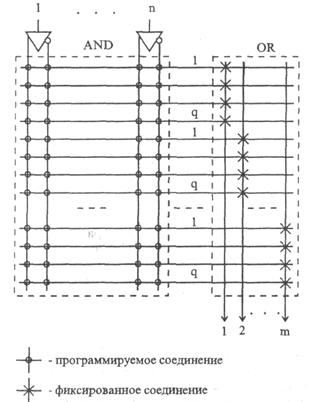

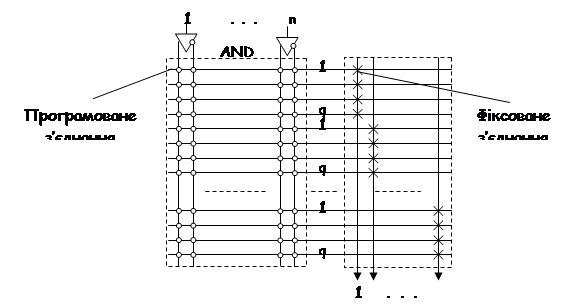

У структурі PAL (рис. 1.4), навпаки, програмується тільки матриця І, а матриця АБО має фіксоване налагодження, при якій q проміжних шин зв'язується з одним виходом. Це дозволяє матрицю АБО реалізувати у виді сукупності q-входових диз‘юнкторов.

На перший погляд може показатися, що PAL значно уступають PLA за своїми можливостями, оскільки вводиться обмеження на число проміжних шин, що приєднуються до одного виходу. Практика ж показує, що дане обмеження в більшості застосувань не критично.

Якщо все-таки це трапляється, можливо об'єднати кілька виходів по АБО за допомогою логічного елемента або провідним з'єднанням (для інверсної логіки).

Рис. 1.4. Структура PAL.

З іншого боку, у PAL програмується тільки одна матриця І, що значно спрощує структуру PAL і, як наслідок, приводить до зниження вартості пристрою і підвищенню його швидкодії. Крім того, спрощення матриці АБО дозволило додати в структуру PAL ланцюг зворотного зв'язку і вихідні буфери, завдяки чому PAL набули нових якостей.

Вихідні буфери PAL являють собою програмувальні макроосередки, що і визначають архітектуру PAL. Макроосередки PAL можуть включати вихідний інвертор із трьома станами, тригери різного типу, вентилі "АБО, що вилучає" і ін. Відповідно до типу вихідних макроосередків PAL поділяють на функціональні групи: комбінаційні, реєстрові, універсальні, асинхронні й ін. У свою чергу виробники поділяють PAL на сімейства, у яких виділяють серії пристроїв, причому в одній серії можуть зустрічатися пристрої з різних функціональних груп. Більш того, різні типи вихідних макроосередків можуть одночасно зустрічатися в одній PAL.

Безумовно, приведена класифікація не охоплює всієї розмаїтості SPLD. Наприклад, структуру, що дуже нагадує PLA, мають програмувальні логічні секвенсери (Programmable Logic Sequencers - PLS), а узагальнені матриці логіки (УМЛ - Generic Array Logics - GAL) подібні PAL.

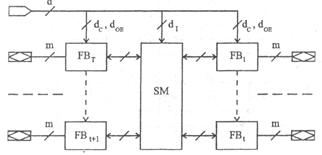

Рис.1.5. Узагальнена структура CPLD

Складними PLD прийнято називати мікросхеми високого ступеня інтеграції, структура яких являє собою сукупність функціональних блоків з архітектурою PAL (рис. 1.5), поєднаних програмувальною матрицею переключень (Switch Matrix - SM).

Багатьма фірмами випускаються різні структури CPLD. Наприклад, фірма AMD свої CPLD назвала КМОП-макроматриці високої щільності (Macro Array CMOS High-density - MACH). Фірма Altera випускає кілька видів CPLD: багаторазові матричні таблиці (Multiple Array Matrix - MAX) і FLASH-пристрої, названі за засобом перепрограмування елементів, що здатні до багаторазового налагоджування.

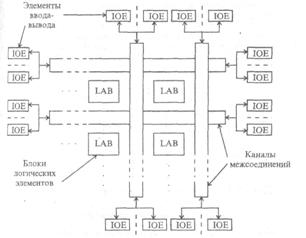

Подальший розвиток структура складних PLD одержала в мікросхемах фірми Altera, названих матрицями елементів гнучкої логіки (Flexible Logic Element Matrix - FLEX), узагальнена структура яких подана на рис. 1.6. Тут відсутня звична PAL-структура, а є лише блоки логічних елементів, поєднувані в LAB-модулі (LAB - Logic Array Block) по 8 елементів у кожнім. Відмінною рисою FLEX-пристроїв є те, що матриця переключень реалізована у вигляді горизонтальних і вертикальних каналів з’єднань (каналів трасування).

Рис. 1.6. Структура FLEX-пристроїв

Це дозволило значно зменшити площу кристала, займаного матрицею переключень, без суттєвого зниження властивостей CPLD. Елементи введення-виведення (IOE - Input/Output Element), що обслуговують зовнішні виводи, приєднуються безпосередньо до каналів з’єднань.

Архітектуру FPGA доцільно розглянути на прикладі пристроїв фірми Xilinix. Основу структури FPGA (рис. 1.7) складає матриця логічних елементів (Logic Element - LE), між якими розташовується поле з’єднань: сукупність вертикальних і горизонтальних каналів.

Якщо в FLEX-пристроях лінії каналів з’єднань безперервні і проходять через всю довжину або ширину кристала, то в FPGA лінії каналів складаються з окремих сегментів, що з'єднуються програмувальними матрицями переключень. По боках кристала FPGA розташовані блоки введення-виведення (Input/Output Blocks - IOBs).

Рис.1.7. Структура FPGA фірми Xilinix

Розглянута класифікація PLD стосується лише їх архітектури. Існують класифікації PLD за типом налагоджуваного елемента, кількістю перепрограмувань, затримці при проходженні сигналів и так далі. Виходячи з поставленого технічного завдання проектувальник самостійно обирає тип програмуємих логічних інтегральних схем, користуючись співвідношенням основних параметрів PLD (табл. 1.1) до ціни конкретної мікросхеми. Чималу роль при обранні елементної бази відіграють і досвід проектувальника, а також доступність програмних засобів ефективного синтезу логічної схеми. Останнім часом компанії-виробники PLD звернули увагу на розробку саме таких програмних пакетів.

Похожие работы

... цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС. Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності бі ...

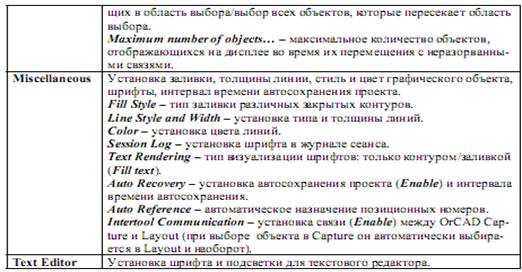

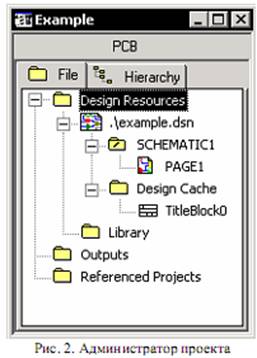

... КП, відповідно; X Offset, Y Offset – зсув точки підключення траси відносно геометричного центру КП по осях X і Y, відповідно. Таблиця апертур (Apertures) містить опис використовуваних апертур. Таблиця Layers містить список шарів, використовуваних OrCAD Layout. Шари можуть бути наступних типів: Routing – шар трасування; Plane – шар металізації; Drill – шар символів отворів; Jumper – шар ...

... результаты отчета. Они являются кульминационным пунктом отчета и должны быть разумными, хорошо определенными, перечисленными и обоснованными [11].Практика дистанционного образования с использованием Internet Шутилов Ф.В. Особенности заочного образования - в необходимости обеспечить высокий уровень знаний при значительно меньшем времени непосредственного личного общения студентов с преподавателем. ...

0 комментариев