Навигация

Коммутатор цифровых каналов системы передачи

Рис. 4.16 Функциональная схема блока формирования исходящих каналов.

ОЗУ1

ОЗУ2

Рз/сч

Dстр

Dст

Dстр

Dст

Q3 Q2 Q1

Сч2

Т RУ «0»

ГЛАВА 10

ПАТЕНТНЫЕ ИССЛЕДОВАНИЯПатентные исследования проводились при помощи онлайновой службы поиска американского национального патентного бюро. Поиск производился по ключевым словам: «communications AND E1», искались патенты 1997 и 1998 годов, результаты поиска отображены ниже.

Результаты Перебора в PATBIB-97-98 db для:

(communication AND E1): 13 патентов.

Отображено: с 1 по 13 из 13

Номер

Заглавие

5,727,160 Блок радиоуправления портом в беспроводной персональной системе связи

5,724,610 Селекторные подсистемы CDMA системы, использующие пару первых процессоров для выбора каналов CDMA, связывающие подсистему и центр обслуживания подвижных абонентов

5,708,660 Соглашения для принятия и отправления пакетов сообщения с оборудованием связи АТМ

5,705,178 Методы и композиции, основанные на запрещении вторжения клетки и фиброза анионичными полимерами

5,705,177 Методы и композиции, основанные на запрещении вторжения клетки и фиброза анионичными полимерами

5,701,465 Методы и прибор для сохранения ресурсов системы, гарантирующие качество обслуживания

5,692,038 Методы для идентификации источника телефонной связи

5,674,844 Лечение, для предотвращения потери массы кости и увеличения в метаболических процессов в кости

5,671,251 Приборы и метод работы устройства передачи данных, для избирательно функционирующего как аналоговый модем, как цифровой модем, и как терминальный адаптер

5,654,815 Методы синхронизации и единицы синхронизации, для терминального обмена

5,605,938 Методы и композиции для запрещения вторжения клетки и фиброза, использующего сульфат декстрана

5,598,401 Приборы и метод для цифрового устройства передачи данных, функционирующего в аналоговом режиме

5,592,607 Интерактивный метод и система для создания адресной информации, использующей указанные пользователем зоны адреса

Резюме Перебора

communication: 12683 слова в 6493 патентах.

E1: 193 слова в 127 патентах.

(communication AND E1): 13 патентов.

Время Перебора: 0.36 секунд.

На основе результатов перебора для рассмотрения были выбраны следующие патенты: 5,724,610 5,708,660 5,701,465 5,692,038 5,671,251 5,654,815 5,598,401 5,592,607. Ни один из них не является патентом на подобную коммутационную БИС, более подробно каждый из выбранных патентов рассмотрен далее. Следовательно проектируемая БИС обладает патентной чистотой и является потенциально перспективной для производства.

Патент, Соединенные штаты

№ 5,724,610

Март 3, 1998

Селекторные подсистемы CDMA системы, использующей пару первых процессоров для выбора каналов CDMA, связывающие подсистему и центр обслуживания подвижных абонентов

Изобретатели: Han; Jin Soo (Daejeon, KR); Cheong; Yoon Chae (Kyoungki-do, KR).

Представитель: Hyundai Electronics Industries Co., Ltd. (Kyoungki-do, KR).

Приложение №: 478,030

Зарегистрировано: 7.06.1995

Основной Ревизор: Lee; Thomas C.

Помощник Ревизора: Luu; Le Hien

Поверенный, Агент или Фирма: Merchant, Gould, Smith, Edell, Welter & Schmidt

Краткое содержание

Селекторная подсистема банка коллективного доступа с кодовым разделением. В систему включены два блока: блок SBSC и блок S/V. Блок ONE SBSC разработан, чтобы управлять двенадцатью S/V направлениями, чтобы обеспечить 96 каналов движения за SBS, и таким образом, одно S/V правление обеспечивает восемь каналов связи. Селекторная подсистема банка (SBS) коллективного доступа с кодовым разделением (CDMA) система, включает: блок SBS, блок SBS, состоящий из пары первых процессоров для управления движением фрейма CDMA и связывает подсистему (CIS), выбирая канал между CIS и центром обслуживания (MSC); двухпортовая оперативная память (DRAM) служит для хранения фрейма и управления первым процессором, а также управлением прямого доступа в память (DMAC); второй процессор служит для управления DMAC; E1 сопрягают блок данных фрейма с MSC, получая синхронизм из TFU CPS приемника; и блок S/V, связываемый между DRAM и E1 сопрягает как множество продолжений форм карты, и для получения фрейма движения к блоку интерфейса E1 после DSP. Следовательно, массовое производство модуля, имеющего конкурентоспособность, избегает сложного строения оборудования и уменьшает возможность конфликта между сигналами управлениями.

Патент, Соединенные штаты

№ 5,708,660

Январь 13, 1998

Соглашения для принятия и отправления пакетов сообщения с оборудованием связи ATM

Изобретатели: Riedel; Michael (Dresden, DE).

Представитель: Siemens Aktiengesellschaft (Munich, DE).

Приложение №: 610,366

Зарегистрировано: 4.03.1996

Основной Ревизор: Safourek; Benedict V.

Поверенный, Агент или Фирма: Hill, Steadman & Simpson

Краткое содержание

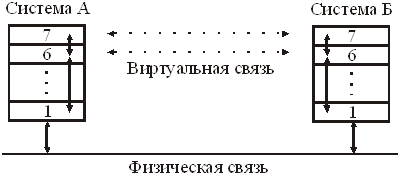

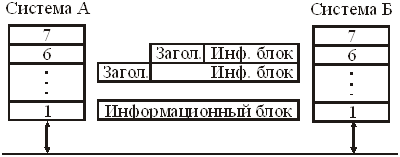

Оборудование связи ATM обслуживает отправляемые пакеты сообщений, поставленных через, по крайней мере одну магистраль (E1,...,En) в течение процесса виртуальных связей с подчиненными магистралями (A1,...,An) входящими в соответствующую виртуальную связь. Характерные параметры также, как, по крайней мере, два различных приоритета, определены для соответственной виртуальной связи в течение установленного запроса. Соответствующее расположение магистрали обслуживания имеет управляющее устройство (BHE) распределением, имеющим центральную память (СМ), в которой связанные запросом списки очередности заказов пакетов установленные для хранения пакетов сообщения. Контрольное устройство (STE), в котором сохраняется таблица распределения (LUT), соединенная с пакетом. Эта таблица распределения распределяет идентификатор списка очередности заказов также как идентификатор приоритета запроса информации (VPA/VCI) содержащийся в пакетах сообщения. Базирующиеся на критерии индивидуальных идентификаторов приоритета, идентификаторы списка очередности заказов принадлежности вставляются в список очередности заказов рассылки (Q1, Q2) распределенный соответственно приоритету. Эти списки очередности заказов рассылки обрабатываются с различными приоритетами, посредством идентификаторов списка очередности заказов, вследствие этого предлагаемые, добавления к пакету (СМ) для создания пакета сообщения.

Патент, Соединенные штаты

№ 5,701,465

Декабрь 23, 1997

Методы и прибор для сохранения ресурсов системы, гарантирующие качество обслуживания

Изобретатели: Baugher; Mark John (Austin, TX); Chang; Philip Yen-Tang (Austin, TX); Morris; Gregory Lynn (Round Rock, TX); Stephens; Alan Palmer (Austin, TX).

Представитель: International Business Machines Corporation (Armonk, NY).

Приложение №: 674,074

Зарегистрировано: 1.07.1996

Основной Ревизор: Black; Thomas G.

Помощник Ревизора: Lewis; C.

Поверенный, Агент или Фирма: Emile; Volel

Краткое содержание

Метод для обеспечения доступа к узлу, включая шаги определения, является ли ширина полосы частот доступной для передачи по линии связи, запрошенная удаленным узлом, сохранение ширины полосы частот для запрошенного доступа, если ширина полосы частот определена, как доступная, и открытие запрошенного доступа для пропускания только, если ширина полосы частот, сохранена. Кроме того, прибор для обеспечения доступа к удаленному узлу, включая прибор для определения, является ли ширина полосы частот доступной для передачи по линии связи, запрошенная удаленным узлом, прибор для сохранения ширины полосы частот для запрошенного доступа, если ширина полосы частот определена, как доступная, и прибор для открытия запрошенного доступа для пропускания, только если ширина полосы частот, сохранена.

Патент, Соединенные штаты

№ 5,692,038

Ноябрь 25, 1997

Метод для идентификации источника телефонной связи

Изобретатели: Kraus; Evan (Atlanta, GA); Yue; Drina C. (Atlanta, GA); Smets; Raymond J. (Atlanta, GA); Moquin; Thomas Joseph (Roswell, GA).

Представитель: BellSouth Corporation (Atlanta, GA).

Приложение №: 743,751

Зарегистрировано: 7.11.1996

Основной Ревизор: Matar; Ahmad F.

Поверенный, Агент или Фирма: Jones & Askew

Краткое содержание

Метод для идентификации источника связи, включая шаги: получение связи на линии запроса; идентификация строки вызывающего номера, связанного с линией запроса; доступ к базе данных, для обеспечения идентичность источника, находя вход базы данных, соответствующий строке вызывающему номеру; объявление этой идентичности источнику; и запрос подтверждения. Приоритет вызывающего оператора может использоваться, для идентификации источника. Факсимильные сообщения также могут быть идентифицированы прежде, чем сообщение поступило.

Патент, Соединенные штаты

№ 5,671,251

Сентябрь 23, 1997

Приборы и метод устройства передачи данных, для избирательно функционирующего как аналоговый модем, как цифровой модем, и как терминальный адаптер

Изобретатели: Blackwell; Steven R. (Huntsville, AL); Pearson; John Timothy (Huntsville, AL); Fridlin; C. C. (Boca Raton, FL).

Представитель:Motorola, Inc. (Schaumburg, IL).

Приложение №: 395,332

Зарегистрировано: 28.02.1995

Основной Ревизор: Chin; Wellington

Помощник Ревизора: Luther; William

Поверенный, Агент или Фирма: Gamburd; Nancy R.

Краткое содержание

Прибор и метод для устройства передачи данных, для избирательного функционирования в множестве аналоговых и цифровых способов, таких как аналоговый модем, как цифровой модем, и как терминальный адаптер. Конструктивные исполнения обеспечивают единственное устройство связи сгруппированных данных, которое будет конфигурировано и впоследствии реконфигурирован, чтобы обеспечить передачу данных в ряд сетей, включая общественные телефонные сети и цифровые сети, включая T1, E1 и ISDN. Различные конструктивные исполнения также обеспечивают сигнальное моделирование различных сетей, так, что фактическая сеть является прозрачной для терминала и пересылки информации через устройство связи в сеть.

Патент, Соединенные штаты

№ 5,654,815

Август 5, 1997

Методы синхронизации и единицы синхронизации, для терминального обмена

Изобретатели: Bunse; Stephan (Stuttgart, DE).

Представитель: Alcatel N.V. (NL).

Приложение №: 440,822

Зарегистрировано:15.05.1995

Краткое содержание

Синхронизация между двумя местами в оптической системе связи, соотнося полученный сигнал синхронизации с сигналом синхронизации с станции и управляя тактами собственно станции соответственно, корреляция происходит в одном месте, но изделие корреляции работает в другом месте (E1-E3), и сигнал такта последних управляется соответственно. Это может быть выполнено, посылая первую последовательность битов синхронизаций от терминала (E1-E3), и делая петлю, это поддерживают в обмене скорости передачи информации в битах второй последовательности битов синхронизации, генератор синхронизма терминала (E1-E3) управляется согласно полученной последовательности битов корреляций. Это имеет преимущество при обмене, так как синхронизация требует только оптических переключателей и никаких оптико-электронных преобразователей. Это разрешает все оптические обмены и устраняет один оптико-электронный преобразователь соединенного абонента. Единственный недостаток - то, что для передатчика без приемника, дополнительный обратный канал является необходимым.

Патент, Соединенные штаты

№ 5,598,401

Январь 28, 1997

Приборы и метод для цифрового устройства передачи данных, функционирующего в аналоговом режиме

Изобретатели: Blackwell; Steven R. (Huntsville, AL); Pearson; John T. (Huntsville, AL); Fridlin, IV; Charles C. (Boca Raton, FL).

Представитель: Motorola, Inc. (Schaumburg, IL).

Приложение №: 407,749

Зарегистрировано: 21.03.1995

Основной Ревизор: Marcelo; Melvin

Поверенный, Агент или Фирма: Gamburd; Nancy R

Краткое содержание

Прибор и метод для устройства передачи данных, для избирательного функционирования в множестве аналоговых и цифровых способов, таких как аналоговый модем, как цифровой модем, и как терминальный адаптер. Конструктивные исполнения обеспечивают единственное устройство связи и группирование данных, которое будет конфигурировано и также впоследствии реконфигурировано, чтобы обеспечить передачу данных в ряд сетей, включая общественные телефонные сети, выделенный канал, и цифровые сети, включая T1, E1 и ISDN. Различные конструктивные исполнения далее обеспечивают выбор основного цифрового рабочего режима при одновременном обеспечении автоматической реконфигурации для вспомогательного или запасного аналогового рабочего режима. Различные конструктивные исполнения также обеспечивают сигнальное моделирование различных сетей, такой, что фактическая соединенная сеть является прозрачной для терминала и пересылки данных через устройство связи в сеть.

Патент, Соединенные штаты

№ 5,592,607

Январь 7, 1997

Интерактивный метод и система для создания адресной информации, использующей указанные пользователем зоны адреса

Изобретатели: Weber; Karon A. (San Francisco, CA); Poon; Alex D. (Mountain View, CA); Moran; Thomas P. (Palo Alto, CA).

Представитель: Xerox Corporation (Stamford, CT).

Приложение №: 138,545

Зарегистрировано: 15.10.1993

Основной Ревизор: Powell; Mark R.

Помощник Ревизора: Ho; Ruay Lian

Поверенный, Агент или Фирма: Bares; Judith C.

Краткое содержание

Интерактивный метод и система, для поддержания и облегчения задачи в урегулирования, прежде всего, в реальном времени. В одном конструктивном исполнении, пользователь системы использует пишущее устройство, чтобы войти в форму рукописных штрихов, которые сохранены и соотнесены с адресом, типа времени, обеспеченного синхронизацией системы. Счета собраны в структуре данных, представляемой пространственной областью на показе названном адресом, или временем, зона, которая создана, когда пользователь входит в нее, запрашивающее адрес из системы. Все счета, введенные в специфическую область часового пояса в экспозиционной площади сохранены в блоке структуры данных, соотнесенной со временем, связанным с областью зоны того времени, и, в то время как часовые пояса созданы в последовательном приказе, ограниченном по времени, счет - может быть введен в зоны времени в любой последовательности и все еще может быть соотнесен с зоной того времени. Дополнительная возможность обеспечивает обозначение блока пользовательских счетов как ключевое слово, которое может затем быть связано с другими часовыми поясами, чтобы соединить ключевые слова со временами и счетами. Штрихи вошли и обозначили, поскольку ключевое слово назначено уникальный, распознаваемый системой идентификатор. Структура данных хранит штрихи ключевого слова, расположение в экспозиционной площади и зонах времен, с которыми это связано. Хорошо-разработанный интерфейс пользователя обеспечивает рабочие области окна для создания и использования часовых поясов и для легко отображения и использования ключевых слов.

ГЛАВА 3

РАЗРАБОТКА ФУНКЦИОНАЛЬНО-ЛОГИЧЕСКОЙ СХЕМЫ БЛОКОВ ПРОЕКТИРУЕМОГО УСТРОЙСТВАФУНКЦИОНАЛЬНАЯ СХЕМА БЛОКА ВЫДЕЛЕНИЯ ЦИКЛОВОЙ И СВЕРХЦИКЛОВОЙ СИНХРОНИЗАЦИИ

Синхронизация БИС коммутации по циклам и сверхциклам обеспечивает правильное распределение коммутируемого сигнала по каналам, а также правильное декодирование кодовых групп. Работа приемников цикловой и сверхцикловой синхронизации основана на передаче в групповом канале кодовых групп цикловой и сверхцикловой синхронизаций. Причем работа приемника сверхцикловой синхронизации практически не отличается от работы приемника цикловой синхронизации, только установка сверхцикловой синхронизации начинается после установки цикловой.

К аппаратуре систем синхронизации предъявляются следующие требования:

Время вхождения в синхронизм при первоначальном включении аппаратуры в работу и время восстановления в синхронизм при его нарушении должно быть минимальным;

Приемник синхросигнала должен быть помехоустойчив, что обеспечивает большее среднее время между сбоями синхронизма.

На БЛОК ВЫДЕЛЕНИЯ ЦИКЛОВОГО И СВЕРХЦИКЛОВОГО СИНХРОНИЗМА поступают входящие групповые каналы и тактовые импульсы, выделенные линейным оборудованием станции (ВТи), функция этого блока состоит в выделении из групповых каналов синхроимпульсов цикловой и сверхцикловой синхронизации. Структурно такой блок должен состоять из 8ми приемников цикловой и сверхцикловой синхронизации (см. рис. 4.1).

БЛОК ВЫДЕЛЕНИЯ ЦИКЛОВОГО И СВЕРХЦИКЛОВОГО СИНХРОНИЗМА

Приемник цикловой и сверхцикловой синхронизации

Приемник цикловой и сверхцикловой синхронизации

Приемник цикловой и сверхцикловой синхронизации

Приемник цикловой и сверхцикловой синхронизации

Приемник цикловой и сверхцикловой синхронизации

Приемник цикловой и сверхцикловой синхронизации

Приемник цикловой и сверхцикловой синхронизации

Приемник цикловой и сверхцикловой синхронизации

- канал ИКМ - 30/32;

- ВТи ;

- данные на УУ.

Рис. 4.1 Структура блока.

Приемник цикловой и сверхцикловой синхронизации обеспечивает установление синхронизма после включения аппаратуры в работу, контроль за состоянием синхронизма в рабочем режиме, обнаружение сбоя синхронизма и его восстановление.Структурно приемник цикловой и сверхцикловой синхронизации состоит из (см. рис. 4.2):

Опознаватель синхросигнала - предназначен для выделения из группового ИКМ сигнала кодовых последовательностей по структуре совпадающих с синхросигналом. Блок содержит два выхода, на одном из которых появляется импульс в момент прихода кодовой комбинации циклового синхросигнала (КЦС), а на другом - в момент прихода кодовой комбинации сверхциклового синхросигнала (КСЦС).

Анализатор циклового и анализатор сверхциклового синхронизма определяют наличие соответствующего синхронизма (НС) или его отсутствие (ОС).

Решающее устройство определяет пропадание синхронизма, но поддерживает нормальную работу коммутатора даже при пропадании двух синхрогрупп подряд.

Генератор импульсной последовательности вырабатывает определенный набор импульсных последовательностей, используемых для управления работой функциональных узлов коммутатора, их синхронизации. На его выходе вырабатываются три группы импульсов: разрядные, канальные и цикловые.

Входящий групповой канал

Выделенный тактовый импульс

ОПОЗНОВАТЕЛЬ

НС

КЦС

ОС

НС

КСЦС

ОС

Рис. 4.2 Структурная схема приемника цикловой и сверхцикловой синхронизации.

Рассмотрим функциональные схемы каждого из блоков приемника цикловой и сверхцикловой синхронизации.

Функциональная схема (см. рис. 4.3) опознавателя синхронизма содержит регистр сдвига и дешифратор, представляющие собой две схемы совпадения, на выходе одной из которых появляются импульс в момент прихода КЦС, а на выходе другой - в момент прихода КСЦС. Схема регистра сдвига построена на 8ми тактируемых D – триггерах, а схемы совпадения кодовых комбинаций представляют собой схемы И.

Рис. 4.3 Функциональная схема опознавателя кодовых комбинаций циклового и сверхциклового синхросигналов.

Функциональная схема анализатора циклового (сверхциклового) синхронизма (рис. 4.4) содержит схему совпадения, определяющую наличие синхронизма и схему выдающую логическую «1» на выходе в момент прихода кодовой комбинации синхросигнала при отсутствии синхронизма.

Рис. 4.4 Функциональная схема анализатора циклового (сверхциклового) синхронизма.

Решающее устройство содержит двоичный счетчик - накопитель по выходу из синхронизма, двоичный счетчик - накопитель по входу в синхронизм и схему совпадения (см. рис. 4.5).

Рис. 4.5 Функциональная схема решающего устройства.

Функциональная схема генератора импульсной последовательности содержит три распределителя импульсов: распределитель разрядных импульсов (РР), распределитель канальных импульсов (РК) и распределитель цикловых импульсов (РЦ), каждый из которых реализован в виде двоичного счетчика и дешифратора, и двух схем совпадения, на выходе одной из них формируется сигнал цикловой синхронизации, а на выходе другой сигнал сверхцикловой синхронизации (см. рис. 4.6).

Функциональная схема всего блока представлена на рисунке 4.7. Рассмотрим работу схемы приемника цикловой и сверхцикловой синхронизации. Накопитель по входу в синхронизм обеспечивает защиту приемника от ложного синхронизма в режиме поиска, когда на вход поступают случайные комбинации группового сигнала, совпадающие с синхросигналом. Обычно накопитель по входу в синхронизм содержит два - три разряда. Накопитель по выходу из синхронизма необходим для исключения ложного нарушения синхронизма. Обычно накопитель по выходу из синхронизма содержит четыре - шесть разрядов.

В режиме синхронизма накопитель по входу в синхронизм заполнен, а накопитель по выходу - пуст. Сигнал наличие синхронизма (НС) на выходе держит накопитель по входу в синхронизм. Случайные кодовые комбинации, совпадающие с кодовой комбинацией синхросигнала, не будут влиять на работу приемника.

При отсутствии кодовой комбинации синхросигнала (КЦС или КСЦС) из-за воздействия помехи или других причин цикловый или сверхцикловый сигнал генератора импульсной последовательности сформирует на выходе анализатора циклового (сверхциклового) синхронизма сигнал отсутствия синхронизма (ОС), который поступит на вход накопителя по выходу из синхронизма. Если нарушения синхронизма кратковременны (1-3 цикла), то следующий сигнал КЦС (КСЦС) совпадет по времени с цикловым или сверхцикловым сигналом от генератора импульсной последовательности и запишет «1» в накопитель по входу в синхронизм, а так как накопитель заполнен, то его выходной сигнал сбросит три младших разряда накопителя по выходу из синхронизма в нулевое состояние и синхронная работа устройства не нарушится.

При длительном нарушении синхронизма накопитель по выходу будет заполнен, на его выходе появится логическая единица и начнется поиск синхронизма. Теперь первый же импульс от опознавателя установит в начальное нулевое состояние разрядный и канальный распределители, а также старший разряд накопителя по выходу из синхронизма.

Следующее опознавание будет произведено ровно через цикл (сверхцикл). Если синхросигнал выделен верно, то в накопитель по входу будет записана «1». При трехкратном совпадении сигналов КЦС (КСЦС) и циклового (сверхциклового) сигналов от генератора импульсной последовательности накопитель по входу в синхронизм заполнится и установит «0» в трех младших разрядах накопителя по выходу из синхронизма (в четвертом разряде накопителя по выходу «0» был установлен ранее). Синхронная работа устройства установлена.

Рис. 4.6. Функциональная схема генератора импульсной последовательности.

ФУНКЦИОНАЛЬНАЯ СХЕМА БЛОКА ЦИКЛОВОГО ВЫРАВНИВАНИЯ И КОММУТАЦИИ

На БЛОК ЦИКЛОВОГО ВЫВРАВНИВАНИЯ И КОММУТАЦИИ поступают входящие групповые каналы, и его функция заключается в выравнивании каналов в соответствии с сигналом синхронизации УСТРОИСТВА УПРАВЛЕНИЯ и коммутировании каналов в соответствии с адресом, поступающим с УСТРОЙСТВА УПРАВЛЕНИЯ.

Рассмотрим принцип циклового выравнивания входящих групповых каналов, он заключается в записи в запоминающее устройство информации входящих групповых каналов синхронно с выделенными тактовыми импульсами и считывании их синхронно со станционными импульсами тактовой и цикловой синхронизации.

Для осуществления коммутации необходимо сформировать общий, уплотненный во времени канал, и переставить импульсы из одной временной позиции в другую. Как отмечалось выше технически такую перестановку легко выполнить в запоминающем устройстве, если записывать информацию общего канала последовательно, а считывать в соответствии с картой коммутации.

Объединение процессов циклового выравнивания и коммутации позволяет сократить необходимый объем запоминающего устройства и уменьшить время задержки прохождения информационных сигналов. Для обеспечения данных функций блок ЦИКЛОВОГО ВЫРАВНИВАНИЯ И КОММУТАЦИИ должен содержать утроенное количество запоминающих устройств. Это необходимо для запоминания информации входящих групповых каналов в случае потери синхронизации одного из них (восстановление синхронизма происходит максимум в течение трех циклов). Структурная схема такого устройства представлена на рисунке 4.8.

СТи

В/в КУ

Рис20 Структурная схема блока ЦВПКиК

БЛОК ЦИКЛОВОГО ВЫРАВНИВАЕИЯ И КОММУТАЦИИ

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО КОММУТАЦИИ

ВГК

ВТи

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО КОММУТАЦИИ

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО КОММУТАЦИИ

От УУ

СТи

Рис. 4.8. Структура блока.

Рассмотрим структурную схему БЛОКА ЦИКЛОВОГО ВЫРАВНИВАНИЯ И КОММУТАЦИИ:

Запоминающее устройство коммутации, предназначено для коммутации входных каналов (запись информации ведется последовательно, а считывание происходит в соответствии с картой коммутации), одновременно с коммутацией происходит временное уплотнение входящих групповых каналов. Для выравнивания предусмотрено наличие трех запоминающих устройств коммутации, при заполнении одного из них информацией нескольких (не всех) каналов автоматически начинается заполнение следующего и т.д.

Запоминающее устройство адреса, предназначено для хранения номеров (адресов) коммутируемых каналов.

ФУНКЦИОНАЛЬНАЯ СХЕМА ЗАПОМИНАЮЩЕГО УСТРОЙСТВА КОММУТАЦИИ.

Для обеспечения указанных выше функций запоминающее устройство коммутации должно записать информацию всех 256ти каналов за один цикл, т.е. должно обладать емкостью:

256 * 8 [бит] = 2048 [бит]. (4.1)

Организация запоминающего устройства коммутации зависит от режима работы:

При записи данное запоминающее устройство представляет собой восемь ОЗУ с разрядной организацией, в каждое из которых записывается информация соответствующая входящему групповому каналу синхронно со своей выделенной тактовой частотой и цикловым синхросигналом. Емкость каждого из ОЗУ:

32 * 8 [бит] = 256 [бит]. (4.2)

При считывании запоминающее устройство коммутации представляет собой одно ОЗУ со словарной организацией (емкостью 256*8 [бит]). В каждой ячейке ОЗУ содержится информация одного информационного канала. Следовательно, все восемь разрядов каждого из информационных каналов можно считывать одновременно по параллельному каналу. Таким образом, одновременно с коммутацией осуществляется уплотнение восьми групповых каналов в один общий групповой канал, передаваемый по параллельной шине, что позволяет снизить внутреннюю скорость передачи данных до 2,048 Мбит/с.

Структурно схему запоминающего устройства коммутации можно представить в виде восьми ОЗУ емкостью 256 бит каждая, выходы которых объединены общей параллельной шиной, а на входы каждого из ОЗУ поступают соответствующие групповые каналы и выделенные тактовые импульсы. Такая схема представлена на рисунке 4.9.

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО КОММУТАЦИИ

чтение/запись

Адрес чтения

ВГК

ВТи

Параллельная шина

Рис. 4.9. Структурная схема запоминающего устройства коммутации.

Рассмотрим функциональную схему одного из восьми ОЗУ (см. рис. 4.10), она включает в себя:

Счетчик тактовых импульсов, предназначенный для формирования адреса в режиме записи (Сч2).

Дешифраторы строк и столбцов, предназначенные для правильного функционирования матрицы памяти (D).

Мультиплексор, предназначенный для переключения считывания адреса столбца от счетчика в режиме записи или от запоминающего устройства адреса (ЗУА) в режиме считывания (М).

Н

ВГК

У «О»

Выбор ЗУ

Рз/сч

ОЗУ8*32

Dст А1 А2 А3 А4 А5 ДDстр А1А2

А3

Сч2 Q1Q2

Q3

ТR

MD1D2 D3 D4 D5

А От ЗУАQ1Q2Q3Q4Q5

Cч2

ТR

Р8D1D2 D3 D4 D5

ВТи

Параллельная шина

епосредственно матрица памяти, состоящая из 256ти элементов (8*32).Рис. 4.10. Функциональная схема ОЗУ запоминающего устройства коммутации.

Принцип работы данной схемы состоит в следующем:

В режиме записи (Рз/сч=1) мультиплексор подключает к дешифратору столбцов старшие 5 разрядов счетчика адреса, 3 младшие разряда счетчика подключены к дешифратору строк. ЗУ в этом режиме имеет разрядную организацию.

В режиме считывания (Рз/сч =0) мультиплексор подключает к дешифратору столбцов ЗУА, а дешифратор строк при этом отключается и ОЗУ приобретает словарную организацию каждые из восьми элементов памяти входящих в состав столбцов матрицы памяти образуют ячейку памяти и считываются параллельно.

ФУНКЦИОНАЛЬНАЯ СХЕМА ЗАПОМИНАЮЩЕГО УСТРОЙСТВА АДРЕСА.

Запоминающее устройство адреса предназначено для хранения адреса входящего канала, который поступает на выход в момент поступления станционного тактового импульса, соответствующего номеру исходящего канала. Каждому из восьми ОЗУ, рассмотренных выше соответствует отдельное запоминающее устройство адреса, т.е. каждому входящему групповому каналу соответствует свое запоминающее устройство адреса (см. рис. 4.11).

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО АДРЕСА

чтение/запись

Рис. 4.11. Структурная схема запоминающего устройства адреса.

Для обеспечения правильного функционирования схемы необходимо запомнить адрес входящего канала, который состоит из 5ти разрядов:

25 = 32. (4.3)

Но для функционирования УСТРОЙСТВА УПРАВЛЕНИЯ нужно знать о состоянии канала в любой момент времени, для этого разрядность запоминающего устройства адреса необходимо увеличить на 1 бит, который отображает состояние канала («1» – канал занят; «0» – канал свободен). Этот разряд так же может управлять состоянием выходной ячейки ОЗУ, при появлении в данном разряде «0» выходная ячейка ОЗУ переходит в третье состояние (для этого выходные ячейки ОЗУ должны быть построены по соответствующей схеме). Следовательно, данное запоминающее устройство должно обладать емкостью:

32 * 6 [бит] = 192 [бит]. (4.4)

Запоминающее устройство адреса имеет словарную организацию, как при записи информации, так и при считывании (одно слово обладает разрядностью 6 бит). Функциональная схема данного устройства представлена на рисунке 4.12.

Выбор ЗУ

Ти

Рз/сч

на ОЗУ

ОЗУ

6*32

Рз/сч

&

У «О»

На УСТРОЙСТВО УПРАВЛЕНИЯ

Рис. 4.12. Функциональная схема запоминающего устройства адреса.

Функциональная схема запоминающего устройства адреса состоит из:

Матрица памяти 6*32, предназначенная для хранения адреса коммутируемого канала.

Дешифратора столбцов (D), предназначенного для правильного функционирования матрицы памяти.

Счетчика тактовых импульсов (Сч2), предназначенного для формирования адреса считываемой или записываемой информации.

Схемы совпадения, предназначенной для формирования сигнала считывания из ОЗУ коммутации.

Работает устройство следующим образом:

В режиме записи (запись ведется, как в адресное ЗУ, так и в ЗУ коммутации), в соответствии с тактовыми импульсами записывается информация об адресе коммутируемого канала и его состоянии на данный момент. Информация поступает от УСТРОЙСТВА УПРАВЛЕНИЯ в виде 6ти разрядных слов.

В

Сигнал считывания на ЗУК

Сигнал считывания на ЗУА

t

t

Ти

Ти

Ти

- Считывание разрешено

режиме считывания информации адрес коммутируемого канала должен поступить немного раньше начала считывания информации из запоминающего устройства коммутации, для этого необходима схема совпадения, формирующая сигнал разрешения чтения на запоминающее устройство коммутации. Так как сигнал разрешения чтения для запоминающего устройства адреса является постоянным, а информация на выходе обновляется благодаря счетчику тактовых импульсов, постоянно меняющему адрес считывания; то при включении схемы совпадения тактового импульса и сигнала разрешения чтения, на выходе этой схемы будет формироваться сигнал, соответствующий моменту поступления адреса на запоминающее устройство коммутации. Следовательно, при подаче этого сигнала на запоминающее устройство коммутации, в качестве сигнала разрешения чтения, чтение из этого устройства будет производиться в нужный момент времени. Временные диаграммы, поясняющие работу схемы совпадения представлены на рисунке 4.13.Рис. 4.13. Временные диаграммы, поясняющие принцип работы, устройства совпадения.

КОММУТАЦИОННЫЙ ЭЛЕМЕНТ.

Введем понятие коммутационного элемента. Коммутационный элемент - это совокупность запоминающего устройства адреса и ОЗУ запоминающего устройства коммутации, функциональная схема коммутационного элемента представлена на рисунке 4.14. Схема БЛОКА ЦИКЛОВОГО ВЫРАВНИВАНИЯ И КОММУТАЦИИ содержит двадцать четыре коммутационных элемента, т.е. по три на каждый из входящих групповых каналов.

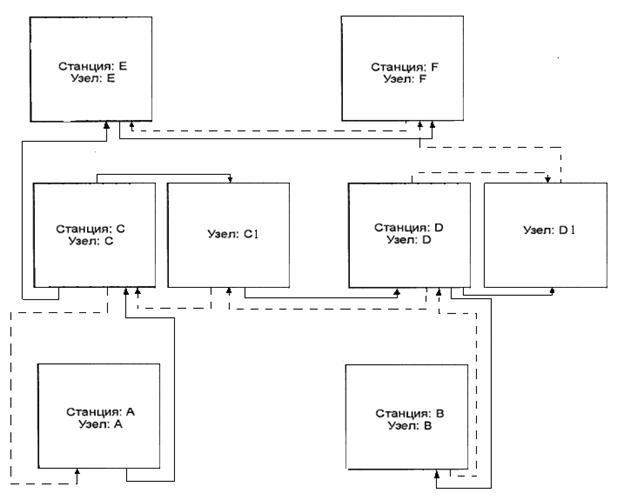

ФУНКЦИОНАЛЬНАЯ СХЕМА БЛОКА ФОРМИРОВАНИЯ ИСХОДЯЩИХ КАНАЛОВ

Б

БЛОК ФОРМИРОВАНИЯ ИСХОДЯЩИХ КАНАЛОВ

ЗУ1

ЗУ2

Рз/сч

параллельная шина

исходящие групповые каналы

ЛОК ФОРМИРОВАНИЯ ИСХОДЯЩИХ ГРУППОВЫХ КАНАЛОВ, предназначен для формирования 8ми каналов стандарта ИКМ - 30/32 из поступающего на его вход уплотненного во времени и разнесенного в пространстве скоммутированного канала. Для обеспечения непрерывного формирования каналов блок нуждается в двух запоминающих устройствах, в каждый момент времени из одного идет считывание, а в другой идет запись. Структурная схема такого блока представлена на рисунке 4.15.Рис. 4.15. Структура блока.

Для расчета емкости каждого из двух элементов памяти необходимо выяснить принцип работы блока. В момент записи по параллельной шине передается восемь разрядов одного из каналов, следовательно, ОЗУ должно содержать восемь элементов в столбце. В момент считывания формируются восемь исходящих групповых каналов, в каждый момент времени на выход поступают восемь бит, по одному на каждый канал; следовательно, ОЗУ должно содержать восемь столбцов. Таким образом, общая емкость ОЗУ составляет:

8 * 8 [бит] = 64 [бит]. (4.4)

Организация ОЗУ словарная, но при записи информации каждая ячейка памяти состоит из элементов памяти, входящих в соответствующий столбец матрицы, а при считывании - из элементов, входящих в соответствующую строку. Функциональная схема данного устройства представлена на рисунке 4.16, она состоит из:

Собственно матрицы памяти, они предназначены для хранения информации.

Дешифраторы строк и столбцов, предназначены для правильной работы матриц памяти.

Счетчик предназначен для формирования адресов записи и считывания.

Инвертор предназначен для переключения записи/чтения.

Принцип работы этой схемы заключается в следующем, при записи со счетчика адреса трехразрядный код поступает на дешифратор столбцов (Dст), а дешифратор строк (Dстр) отключается и восемь разрядов одного информационного канала поступает на элементы памяти выбранного столбца. При считывании отключается дешифратор столбцов (Dст), а трехразрядный код счетчика адресов поступает на дешифратор строк (Dстр) и восемь одноименных разрядов разных информационных каналов выбранной строки матрицы поступают на соответствующие восемь выходов исходящих групповых каналов. В результате на выходе коммутационной БИС формируются групповые каналы в стандарте ИКМ -30/32.

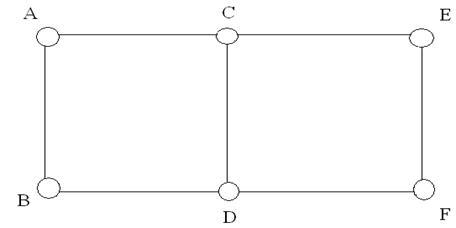

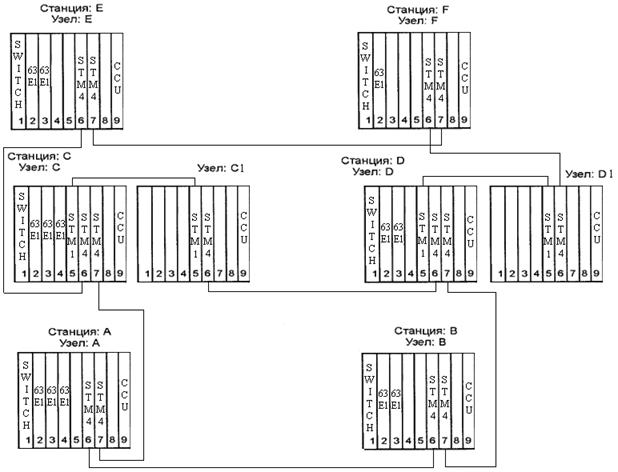

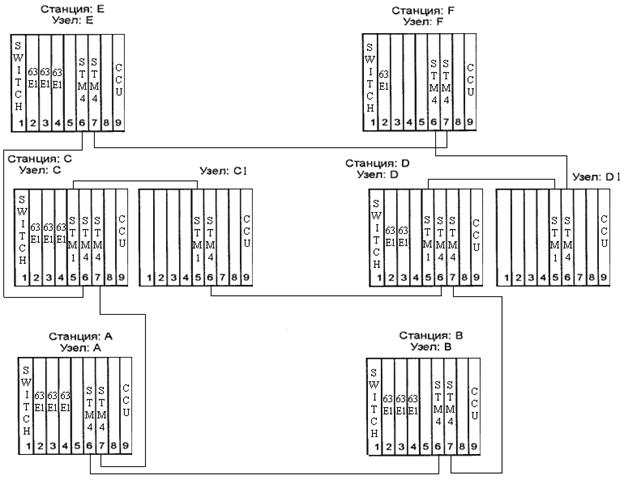

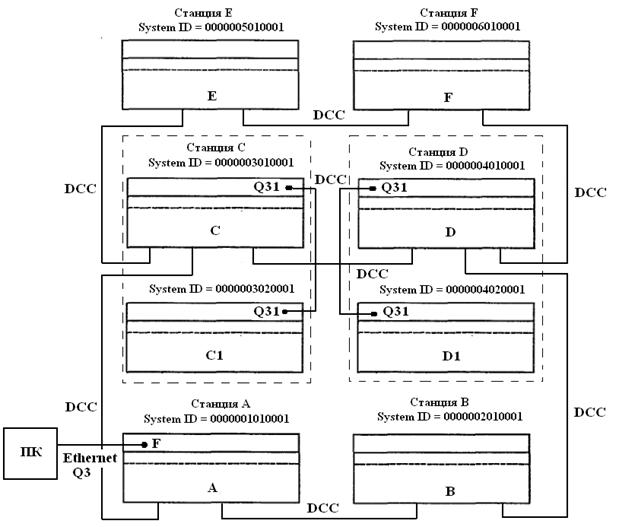

ГЛАВА 2

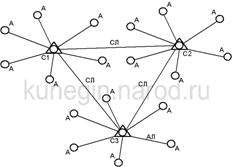

РАЗРАБОТКА СТРУКТУРНОЙ СХЕМЫ УСТРОЙСТВАСРАВНЕНИЕ ПРОЕКТИРУЕМОЙ СИСТЕМЫ С ЦИФРОВОЙ ТРАНСПОРТНОЙ СЕТЬЮ КОМПАНИИ “МТУ-ИНФОРМ”

Прежде всего необходимо отметить, что обе системы имеют в своей основе кольцевой принцип построения сети, что обеспечивает преимущества по сравнению с радиальной схемой построения сети (см. Введение). Основным отличием проектируемой системы от сети, построенной по принципу Синхронной Цифровой Иерархии, является снижение минимальной пропускной способности канала до 2,048 Мбит/с, это накладывает определенные условия на построение устройств обеспечивающих работу сети. Вторым важным отличием проектируемой системы является децентрализация управления, которая позволяет использовать устройства системы независимо от центрального узла управления, что в конечном итоге позволяет продолжить работу сети при выходе из строя центрального управляющего элемента, и тем самым повысить надежность системы вцелом.

Похожие работы

... эксплуатации (станционный сервер). Подключение выполняется посредством соединения через COM-порт или через соединение локальной сети Ethermet 100 Мбит/с. Связь сервера с терминалами центра управления осуществляется посредством локальной сети. 6. Цифровые системы уплотнения аналоговых линий Задача таких систем заключается в экономии физических линий связи, когда на одну пару телефонной линии ...

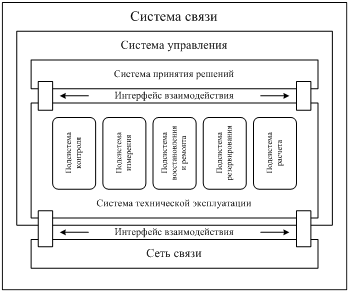

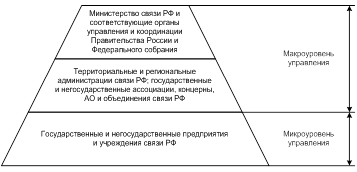

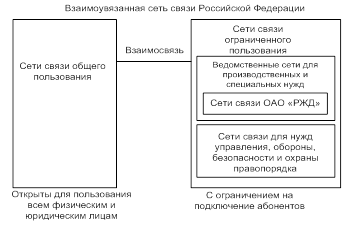

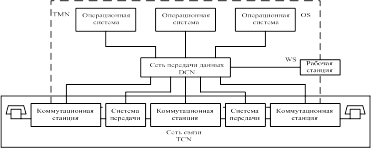

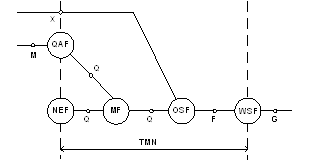

... Каждому элементу соответствует численный и символьный идентификатор. В имя переменной включается полный путь до нее от корневого элемента root. 3. Система мониторинга и администрирования 3.1 Системы управления технологическим сегментом магистральной цифровой сети связи ОАО «РЖД» РФ При построении современных цифровых сетей следует различать следующие сетевые уровни: уровень первичной ...

... ПО. Центральное ПО может взаимодействовать с другими функциональными блоками в центральном процессоре. Взаимодействие функциональных блоков всегда происходит на уровне CP. 3 Виды доступа В коммутационной системе AXE-10 используется различное оборудование доступа, которое позволяет строить сети с достаточной гибкостью. К этому оборудованию относится следующее: - Удаленный абонентский ...

... нм; - STM-4 L-4.2 - модуль оптического приемопередатчика организует один оптический интерфейс STM-4 (или STM-4c), связанный с модулем кроссовой коммутации, работает на длине волны 1550 нм; - STM-16 - модуль оптического компонентного интерфейса; - Gigabit Ethernet - модуль позволяет организовать передачу данных в формате Gigabit Ethernet с сетевой топологией «точка-точка»; - 63 Е1 - плата ...

0 комментариев