Навигация

РАЗРАБОТКА СТРУКТУРНОЙ СХЕМЫ УСТРОЙСТВА

2. РАЗРАБОТКА СТРУКТУРНОЙ СХЕМЫ УСТРОЙСТВА

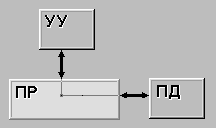

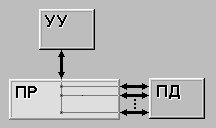

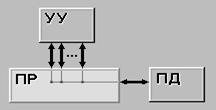

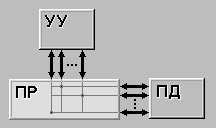

Устройства подключается через разъём к Управляющей компьютерной системе(УКС), от которой оно будет получать управляющие сигналы, данные и которому оно будет в ответ выдавать результат вычисления.

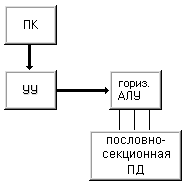

Анализируя поставленную задачу можно определить основные блоки включающие в себя устройство.

Так сигналы от УКС будут поступать на устройство ввода-вывода информации (УВВ), которое может присутствовать только абстрактно в нашем устройстве.

Из устройства ввода вывода данные будут поступать в ОЗУ, а управляющие сигналы непосредственно в блок управления. Блок управления (УУ) должен синхронизировать и контролировать работу всего модуля в целом. При этом он должен вырабатывать сигналы чтения и записи из ОЗУ и ПЗУ, а также сигналы управления блоком вычислений (ОБ).

В ОЗУ хранятся входные величины, промежуточные данные и результат. В ПЗУ может храниться микропрограмма вычисления, а также таблицы значений констант таких как Arth(2-i), log(1+ri2-i) и 2-i, .

Это один из возможных вариантов структурной схемы. Ее можно реализовать на ПЛИС или на интегральных схемах средней степени интеграции. Реализации на ПЛИС более дорогая и трудоемкая в сравнении с другими способами. На интегральных микросхемах средней степени интеграции устройство получится более дорогое, так как требуется большое количество дополнительных микросхем, и будет обладать меньшим быстродействием, чем при реализации на микроконтроллере. Поэтому мы остановимся на реализации устройства на микроконтроллере

2.1 Обоснование достаточности аппаратных средств и программных ресурсов

Данное устройство будет реализовано на микроконтроллере AVR фирмы ATMEL , так как они наиболее распространённые и доступные по цене. Для реализации данного устройства достаточно использовать 8-ми разрядный микроконтроллер ATmega16, который по своим параметрам вполне удовлетворяет всем требованиям проекта и имеет запас программных и аппаратных средств для введения дополнительных функций и усовершенствования данного специализированного процессора.

AT mega16 обладает следующими характеристиками:

· 8-разрядный высокопроизводительный AVR микроконтроллер с малым энергопотреблением

· Прогрессивная RISC архитектура

1. 130 высокопроизводительных команд, большинство команд выполняется за один тактовый цикл,

2. 32 8-разрядных рабочих регистра общего назначения

Полностью статическая работа

3. Производительность приближается к 16 MIPS (при тактовой частоте 16 МГц)

4. Встроенный 2-цикловый перемножитель

· Энергонезависимая память программ и данных

1. 16 Кбайт внутрисистемно программируемой Flash памяти (In-System Self-Programmable Flash) :

-обеспечивает 1000 циклов стирания/записи

- дополнительный сектор загрузочных кодов с независимыми битами блокировки

- Внутрисистемное программирование встроенной программой загрузки

- Обеспечен режим одновременного чтения/записи (Read-While-Write)

2. 512 байт EEPROM:

- Обеспечивает 100000 циклов стирания/записи

3. 1 Кбайт встроенной SRAM

- Программируемая блокировка, обеспечивающая защиту программных средств пользователя

· Интерфейс JTAG (совместимый с IEEE 1149.1)

· Программируемый последовательный USART

· Последовательный интерфейс SPI (ведущий/ведомый)

· Специальные микроконтроллерные функции

1.Сброс по подаче питания и программируемый детектор кратковременного снижения напряжения питания

2.Встроенный калиброванный RC-генератор

3. Внутренние и внешние источники прерываний

4. Шесть режимов пониженного потребления: Idle, Power-save, Power-down, Standby, Extended Standby и снижения шумов ADC

· Выводы I/O и корпуса

32 программируемые линии ввода/вывода

40-выводной корпус PDIP и 44-выводной корпус TQFP

· Рабочие напряжения 4,5 - 5,5 В

· Рабочая частота 0 - 16 МГц

· Корпус: DIP-40

Контролер имеет три внешних прерывания, подключаемых к одному из портов. Обмен информацией с УКС можно производить по интерфейсу SPI.

2.2 Выбор и обоснования режимов работы узлов микроконтроллера

Для ввода и вывода данных будем использовать интерфейс SPI (Serial Peripheral Interface) - полнодуплексный скоростной синхронный трёхпроводной интерфейс. В используемом МК интерфейс SPI реализован на старших выводах порта В.

SPI в реализации Atmel имеет четыре задаваемые программно скорости передачи, может передавать байты от старшего к младшему биту и наоборот, обнаруживает ошибки пакета.

За работу интерфейса отвечают 3 регистра:

· Регистр SPCR - регистр управления

SPIE - разрешение прерывания по окончанию передачи.

SPE - SPI включен. Если установлен этот бит, то выводы #SS, MISO,

MOSI и SCK работают как выводы SPI, иначе - как простые выводы порта.

DORD - направление передачи данных. Если установлен, то передача идёт с младшего бита, если сброшен - со старшего.

MSTR - если установлен, контроллер работает как Master, если сброшен - как Slave. Управляется также выводом #SS, если он настроен на ввод - при подаче "0" на #SS бит MSTR сбрасывается.

CPOL - определяет уровень на выходе SCK в режиме ожидания - SCK = CPOL

CPHA - если установлен, передача и приём бита производится по обратному фронту, если сброшен - по прямому.

SPR1, SPR0 - делитель тактовой частоты (F - частота генератора контроллера).

SPR1SPR0Частота

00F/4

01F/16

10F/64

11F/128

· Регистр SPSR - регистр состояния

· Регистр SPDR - регистр данных

Также мы испольуем линии порта D, на выводы которого подаются внешние прерывания – PD2(INT0) и PD3(INT1) .

Для задания работы портов используются регистры DDR и PORT, соответствующих портов. Режимы работы портов приведены в таблице1.

В те моменты, когда устройство не востребовано, будем переводить его в спящий режим Power Down, выход из которого осуществляется по прерыванию. Данный режим работы описан в таблице 2.

Прерывания будем обрабатывать по переднему фронту, для этого занесём соответствующее значение в регистр MCUCR.

Похожие работы

... элементов, глобальное пространство имен, а также лавинообразную первоначальную загрузку сети. Таким образом ОСРВ SPOX имеет необходимые механизмы для создания отказоустойчивой распределенной операционной системы реального времени, концепция построения которой описана в главе 2. 4.3 Аппаратно-зависимые компоненты ОСРВ Модули маршрутизации, реконфигурации, голосования реализованы как аппаратно- ...

... ; - показывать, за счет каких структурных особенностей достигается увеличение производительности различных вычислительных систем; с этой точки зрения, классификация может служить моделью для анализа производительности. 1.12 Классификация Дазгупты Одним из последних исследований по классификации архитектур, по-видимому, является работа С. Дазгупты, вышедшая в 1990 году. Автор ...

... БД, куда по необходимости могут заноситься и логические представления (взаимосвязи) (внешние модели). До загрузки среды БД желательно реализовать её экспериментальный прототип, или построить её модель. На основе прототипа можно получить приемлемую оценку эксплуатационных характеристик БД, в том числе заранее спрогнозировать увеличение увеличение объёма БД и числа её функций. Применение полной БД ...

... преодолеть присущие архитектуре х86 ограничения (различная длина инструкций). В случае использования инструкций различной длины, чипы 4-го поколения могут одновременно обрабатывать 1 команду, процессоры 5-го поколения (Pentium) - 2 команды. И только микропроцессор AMD5k86 способен обрабатывать до 4 инструкций за такт. Использование раздельного КЭШа инструкций и данных (объем КЭШа инструкций ...

0 комментариев