Навигация

Проектирование технологии ИМС

4. Проектирование технологии ИМС.

Основные правила проектирования топологии полупроводниковых микросхем с изоляцией р-n-переходом

Важнейший этап проектирования полупроводниковой микросхемы заключается в преобразовании ее электрической схемы в топологию. Сущность разработки топологии микросхем состоит в определении взаимного расположения элементов на подложке. Разработка топологии не сводится к размещению элементов на подложке. Этот процесс должен осуществляться так, чтобы обеспечить оптимальное расположение элементов, при котором уменьшается влияние паразитных эффектов, присущих полупроводниковым микросхемам. Поэтому одной из основных задач при разработке топологии микросхемы является выбор критерия оптимальности размещения элементов. В настоящее время при разработке топологии полупроводниковых микросхем с однослойной металлизацией обязательными считаются следующие критерии: минимизация общей суммарной длины соединений; минимизация числа пересечений межэлементных соединений.

Как уже отмечалось, разработка топологии микросхем производится в несколько этапов. После расчета геометрических размеров активных и пассивных элементов приступают к разработке эскиза топологии микросхем, который вычерчивается от руки в произвольном масштабе, но с сохранением приближенного соотношения габаритных размеров элементов. При разработке эскиза топологии в первую очередь определяют число изолированных областей (карманов), которые при изоляции обратносмещенным р-n-переходом создают с помощью разделительной диффузии акцепторных примесей. Таким образом, изолированная область представляет собой область n-типа, которая соответствует коллектору транзистора. Анализируя принципиальную электрическую схему, определяют число коллекторов, имеющих различные потенциалы. Этим числом в основном и обусловлено число необходимых изолированных областей.

При разработке эскиза топологии микросхем площади изолированных областей делают как можно меньшими. Это позволяет, во-первых, реализовать на пластине большое количество микросхем и, во-вторых, уменьшить паразитные емкости переходов коллектор – подложка, влияющих на их параметры. Минимальная площадь изолированной области зависит от геометрических размеров размещаемых в ней элементов, а также расстояний, которые необходимо выдерживать между краем изолированной области и элементом и между элементами. В свою очередь, геометрические размеры областей самих элементов микросхем (эмиттера, коллектора, базы и т. д.) определяются требованиями, предъявляемыми к их электрическим характеристикам и параметрам, а также технологическими возможностями.

Минимальное расстояние между областями элементов (топологические зазоры) определяют с учетом следующих факторов, возникающих в рабочем режиме микросхем: расширения обедненной области р-n-переходов; паразитного взаимодействия между областями. Кроме того, необходимо учитывать, что реальные размеры структурных элементов, а следовательно, и топологические зазоры между областями элементов зависят от ухода p-n-перехода под окисел, т. е. от эффекта боковой диффузии. Очевидно, что для определения топологических зазоров нужно учесть погрешности, присущие определенному технологическому процессу изготовления микросхем.

Технологические погрешности в основном возникают при проведении фотолитографических процессов, а также при диффузии. Ошибка, обусловленная процессом фотолитографии, состоит из неточностей, возникающих при изготовлении фотошаблонов, из размерной ошибки проявленного изображения, связанной с режимом экспонирования, и размерной ошибки, возникающей при травлении SiO2, а также из-за неточности совмещения фотошаблона с подложкой. Топологические зазоры должны быть оптимизированы, так как при неоправданно малых топологических зазорах может произойти перекрытие отдельных областей, например области разделительной диффузии и базовой области, вследствие чего схема не будет функционировать. В этом случае возрастает также паразитное взаимодействие между областями элементов. В частности, может возникнуть паразитный транзистор со структурой база – коллектор – область разделительной диффузии. Чем меньше зазор база – подложка, тем больше коэффициент усиления по току у этого паразитного латерального транзистора. С другой стороны, завышение топологических зазоров приводит к увеличению площади, занимаемой микросхемой. Например, при завышении топологических зазоров всего лишь на 0,5 мкм площадь транзистора возрастает приблизительно на 12 мкм2, а если микросхема содержит 50 транзисторов, то площадь, занимаемая микросхемой, увеличивается на 600 мкм2, что представляет весьма существенный вклад в потери площади.

Необходимо отметить, что обычный подход при расчете топологических зазоров, т.е. с точки зрения наихудшего случая, применяется довольно редко, чаще всего используется метод, основанный на сборе статистического распределения погрешностей. Топологические ограничения непрерывно изменяются по мере совершенствования технологических процессов изготовления микросхем.

Конструирование и выбор структуры интегральных транзисторов. Процесс проектирования планарных транзисторов состоит из следующих этапов: для данной серии ИМС или нескольких серий, исходя из быстродействия, потребляемой мощности, необходимой степени интеграции, задают электрические параметры транзисторов как базовых элементов ИМС; выбирают технологию производства ИМС, параметры материала подложки и эпитаксиального слоя, приближенно оценивают основные размеры конструкции транзисторов в плане и в сечении, проводят расчет электрических параметров транзисторов и, если они существенно отличаются от заданных, путем ступенчатого изменения конструктивных размеров и последующих расчетов подбирают геометрию всех областей транзисторной структуры, не выходя за рамки технологических ограничений. Затем осуществляют экспериментальную проверку проведенной работы: разрабатывают комплект фотошаблонов, выпускают опытные партии транзисторных структур и измеряют их характеристики. Если параметры транзисторов отличаются от заданных, то методом последовательных приближений путем изменения размеров транзисторных областей и их характеристик, корректировки режимов технологических процессов добиваются необходимого соответствия параметров.

Расчет транзисторов сложен, трудоемок, без применения ЭВМ практически невыполним, точность его невысока. Поэтому часто этап расчета конструкции транзисторов опускают, акцентируя внимание на экспериментальном этапе. При этом на предприятии, выпускающем ИМС, формируют банк интегральных транзисторов с широким спектром характеристик. При таком подходе задача конструктора ИМС состоит в подборе конкретных типов интегральных транзисторов для данной ИМС в соответствии с ее электрической схемой.

1. Сначала выбирают физическую структуру различных областей транзистора. Удельное сопротивление подложки должно быть большим (1—10 Ом · см), что обеспечивает высокое напряжение пробоя и малую емкость обратно смещенного p-n-перехода коллекторной подложки.

2. При выборе уровня легирования коллекторной области (эпитаксиального слоя) необходимо выполнить ряд противоречивых требований: для получения малого последовательного сопротивления коллектора уровень его легирования должен быть высокий, а для получения малой емкости и высокого напряжения пробоя перехода база – коллектор – низкий.

Обычно удельное сопротивление эпитаксиального слоя выбирают равным 0,1 – 0,5 Ом см, а толщину – в пределах 2 – 15 мкм. Использование тонких эпитаксиальных слоев (до 3 мкм) позволяет уменьшить паразитные емкости и увеличить плотность размещения элементов. В структурах со скрытым n+ – слоем и подлегированием области коллекторного контакта последовательное сопротивление коллектора составляет 10—50 Ом.

3. При выборе уровней легирования базовой и эмиттерной областей необходимо также учитывать несколько противоречивых требований. Так, для уменьшения паразитного сопротивления между активной областью базы и контактом к базе следует увеличивать уровень легирования базы. Однако это приводит к снижению эффективности эмиттера и уменьшению напряжения пробоя перехода база – эмиттер. Кроме того, поверхностная концентрация примеси в базовом слое не должна быть меньше 5·1016 см -3, так как на поверхности этого слоя возможно образование инверсного проводящего канала n-типа, индуцированного встроенным зарядом в окисле.

4. Высокий уровень легирования эмиттера необходим для получения большого коэффициента инжекции. Однако при уровнях легирования эмиттерной области, достигающих предела растворимости примеси в кремнии, в кристаллической решетке образуются точечные и линейные дефекты, которые значительно уменьшают время жизни носителей заряда, что, в свою очередь, приводит к уменьшению коэффициента инжекции.

5. Частотные характеристики транзисторов зависят в основном от паразитных емкостей переходов и последовательных сопротивлений его областей. Влияние паразитных параметров уменьшают конструктивно за счет максимально возможного уменьшения геометрических размеров транзистора.

6. После выбора физической структуры выбирают конфигурацию транзистора. Поскольку характеристики в значительной степени зависят от размеров различных областей транзистора, нужно учитывать, что периметр эмиттера определяет токовые характеристики транзистора, площадь эмиттера – частотные характеристики, площадь базы – емкость перехода база – коллектор и распределенное сопротивление базы, площадь коллектора – емкость перехода коллектор – подложка и последовательное сопротивление коллектора.

7. Обычно анализируют несколько типовых конфигураций транзисторов, где сплошными линиями обозначены границы диффузионных областей, а пунктирными – границы вскрытия окон в пленке двуокиси кремния для последующего формирования металлических контактов. Для микромощных схем наиболее пригодна полосковая конструкция транзистора

Взаимное расположение контактов к различным областям транзисторной структуры выбирают в зависимости от конкретного топологического рисунка микросхемы и удобства расположения выводов транзистора. Если необходимо получить малое сопротивление коллектора, применяют транзисторы с увеличенной контактной областью к коллектору. Для получения малого сопротивления базы и высокого коэффициента усиления используют конструкции с двумя контактами к базовой области. Многоэмиттерные транзисторы применяют во входных цепях схем транзисторно-транзисторной логики (ТТЛ).

На основе эскиза разрабатывают предварительный вариант топологии, который вычерчивают на миллиметровой бумаге в выбранном масштабе, обычно 100:1 или 200:1 (выбирают масштабы, кратные 100). Топологию проектируют в прямоугольной системе координат. Каждый элемент топологии представляет собой замкнутую фигуру со сторонами, состоящими из отрезков прямых линий, параллельных осям координат. Придание элементам форм в виде отрезков прямых линий, не параллельных осям координат, допустимо только в тех случаях, когда это приводит к значительному упрощению формы элемента. Например, если форма элемента состоит из ломаных прямых, составленных в виде «ступенек» с мелким шагом, рекомендуется заменить их одной прямой линией. Координаты всех точек, расположенных в вершинах углов ломаных линий, должны быть кратны шагу координатной сетки.

При вычерчивании чертежа топологии на миллиметровой бумаге принимают минимальный шаг координатной сетки, равный 0,5 мм. Можно выбрать другой шаг, но он должен быть кратным минимальному. Действительный (на кристалле) размер шага координатной сетки зависит от выбранного масштаба топологии.

При вычерчивании общего вида топологии рекомендуется использовать линии разного цвета для различных слоев ИМС: эмиттерного – черный, базового – красный, разделительного (коллекторного) – зеленый, вертикального – черный пунктирный, скрытого – зеленый пунктирный, металлизации – желтый, окна в окисле для контакта к элементам – синий пунктирный, окна в пассивирующем (защитном) окисле – синий сплошной.

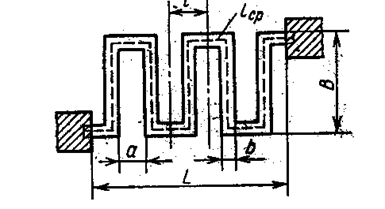

В процессе вычерчивания топологии для получения оптимальной компоновки возможно изменение геометрии пассивных элементов, например пропорциональное увеличение длины и ширины резисторов или их многократный изгиб, позволяющие провести над резистором полоски металлической разводки или получить более плотную упаковку элементов. При изменении формы пассивных элементов в процессе их размещения проводят корректировочные расчеты в соответствии с формулами и рекомендациями.

Проверка правильности разработки топологии ИМС. Последний из составленных и удовлетворяющий всем требованиям вариант топологии подвергают проверке в такой последовательности. Проверяют соответствие технологическим ограничениям: минимальных расстояний между элементами, принадлежащими одному и разным слоям ИМС.

5. Выводы о проделанной работе.

В данном курсовом проекте разработана топология интегральной микросхемы.

Разработанная мной топология соответствует электрической принципиальной схеме, учитывая топологические ограничения, и использует исходные конструктивные данные.

Для изготовления заданной схемы была выбрана планарная технология на кремниевой пластине. Изоляция элементов схемы осуществляется с помощью обратно смещённого р-n перехода.

Топология кристалла была разработана с учётом конструктивно-технологических ограничений и требований. Размеры диффузионных резисторов, использованных в схеме, были рассчитаны упрощённым методом.

Разработанная топология интегральной микросхемы не требует сложного оборудования и обеспечивает приемлемый результат для заданной схемы.

Список используемой литературы.

1. Николаев И.М., Филинюк Н.А. Интегральные микросхемы и основы их проектирования. - М.: Радио и связь. 1992 .

2. Конструирование и технология микросхем. Курсовое проектирование под ред. Коледова Л.А. - М: высшая школа. 1984

3. Степаненко И.П. Основы микроэлектроники - М.: Советское радио, 1980

4. Черчение под ред. Куликова А.С. - М: высшая школа, 1989

5. Малышева И. А. Технология производства интегральных микросхем - М: Радио и связь, 1991 .

Похожие работы

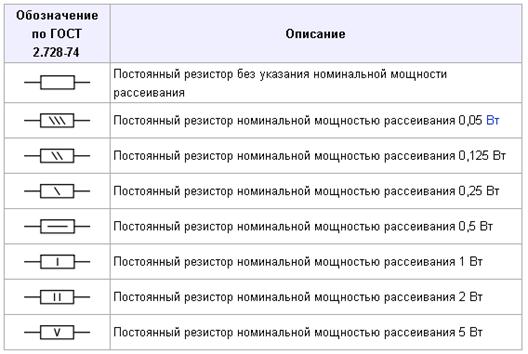

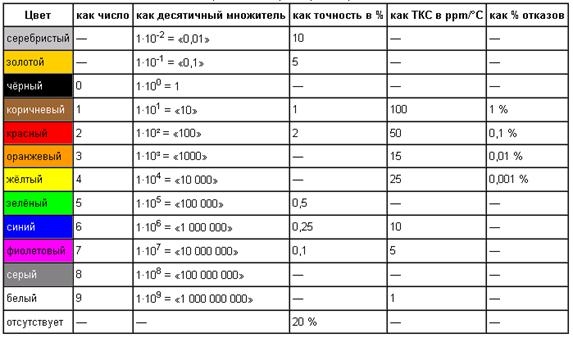

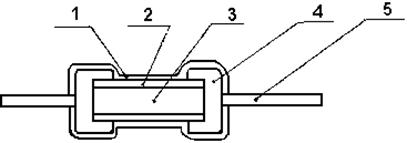

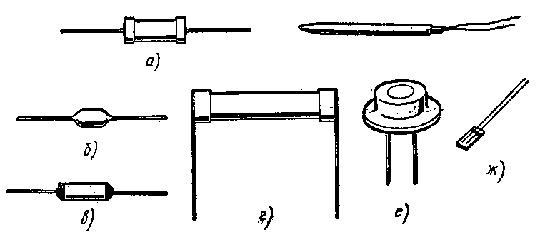

... . Конструкция резисторов, предназначенных для использования при автоматизированной сборке (монтаже) аппаратуры, должна обеспечивать механизацию и автоматизацию процессов сборки аппаратуры. 1.2.1 Требования к конструкции Общий вид, габаритные, установочные и присоединительные размеры резисторов должны соответствовать указанным в стандартах или ТУ на резисторы конкретных типов. Внешний вид ...

... . Резисторы с такими зависимостями применяются для регулировки громкости и тембра звука, яркости свечения индикаторов и др. Резисторы с характеристиками Е и И используют в регулировке стереобаланса, а резисторы с косинусными и синусными зависимостями применяют в устройствах автоматики и вычислительной техники. Отклонения от заданной кривой определяются допусками. Для резисторов общего применения ...

... , которые сегодня можно найти в продаже, практически невозможно. Поэтому приведу лишь таблицы и рисунки с данными некоторых проволочных импортных резисторов. Огнестойки проволочные резисторы серии KNP Резисторы постоянные проволочные. Заменяют собой С5-5, С5-16, С5-16МВ Характеристики: · Высокая рассеиваемая мощность, большая перегрузочная способность · Диапазон рабочих температур: -30…+ ...

... 4 ГГ ц и имеют пластинчатую форму длиной от 4 до 20 мм, шириной от 3-до 6 мм, толщиной 1 мм, либо цилиндрическую диаметром от 1,5 до 4 мм и длиной от 12 до 24 мм. Высокомегаомные и высоковольтные резисторы. Резисторы специального назначения Высоко мегаомные резисторы, отличительной особенностью которых является низкий уровень номинальной мощности рассеивания (порядка десятков милливатт и ...

0 комментариев