Навигация

4. МИКРОКОНТРОЛЛЕР.

Микроконтроллеры фирмы ATMEL с усовершенствованной RISC архитектурой обладают эффективными программно-аппаратными ресурсами для решения различных задач. Семейство микроконтроллеров AVR содержит и простые модели (AT90S1200, AT90S2313) с минимумом необходимых ресурсов, и весьма сложные модели megaAVR с существенно увеличенным объемом памяти, количеством портов ввода-вывода и других средств. Высокая эффективность микроконтроллеров AVR обеспечивается развитой системой команд, выполняющихся, как правило, за один рабочий такт, аппаратной реализацией многих стандартных функций (таймеры, модуляторы ШИМ, параллельные и последовательные порты ввода-вывода, компаратор, АЦП и др.) и возможностью внутрисистемного программирования, т.е. записи программ и данных в ПЗУ микроконтроллера непосредственно в схеме работающего устройства.

Общие архитектурные особенности и программная совместимость микроконтроллеров AVR позволяют использовать одни и те же алгоритмы и рабочие программы на разных моделях. Единственным ограничением применимости может служить только отсутствие необходимых для исполнения программ аппаратных средств в более простых моделях микроконтроллеров.

Существенной общей особенностью всего семейства AVR является использование 32 регистров общего назначения и гарвардской архитектуры с тремя раздельными адресными пространствами: памяти программ (флэш-памяти), оперативной памяти данных (ОЗУ), программируемой постоянной памяти данных (ППЗУ). Флэш-память и ППЗУ являются энергонезависимыми и, как обычно, сохраняют данные при отсутствии питающих напряжений. ОЗУ - это стандартная энергозависимая оперативная память. Система команд поддерживает стандартные операции с однобайтовыми данными, возможны определенные операции с двухбайтовыми словами и отдельными битами. Каждый из 32 восьмиразрядных регистров общего назначения может служить регистром-аккумулятором. Основной формат кодов команд - 2 байта, формат данных - 1 байт.

Управление и доступ к аппаратным средствам микроконтроллеров производятся с помощью специальных управляющих регистров - регистров ввода-вывода. Эти регистры определяют параметры и режимы работы устройств микроконтроллеров, обеспечивают необходимый обмен данными с ними. Система прерываний позволяет обслуживать программные прерывания, внутренние прерывания всех устройств микроконтроллеров через регистры ввода-вывода и внешние прерывания. Внутренние аппаратные и внешние прерывания имеют жестко закрепленные адреса векторов прерываний.

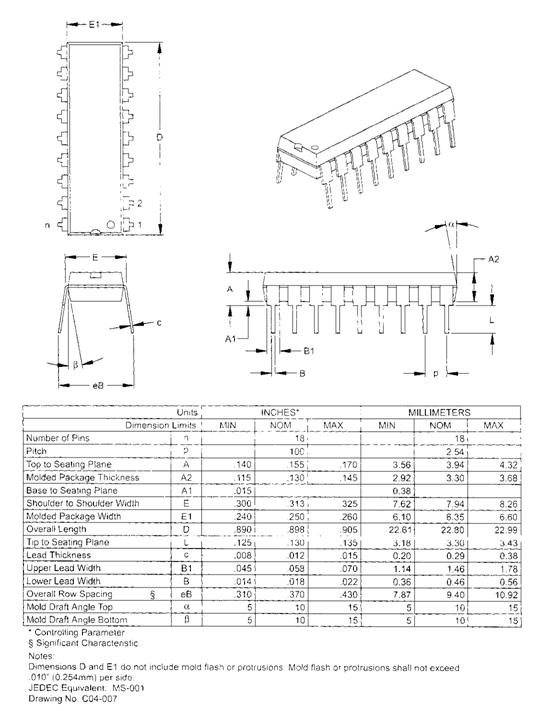

Микроконтроллер AT90S8535 (рис. 16) со 118 командами в системе команд содержит 8-разрядное арифметико-логическое устройство (АЛУ), память программ (флэш-память) объемом 8 Кбайт, электрически программируемое ППЗУ (EEPROM) объемом 0,5 Кбайт (также с возможностью внутрисистемного программирования), статическое ОЗУ объемом 0,5 Кбайт, 32 регистра общего назначения, 4 двунаправленных параллельных восьмиразрядных порта ввода-вывода, последовательный синхронный интерфейс SPI, последовательный асинхронный интерфейс UART, два восьмиразрядных и один шестнадцатиразрядный таймеры с возможностью реализации модулятора ШИМ, сторожевой таймер с автономным генератором, аналоговый компаратор, восьмиканальный АЦП.

На структурной схеме (рис.16) и в дальнейшем при описании микроконтроллеров будут использованы названия и обозначения, используемые фирмой ATMEL. Внешние выводы микроконтроллера:

VCC и GND (общий) - источник питания цифровых элементов;

AVCC, AGND (общий аналоговый), AREF - питание и опорное напряжение АЦП и его мультиплексора;

RESET - сигнал внешнего сброса (низкий уровень длительностью более 50 не), при включении питания сброс микроконтроллера производится автоматически;

XTAL1 и XTAL2 - соответственно вход и выход тактового генератора (для подключения частотозадающего кварцевого резонатора и общей синхронизации с другими устройствами), аналогичные электроды вспомогательного генератора асинхронного режима таймера 2 - выводы РС6 и РС7;

РАО-РА7, РВО-РВ7, РСО-РС7, PDO-PD7 - 32 линии ввода-вывода, объединены в 4 восьмиразрядных порта (PORTA, PORTB, PORTC, PORTD).

PORTA, PORTB, PORTC, PORTD могут использоваться как стандартные двунаправленные порты ввода-вывода либо для передачи сигналов других устройств микроконтроллера. Альтернативные функции PORTA: передача аналоговых сигналов через мультиплексор на вход АЦП. Альтернативные функции PORTB:

Рис.16. Структурная схема микроконтроллера АТ90S8535.

РВО и РВ1 - внешние входы ТО и Т1 таймеров 0 и 1 соответственно, РВ2 и РВЗ - входы AINO и AIN1 аналогового компаратора, остальные сигналы синхронного последователь- ного интерфейса SPI (PB4 - SS, PB5 - MOSI, PB6 - MISO, РВ7 - SCK). Альтернативные функции PORTC: PC6 и РС7 - вход и выход вспомогательного генератора таймера 2. Альтернативные функции PORTD: PDO и PD1 - сигналы RXD и TXD асинхронного последовательного интерфейса UART соответственно, PD2 и РВЗ сигналы внешних прерываний INTO и INT1, PD4-PD7 - сигналы ОС1В, OCIA, TCP, OC2 таймеров 1 и 2.

Запоминающие устройства микроконтроллера AT90S8535.

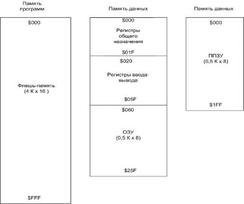

Запоминающие устройства микроконтроллера -флэш-память программ, ОЗУ, ППЗУ, регистры общего назначения и регистры ввода-вывода образуют три отдельных адресных пространства (рис. 17).

Флэш-память объемом 8 Кбайт состоит из 4 К двухбайтовых ячеек с адресами $000 - $FFF* и предназначена для хранения кодов программ и констант, в том числе и при выключенном питающем напряжении. Запись данных производится специальным программатором в процедуре внутрисистемного программирования, допустимое количество циклов перезаписи не менее 1000. Большинство кодов команд имеют 16-битовый формат, поэтому, как правило, одна ячейка флэш-памяти хранит код 1 команды или две 8-битовых константы. Адресация в этом адресном пространстве производится программным счетчиком.

В памяти данных ППЗУ (EEPROM) образует отдельное адресное пространство объемом 0,5 К однобайтовых ячеек с адресами $000 - $ IFF и хранением данных при выключении питающего напряжения. Доступ к данным в ППЗУ производится с помощью специальных регистров из файла регистров ввода-вывода; программно доступно и чтение, и запись данных. Запись данных также может производиться программатором в процедуре внутрисистемного программирования.

Третье адресное пространство является основной частью памяти данных и содержит 32 регистра общего назначения с адресами $000 - $01F, 64 регистра ввода-вывода с адресами $020 - $05F и ОЗУ объемом 0,5 К однобайтовых ячеек с адресами $060 - $25F. Такая организация памяти данных позволяет адресовать все эти регистры как ячейки ОЗУ с известными адресами либо использовать для их адресации соответствующие обозначения или адреса в регистровых файлах. Например, регистр управления АЦП имеет адрес ОЗУ $026, адрес в файле регистров ввода-вывода $06 или символическое имя ADCSR.

Адресация ячеек памяти в третьем адресном пространстве производится стандартными способами. При прямой адресации адрес содержится в командах STS k, Rr и LDS Rd, k, где к - адрес в диапазоне $000-$25F, Rr и Rd любые из регистров общего назначения.

Рис.17. Память микроконтроллера АТ90S8535.

Косвенная адресация возможна регистрами X, Y, Z. Каждый из этих адресных регистров образован парой регистров общего назначения: X -R27-R26, Y - R29-R28, Z - R31-R30. Адресация также возможна с помощью указателя стэка (пара регистров SPH-SPL файла регистров ввода-вывода), обычно в качестве вершины стэка используется наибольший адрес ОЗУ с символическим именем RAMEND, для данного микроконтроллера - это физический адрес S25F.

Адресация регистров общего назначения стандартная: в команде указывается номер регистра (например, mov r2, r0) или присвоенное ему ранее символическое имя (например, mov r2, temp). Обращение к файлу регистров ввода-вывода производится командами in, out с использованием, как правило, символических имен (символические имена регистров ввода-вывода приведены в приложении).

Параллельные порты ввода-вывода.

Микроконтроллер содержит 32 линии ввода-вывода, объединенные в 4 двунаправленных порта (А, В, С, D). Управление каждым портом производится тремя регистрами порта из файла регистров ввода-вывода, символические имена этих регистров содержат наименование порта. Так как процедуры управления для всех портов аналогичны, рассмотрим их на примере порта А.

Регистр управления порта А с символическим именем DDRA*, адресом в файле регистров ввода-вывода $1А, адресом ОЗУ $03 А программно доступен и для чтения, и для записи и определяет направление передачи данных: 0 - ввод, 1 - вывод. Каждый бит DDRA (DDAO - DDA7) управляет соответствующей линией ввода-вывода и программируется независимо, начальное значение всех битов DDRA -- нулевое. Т.е. в процессе работы значение каждого бита не зависит от значений других битов, чтением содержимого регистра DDRA можно определить направление передачи данных по соответствующим линиям ввода-вывода в данный момент времени.

Регистр ввода данных PINA (адрес в файле регистров ввода-вывода -$19, адрес ОЗУ - $039) программно доступен только для чтения и обеспечивает считывание сигналов, поступающих в данный момент времени на соответствующие линии ввода-вывода (например, линия РА2 в режиме ввода формирует бит PINA2 регистра ввода данных). Никакого хранения данных регистр PINA не выполняет.

Регистр вывода данных PORTA (адрес в файле регистров ввода-вывода - $ 1В, адрес ОЗУ - $ОЗВ) программно доступен и для чтения, и для записи, обеспечивает хранение данных и выдачу их в режиме вывода на соответствующие линии ввода-вывода (например, PORTA4 - РА4). При чтении PORTA передает данные, ранее записанные в этот регистр для вывода.

Буферы портов в режиме вывода позволяют формировать логические сигналы с током нагрузки до 20 мА. В режиме ввода, кроме приема внешних сигналов, буферы позволяют подключать к входам портов внутренние резисторы, задавая на входах при отсутствии внешних сигналов уровень логического нуля. Например, DDA7=0 (ввод данных) при PORTA7=0 внутренний резистор буфера подключен и при отсутствии внешнего сигнала будет задавать на РА7 низкий уровень. Это позволяет устранить возможные неопределенности входных сигналов. При появлении сигнала внешнего источника уровень РА7 будет задаваться этим внешним сигналом. При PORTA7=1 внутренний резистор отключен и никакого влияния не оказывает.

Для остальных портов ввода-вывода используются такие же регистры с аналогичными именами и заменой буквы, обозначающей наименование порта. При использовании альтернативных функций портов ввода-вывода в регистрах управления должны задаваться соответствующие этим функциям направления передачи сигналов. Более детальное описание альтернативных функций будет приведено позже при описании соответствующих аппаратных средств микроконтроллера.

Последовательный интерфейс SPI.

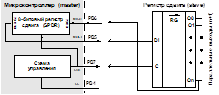

Последовательный интерфейс SPI обеспечивает синхронный ввод-вывод данных в последовательном формате через линии ввода-вывода порта В сигналами SCK (альтернативная функция линии ввода-вывода РВ7), MOSI (альтернативная функция линии РВ5), MISO (альтернативная функция РВ6), SS (альтернативная функция РВ4). Контроллер при обмене данными может работать в режиме ведущий (master) или ведомый (slave). Структурная схема, поясняющая алгоритмы работы интерфейса, приведена на рис.18. Этот же интерфейс используется для внутрисистемного программирования микроконтроллера с записью данных во флэш-память и ППЗУ.

SPI-master управляет обменом данных, формируя информационную 8-битовую последовательность на выходе MOSI, стробирующую выдачу данных последовательность тактовых импульсов на выходе SCK и одновременно может принимать на входе MISO 8-битовую последовательность, стробируемую импульсами SCK. Если РВ4 конфигурируется как выход (DDB4=1), сигнал SS не используется, и РВ4 может работать в стандартном режиме вывода. Если РВ4 конфигурируют как вход (DDB4=0), при SS=1 продолжается работа в режиме SPI-master; SS=0, поступающий от другого устройства должен рассматриваться как запрос на переход в режим SPI-slave для приема данных.

Рис. 18. Интерфейс SPI.

SPI-slave управляется последовательностью импульсов на входе SCK и принимает информационную 8-битовую последовательность, подаваемую на его вход MOSI. Параллельно с приемом данных по этим же стробирующим импульсам SCK может формироваться выходная информационная последовательность на выходе MISO. Для этого режима РВ4 должен конфигурироваться входом. При SS=0 реализуется режим SPI-slave, если SS=1, интерфейс переходит в пассивное состояние и перестает работать.

Для режима SPI-master конфигурирование порта В следующее: MISO -вход, MOSI - выход, SCK - выход, SS - вход (как вход используется только при необходимости), для режима SPI-slave: MISO - выход, MOSI - вход, SCK - вход, SS - вход (задается сигнал логического нуля для работы интерфейса). Обмен данными между SPI-master и SPI-slave производится по алгоритму кольцевого регистра сдвига (рис.18), по каждому такту SCK данные сдвигаются на один бит, после 8 тактов содержимое регистра-master и регистра-slave меняется местами. Соединение MOSI - MOSI обеспечивает передачу от SPI-master к SPI-slave, а соединение MISO - MISO используется при необходимости передачи данных в обратном направлении.

Управление интерфейсом SPI производится тремя регистрами файла регистров ввода-вывода: регистром данных - SPDR, регистром управления - SPCR, регистром состояния - SPSR. SPDR и SPCR программно доступны и для чтения, и для записи, SPSR доступен только для чтения.

SPDR служит для записи передаваемых данных и чтения данных, которые поступили в регистр сдвига. SPCR содержит 8 бит управления интерфейсом (слева в таблице символических имен старший бит).

Символические имена битов управления в регистре SPCR

![]()

SPIE - бит разрешения прерывания SPI, 0 запрещает прерывания.

SPE - бит разрешения работы; при 0 запрещены любые операции в SP1,

1 разрешает работу интерфейса.

DORD - при 1 первым передается младший бит слова данных,

при 0 -старший бит.

MSTR - при 1 определяется режим SPI-master, при 0 - режим SPI-slave.

Младшие 4 бита SPCR определяют параметры тактового сигнала

SCK:

CPOL - определяет пассивный уровень сигнала SCK в перерывах передачи данных, т.е. при 0 тактовый сигнал в пассивном состоянии интерфейса тоже нулевой.

СРНА - при 0 запись данных должна производиться каждым первым фронтом сигнала SCK после пассивного уровня, при 1 - каждым вторым фронтом сигнала после пассивного уровня.

SPR1 и SPR0 задают частоту сигнала SCK; коэффициент деления тактовой частоты микроконтроллера для интерфейса определяется этими битами следующим образом:

00 - коэффициент деления 4,

01- коэффициент деления 16,

10 - коэффициент деления 64,

11 - коэффициент деления 128.

В регистре SPSR используется только 2 старших бита. SPIF (бит 7) - флаг прерывания, WCOL (бит 6) - флаг коллизии. SPIF устанавливается в 1 после каждого цикла передачи данных или после отмены режима SPI-master сигналом SS и вызывает вектор прерывания SPI_STC (адрес вектора $00а), если бит SPIE=1 (разрешение прерывания в SPCR) и установлен флаг глобального прерывания I в регистре состояния SREG". Флаг прерывания очищается автоматически при вызове вектора прерывания SPI_STC либо одновременно с очисткой флага WCOL. Флаг коллизии устанавливается в случае чтения регистра SPDR в период передачи данных в SPI (некорректное чтение данных) и автоматически очищается одновременно с флагом SPIF после чтения регистра SPSR и последующего обращения к регистру SPDR.

Если биты в регистре управления SPCR для выбора необходимого режима заданы, запись байта данных в регистр SPDR контроллера в режиме SPI-master приводит к началу рабочего цикла интерфейса. SPI-master (рис.4) передает на MOSI данные, с входа MISO может записывать данные от SPI-slave и на выходе SCK формирует 8 импульсов, управляющих передачей байта данных. Под управлением этих же сигналов SCK SPI-slave (рис. 16) принимает данные с входа MOSI и может передавать из своего регистра SPDR данные на выход MISO.

После завершения рабочего цикла обмена данными контроллер, работающий в любом режиме, устанавливает флаг прерывания для вызова вектора прерывания SPI_STC. Подпрограмма обработки этого вектора должна выполнять операции доступа к регистрам SPI для реализации необходимых функций интерфейса. Например, чтение из SPDR поступивших в предыдущем цикле данных и запись в него новых данных для передачи в следующем цикле. К контроллеру SPI-master для обмена данными вместо второго контроллера может быть подключен и обычный регистр сдвига разрядности, соответствующей формату данных.

Таким образом, интерфейс SPI обеспечивает за один рабочий цикл и передачу байта данных из SPDR на выход, и запись в этот же регистр нового байта данных, поступивших на вход. Запуск рабочего цикла производится записью в SPI-master очередного байта данных в регистр SPDR.

7.1. Прикладная программа микроконтроллерного регулятора.

Программирование микроконтроллера начинается с внесения в ППЗУ при помощи программатора табулированных значений функции ![]() , при помощи которых определяем знак нелинейного воздействия.

, при помощи которых определяем знак нелинейного воздействия.

Словесный алгоритм функционирования микроконтроллерного регулятора:

1. Инициализация и настройка МК на ввод сигналов x1 и x2.

Порт B на вывод.

2. Измеряем текущее значение x2

3. Проверяем условие ![]()

4. Измеряем значение x1

5. Если условие в пункте 3 ложно, переходим к пункту 8,

6. Проверяем условие ![]() .

.

7. Если оно истинно, то подаём на выход линейное управляющее воздействие и переходим к пункту 2

8. Считываем ![]() и сравниваем с x1

и сравниваем с x1

9. Если ![]() , то подаём на вывод нелинейное управляющее воздействие, иначе подаём его же, но с отрицательным знаком.

, то подаём на вывод нелинейное управляющее воздействие, иначе подаём его же, но с отрицательным знаком.

Похожие работы

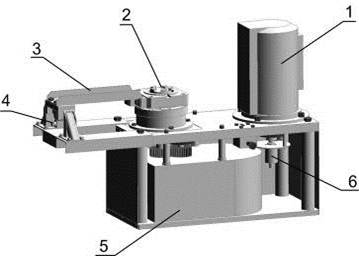

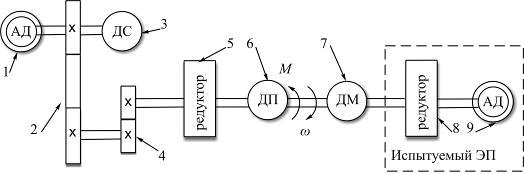

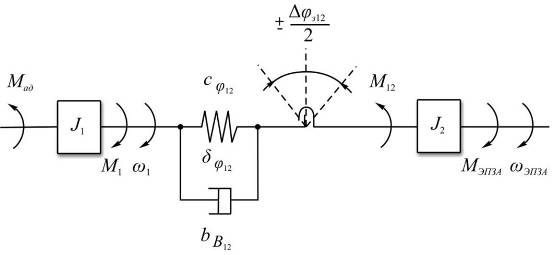

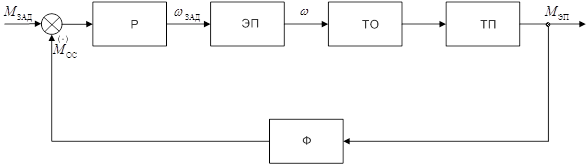

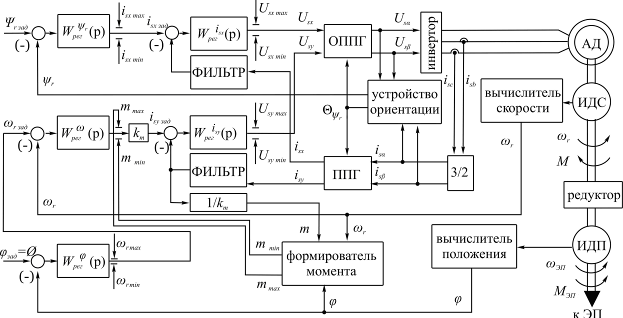

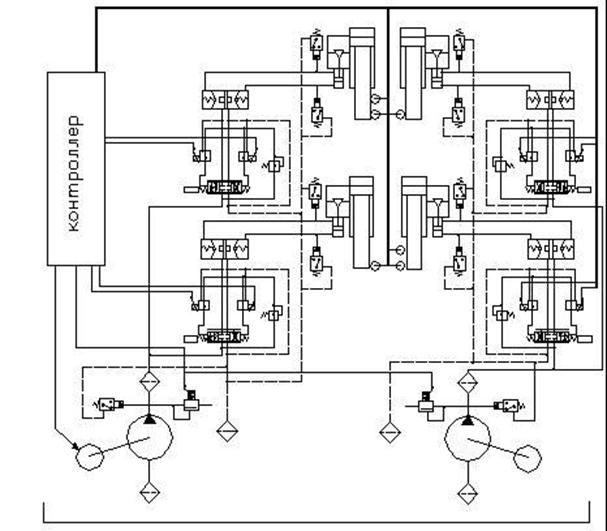

... элементов АСУ ТП 2.1 Разработка общих алгоритмов функционирования АСУ ТП. Блок – схемы алгоритма и их описание Система управления процессом испытания электропривода лифтов предназначена для управления нагрузочным электроприводом испытательного стенда в ручном или автоматическом режиме, разработана на базе микропроцессорного программируемого контроллера и выполняет следующие функции: ввод, ...

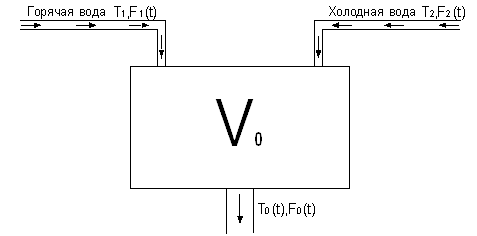

... несчастных случаев. Рассмотрен вопрос о мероприятиях по защите окружающей среды. 7. Технико-экономическое обоснование проекта 7.1. Выбор и обоснование аналога В качестве аналога автоматизированной системы управления тепличным хозяйством выберем комплекс «АСУ «Теплица» ЗАО “НАНКО”, который реализует следующие основные функции: · регистрацию и отображение значений контролируемых ...

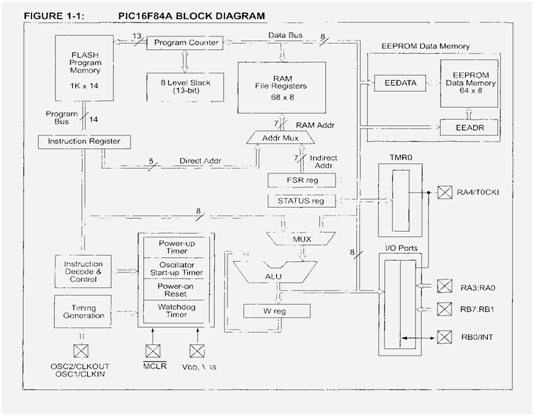

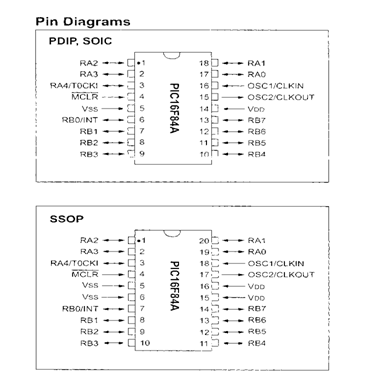

... значительно облегчают процесс изучения контроллеров РІС и написание для них программ. В данном курсовом проекте реализована микропроцессорная система на базе микроконтроллера для терморегулятора аквариума. Проект основывается на микроконтроллере PIC16F84А. 1. Описание объекта и функциональная спецификация Устройство отличается от известных измерителей температуры на DS1820 возможностью ...

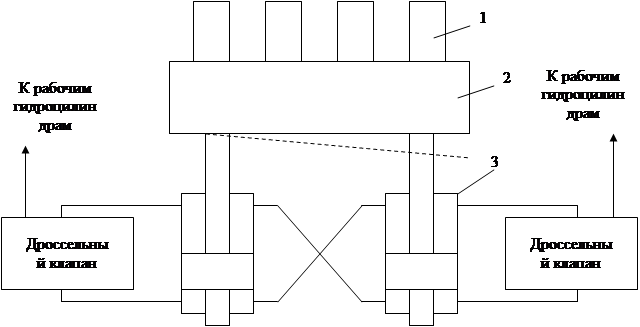

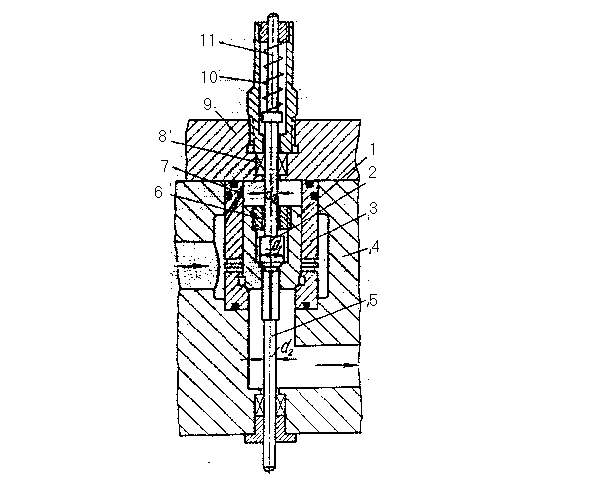

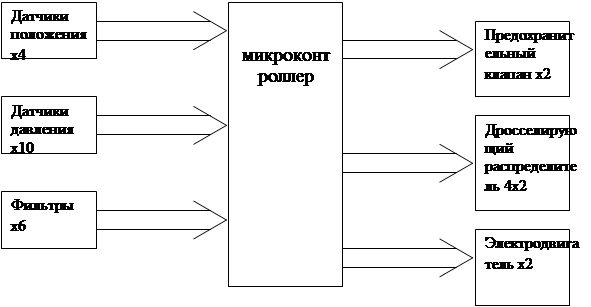

... сигнализировать о повышении давления в соответствующих точках схемы и при необходимости отключить приводной электродвигатель для предотвращения аварийных ситуаций. Первоочередной задачей при разработке системы синхронизации положения траверсы пресса является расчет управляемого впускного клапана, т.к. данный гидроаппарат не является типовым и не имеет справочных данных. После расчета впускного ...

0 комментариев