Навигация

1. Общие сведения

Семейство RISC-процессоров PowerPC в настоящее время состоит из следующих моделей: EC603e, 603e, 604e, 740, 750 (производятся фирмами Motorola и IBM).

В данной работе архитектура и работа микропроцессоров PowerPC рассматривается на базе процессора PowerPC 750. Полную документация по архитектуре и программированию всех процессоров доступна на сайтах Motorola и IBM.

750 реализует 32-разрядную архитектуру PowerPC, которая предоставляет 32-разрядную адресацию, обработку целочисленных данных (8, 16, 32 разряда), данных с плавающей точкой (32 и 64 разряда).

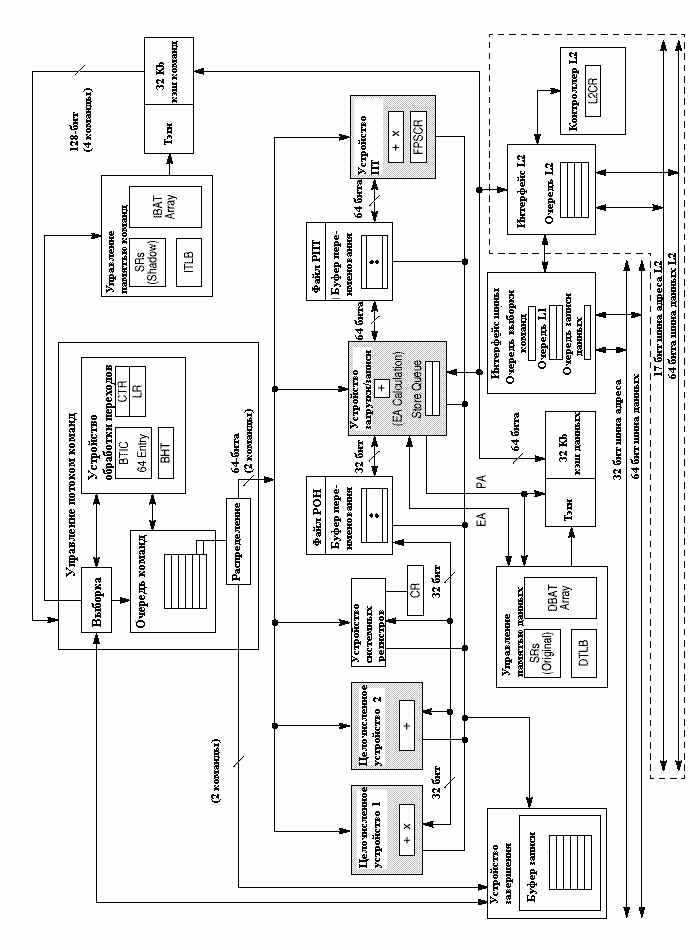

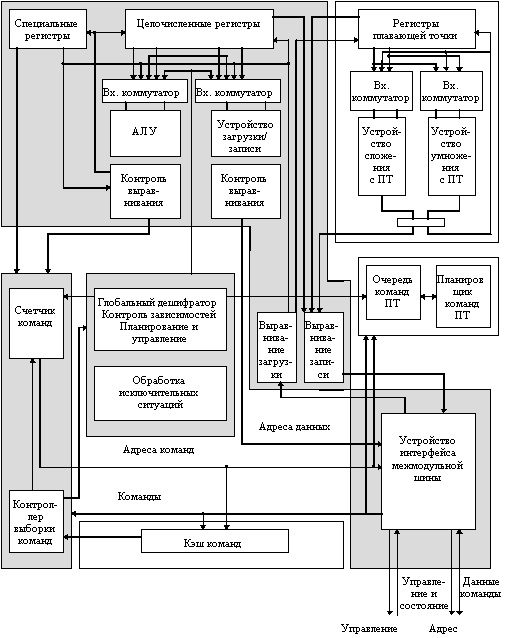

Процессор 750 состоит из следующих устройств выполнения :

· Устройство с плавающей точкой (FPU)

· Устройство обработки переходов (BPU)

· Устройство системных регистров (SRU)

· Устройство загрузки/записи (LSU)

· Два целочисленных устройства (IUs): IU1 - выполняет все команды IU2 - выполняет все команды, кроме умножения и деления

750 является суперскалярным процессором: возможна выборка четырех команд из кэша и выполнение шести команд за один такт. Большинство целочисленных команд выполняется за один такт. Выполнение команд с плавающей точкой разбиваются на три ступени. Одна команда с ПТ занимает одну ступень, таким образом одновременно FPU может выполнять три команды с плавающей точкой (32-разрядные операнды). Сложение 64-разрядных операндов выполняется за три такта, умножение и умножение-сложение за четыре.

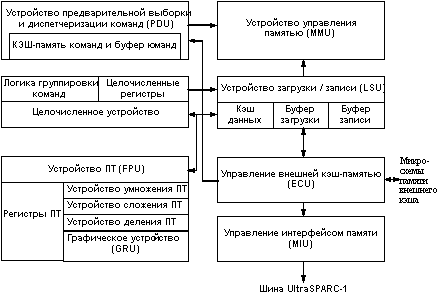

750 имеет независимый встроенный восьмиканальный, 32 Кб, физически адресуемый кэш команд и данных, а также независимые устройства управления памятью команд и данных (memory management unit, MMU). Каждое MMU имеет ассоциативный буфер TLB (DTLB и ITLB) для сохранения адресов недавно использованных страниц. Архитектурой PowerPC также определяется наличие таблиц трансляции адресов блоков памяти (block address translation array, IBAT и DBAT), Подробнее работа памяти описана в соответствующем разделе.

Кэш L2 реализован в виде встроенных памяти тэгов и внешней памяти SRAM. Доступ к внешней SRAM происходит через порт кэша L2, который поддерживает один банк памяти до 1 Мб SRAM.

750 имеет 32-разрядную адресную шину и 64-разрядную шину данных. Внешние устройства получают системные ресурсы через устройство внешнего центрального арбитра. В 750 используется MEI (modified/exclusive/invalid) протокол для синхронизации кэша и памяти и предотвращения ошибок при обращении к кэшу.

2. Архитектура и работа процессора.

2.1 Поток команд.

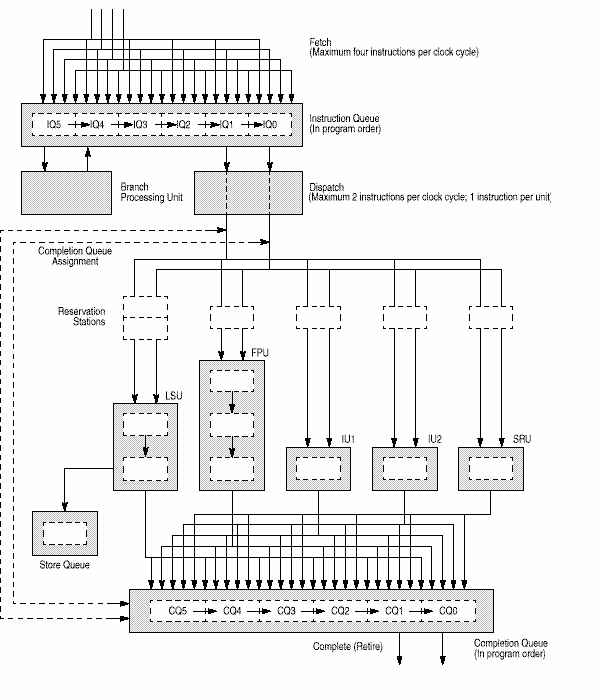

Как видно из рисунка, устройство управления потоком команд состоит из устройства последовательной выборки (fetcher), очереди из шести команд (instruction queue, IQ), устройства распределения команд и устройства обработки переходов (BPU).

Оно определяет адрес следующей команды для выборки по информации из устройства выборки и BPU.

Команда загружается из кэша команд в очередь команд. BPU извлекает команды перехода из последовательного загрузчика. Команды перехода, которые не могут быть обработаны немедленно, предсказываются с помощью специальных алгоритмов динамического или статического (определен архитектурой) предсказания переходов.

Команды перехода, не влияющие на LR или CTR (регистры, содержащие адреса переходов), удаляются из потока команд.

Команды из предсказанной ветви не завершаются, пока переход не обработан наверняка, сохраняя программную модель последовательного выполнения. Если переход был неправильным, устройство выполнения уничтожает все предсказанные пути команд и выбирает команды из правильной ветви.

2.2 Очередь команд и устройство распределения.

Очередь команд (IQ) содержит шесть команд и может быть загружена четырьмя командами за такт. Устройство выборки пытается загрузить команды на все свободные места в очереди. Все команды распределяются к соответствующим устройствам выполнения (IU1, IU2, FPU, LSU, SRU) из двух верхних позиций в очереди с максимальной скоростью две за такт. Устройство распределения проверяет зависимости регистров источника и приемника, определяет свободна ли место в очереди завершения команд, и распределяет последовательные команды по назначению.

2.3 Устройство обработки переходов.

BPU получает команды перехода из устройства выборки и делает упреждающий поиск условных ветвей для их раннего предсказания, достигая попадания в большинстве случаев.

Команды безусловного перехода или с известным условием могут быть предсказаны сразу. Для переходов с неопределенными условиями используется динамическое или статическое предсказание. Команды из предсказанной ветви выполняются, но не завершаются и не записывают результаты до подтверждения корректности перехода.

Динамическое предсказание использует таблицу истории переходов (BHT) из 512 записей, кэш который содержит по 2 бита, определяющие 4 уровня вероятности перехода. Когда динамическое предсказание запрещено переход выбирается исходя из бита в коде команды для предсказания условных переходов.

Когда переход сделан ( или предсказан), команды из остальных ветвей удаляются и загружаются команды из нужной ветви. BTIC - кэш на 64 элемента, содержащий команды из последних переходов. Когда команды находятся в BTIC, они считываются на следующем такте, иначе через один такт.

BPU содержит сумматор для вычисления адресов переходов и использует три регистра - регистр связи (LR), регистр-счетчик (CTR) и CR. BPU вычисляет точку возврата из процедуры и сохраняет результат в LR определенных команд перехода. Также в регистрах LR и CTR содержат адреса для некоторых команд обработки переходов. Из-за использования специальных регистров обработка команд переходов независима от выполнения целочисленных команд и команд с ПТ.

2.4 Устройство завершения команд.

В точке распределения команд, порядок выполнения команд поддерживается назначение команде места в очереди завершения на 6 мест. Устройство завершения отслеживает команды от распределения через устройства выполнения и возвращает результаты в порядке выполнения команд в программе из 2 нижних мест в очереди выполнения.

Команда не может быть отправлена на выполнение, если нет места в очереди завершения. Команды перехода, не модифицирующие CTR и LR удаляются из потока команд и не занимают места в очереди завершения. Команды, модифицирующие CTR и LR занимают место в очереди, но не посылаются на выполнение.

Завершение команды состоит в записи результатов в регистры (GPR, FPR, LR и CTR).

Завершенные команды удаляются из очереди завершения.

Похожие работы

... версия этого микропроцессора. Как и его предшественник, новый кристалл Alpha 21066A помимо интерфейса PCI содержит на кристалле интегрированный контроллер памяти и графический акселератор. Эти характеристики позволяют значительно снизить стоимость реализации систем, базирующихся на Alpha 21066A, и обеспечивают простой и дешевый доступ к внешней памяти и периферийным устройствам. Alpha 21066A ...

... объемов продаж рабочих станций и серверов на архитектуре MIPS в конце 1990-х гг. Silicon Graphics пришлось обратить внимание на более производительные и перспективные архитектуры. Silicon Graphics предлагает спектр серверных решений на основе архитектуры Itanium (модельный ряд Altix), а выпуск продукции архитектуры MIPS постепенно сворачивается. В 1998-2000 гг. MIPS Technologies получила свободу ...

... SunSoft. Кроме непосредственно разработки, в его функции также входило обеспечение лицензиями на ПО дистрибьюторов, OEM-партнеров и конечных пользователей. 8 июля 1987 г. — официальное рождение новой RISC/UNIX платформы: Sun представила компьютерному сообществу одновременно и открытую архитектуру SPARC, и первую базирующуюся на ней систему Sun-4/260, и ОС, и обширный набор прикладного ПО. ...

... . Некоторые характеристики транспьютеров фирмы INMOS : разрядность - 32, скорость обработки данных - 40 Мбайт/с, адресуемое пространство - 4 Гбайт. Общий обзор структур,характеристик и архитектур 32-разрядных микропроцессоров. Cтруктуры различных типов МП могут существенно различаться, однако с точки зрения пользователя наиболее важными параметрами являются архитектура, адресное пространство ...

0 комментариев