Навигация

Регистры и программная модель PowerPC

4. Регистры и программная модель PowerPC.

Архитектура PowerPC включает в себя следующие уровни:

· Уровень команд пользователя (user instruction set architecture, UISA) - определяет базовые пользовательские команды, регистры, типы данных, модели память и про-граммирования для однопроцессорной среды.

· Архитектура виртуальной среды (virtual environment architecture,VEA) - определяет модель памяти для мультипроцессорной среды, команды контроля кэша и другие па-раметры виртуальной среды.

· Архитектура операционной среды (OEA) - определяет модель управления памя-тью, регистры супервизора, требования синхронизации и модель исключений.

4.1 Регистры PowerPC.

Регистры определены на всех трех уровнях архитектуры PowerPC. Архитектура PowerPC определяет операции регистр-регистр для всех команд обработки. Источником данных является встроенные регистры или непосредственные операнды. Трехрегистровый формат команд позволяет отличать регистр результата от 2 регистров-источников, по-зволяя использовать их в других командах. Данные пересылаются между памятью и ре-гистрами только специальными командами загрузки/сохранения.

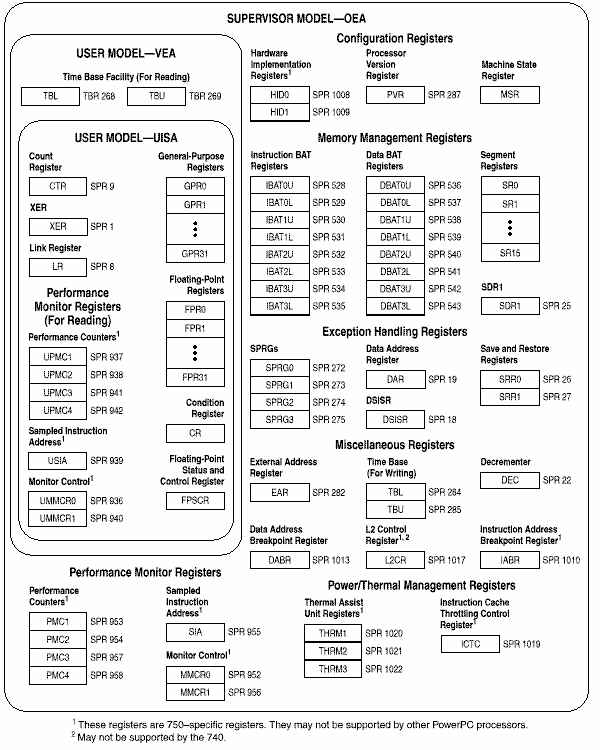

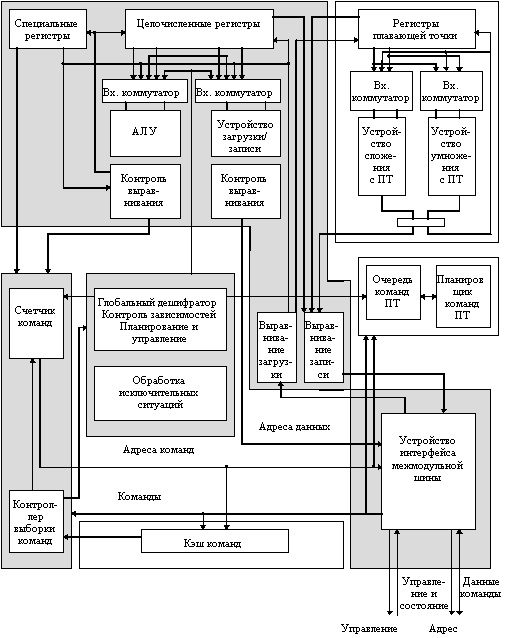

Регистры процессора 750 показаны на рисунке.

· Регистры пользовательского уровня (UISA) - доступны из всех программ с уровнями привилегий пользователя или супервизора.

Регистры общего назначения (GPR). 32 регистра GPR (GPR0-GPR31) используются как источники или приемники для целочисленных команд и предоставляют данные для формирования адреса.

Регистры с ПТ (FPR). 32 регистра FPR (FPR0-FPR31) используются как источники или приемники данных в командах с ПТ. Все регистры FPR поддерживают формат ПТ с двойной точностью.

Регистр условия (CR). 32-битный регистр, состоит из восьми 4-битных полей, CR0-CR7, отражает результаты определенных арифметических операций и обес-печивают механизм тестирования и переходов.

Регистр контроля и статуса операций с ПТ (FPSCR). FPSCR содержит тип резуль-тата операции с ПТ, все сигнальные биты исключительных ситуаций с ПТ, биты общих исключений, биты разрешения исключений и биты контроля для совмес-тимости со стандартом IEEE 754.

Остальные регистры уровня пользователя являются регистрами специального назна-чения (SPR). В PowerPC используется специальный механизм для явного доступа к SPR (команды mtspr и mfspr).

Регистр целочисленных исключений (XER). XER показывает переполнение или перенос для целочисленных операций.

Регистр связи (LR) LR предоставляет адрес перехода для команды Branch condition to link register (bclr) и может быть использован для хранения логического адреса команды следующей за переходом и связи команд, обычно для связи с про-цедурами.

Регистр-счетчик (CTR). Содержит счетчик цикла, который может уменьшатся на 1 при выполнении определенных команд перехода.

· Регистры пользовательского уровня (VEA) — PowerPC VEA определяет механизм базы времени (time base facility, TB), который состоит из двух 32-битных регистров - time base upper (TBU) и time base lower (TBL). Изменяются командами супервизора и доступны для чтения на пользовательском уровне.

· Регистры уровня супервизора (OEA) — OEA определяет регистры, используемые операционной системой для управления памятью, конфигурированием, обработкой исключений и других функций. Определены следующие 32-разрядные регистры:

Регистры конфигурации

-Регистр состояния машины (MSR). MSR определяет режимы работы

процессора.

Изменяется командами Move to machine state register (mtmsr), System Call (sc) и

Return from Exception (rfi).

-Регистр модели процессора (PVR). Регистр только для чтения, идентифицирует

модель и уровень архитектуры PowerPC процессора (0х0008 для 750).

Регистры управления памятью

-Регистры преобразования адресов блоков (BAT). PowerPC OEA включает в се-

бя массив регистров для преобразований адресов блоков, которые могут зада -

вать 4 блока для команд и 4 блока для данных. Регистры BAT реализованы по-

парно - 4 пары BAT команд (IBAT0U-IBAT3U и IBAT0L-IBAT3L) и 4 пары BAT

данных (DBAT0U-DBAT3U и DBAT0L-DBAT3L). Из-за раздельной загрузки

старших и нижних слов BAT, программа должна проверять преобразование

BAT во время загрузки регистров.

-Сегментный регистр (SR). Определены 16 32-битных сегментных регистра

(SR0-SR15). Поля сегментных регистров интерпретируется по разному в

зависимости от значения бита 0. В 750 реализованы отдельные MMU для ко-

манд и данных. Регистры SR относятся к MMU данных. Для MMU команд

используются SR в других, так называемых «теневых» сегментных регистрах.

Регистры обработки исключений

-Регистр адреса данных (DAR). После ошибки преобразования адреса DAR

содержит эффективный адрес, сгенерированный ошибочной командой.

-SPRG0-SPRG3. Используются операционной системой.

-DSISR. Определяет причину ошибки преобразования адреса.

-Регистр сохранения/восстановления статуса машины 0 (SRR0). Содержит адрес

команды выполняющейся после обработки исключения.

-Регистр сохранения/восстановления статуса машины 1 (SRR1). Сохраняет статус

машины при исключении и восстанавливает после обработки исключения.

Разные регистры.

-База времени (TB). TB является 64-битной структурой для поддержки времени и

таймера.

-Регистр декремента (DEC). 32-битный счетчик с декрементом,

предоставляющий механизм вызова исключительной ситуации декремента после

программной задержки.

Остальные регистры уровня супервизора являются регистрами специального назначения, специфическими для процессора 750. С их назначением можно ознакомится в соответст-вующей документации.

4.2 Система команд PowerPC.

Все команды имеют длину 32 бита. Форматы всех команд можно найти в документации В основном команды имеют следующие поля:

0-5 биты - код команды

6-10 биты - rD(destination) / rS(source) / crfD(результат в поле регистра CR или FPSCR) / crbD(результат как бит регистра CR или FPSCR)

11-15 биты - rA(регистр источник или приемник) / crbA(бит регистра CR как источник) / crfS(поле регистра CR или FPSCR как источник)

16-20 биты - rB(регистр как источник) / crbB(бит регистра CR как источник)

16-31 биты - SIMM(операнд со знаком) / UIMM (операнд без знака)

Целочисленные команды оперируют с операндами размером в слово (16 бит). Команды с ПТ оперируют с операндами одинарной или двойной точности. По архитектуре PowerPC ко-манды имеют длину 4 байта. Пересылка между памятью и регистрами общего назначения производится байтами, полусловами и словами. Пересылка между памятью и регистрами с ПТ производится словами и двойными словами.

Арифметические и логические команды не читают и не изменяют память. Содержимое па-мяти должно быть загружено в регистр и затем использовано в вычислениях. Загрузку и за-пись выполняют специальные команды.

Программы обращаются к памяти используя 32-битный эффективный (логический) адрес, вычисляемый процессором при обращении к памяти, выполнении перехода или выборке команды. Если при вычислении эффективный адрес превышает максимальный, адрес опе-ранда рассматривается как расположенный циклически через нулевой эффективный адрес.

Байты в памяти нумеруются последовательно, начиная с 0 и каждый номер является адресом байта. Адресом операнда в памяти является адрес его первого байта.

Для команд перехода как эффективный адрес используется непосредственный операнд или косвенно содержимое регистра связи или счетчика.

Целочисленные команды

· Арифметические.

· Сравнения. Выполняют сравнение rA с операндом UIMM, SIMM или регистром rB. Ре-зультат помещается в поле регистра CR, по умолчанию в CR0.

· Логические. Выполняют побитовые логические операции.

· Сдвига и циклического сдвига.

Команды обработки чисел с ПТ.

· Арифметические. При этом операнды с одинарной точностью преобразовываются в опе-ранды с двойной точностью.

· Сложения с суммированием.

· Округления и преобразования 64-битных чисел с ПТ двойной точности в 32-битные оди-нарной точности.

· Сравнения. Сравнение содержимого двух регистров FPR.

· Команды работы с регистром FPSCR.

· Копирования. Выполняют копирование данных из одного регистра FPR в другой.

Команды сохранения/загрузки.

Доступы к памяти в PowerPC делятся на выровненные и невыровненные. Адрес операнда считается не выровненным, если он не кратен его длине. Например, операнд длиной 12 байт выровнен по слову если его адрес кратен 4. Некоторые команды требуют выравнивания опе-рандов в памяти. Вообще, наилучшая производительность достигается, когда операнды в памяти выровнены.

· Целочисленной загрузки/сохранения. Сохранение/загрузка регистра rS/rD как байта, по-луслова, слова или двойного слова по эффективному адресу.

· Целочисленной загрузки/сохранения с реверсом байтов

· Множественной целочисленной загрузки/сохранения. Используются для пересылки блоков данных в и из регистров общего назначения, данные могут быть выровнены (множественная загрузка) или нет (загрузка строк, выполняется гораздо дольше).

· Загрузки/сохранения чисел с ПТ. Эффективный адрес генерируется используя косвенно регистр с индексной константой. Прямое сохранение в память не поддерживается. При загрузке числа одинарной точности преобразуются к двойной при загрузке в регистры FPR. При сохранении наоборот.

· Синхронизации памяти

Команды перехода и контроля потока команд

Некоторые команды перехода выполняются условно исходя из значения битов регистра CR. Если ни одна выполняемая в данный момент команда не влияет на CR, то переход решается немедленно.

· Относительный переход

· Условный переход на относительный адрес

· Переход по абсолютному адресу

· Условный переход на абсолютный адрес

· Переход по регистру связи

· Переход по регистру-счетчику

Другие команды

· Команды системных вызовов

· Команды контроля процессора. Чтение и запись CR, MSR и SPR.

· Команды синхронизации завершения операций с памятью с асинхронными событиями.

· Команды контроля памяти. Управления кэшем (пользователь и супервизор), управления сегментными регистрами (супервизор) и TLB (супервизор)

Похожие работы

... версия этого микропроцессора. Как и его предшественник, новый кристалл Alpha 21066A помимо интерфейса PCI содержит на кристалле интегрированный контроллер памяти и графический акселератор. Эти характеристики позволяют значительно снизить стоимость реализации систем, базирующихся на Alpha 21066A, и обеспечивают простой и дешевый доступ к внешней памяти и периферийным устройствам. Alpha 21066A ...

... объемов продаж рабочих станций и серверов на архитектуре MIPS в конце 1990-х гг. Silicon Graphics пришлось обратить внимание на более производительные и перспективные архитектуры. Silicon Graphics предлагает спектр серверных решений на основе архитектуры Itanium (модельный ряд Altix), а выпуск продукции архитектуры MIPS постепенно сворачивается. В 1998-2000 гг. MIPS Technologies получила свободу ...

... SunSoft. Кроме непосредственно разработки, в его функции также входило обеспечение лицензиями на ПО дистрибьюторов, OEM-партнеров и конечных пользователей. 8 июля 1987 г. — официальное рождение новой RISC/UNIX платформы: Sun представила компьютерному сообществу одновременно и открытую архитектуру SPARC, и первую базирующуюся на ней систему Sun-4/260, и ОС, и обширный набор прикладного ПО. ...

... . Некоторые характеристики транспьютеров фирмы INMOS : разрядность - 32, скорость обработки данных - 40 Мбайт/с, адресуемое пространство - 4 Гбайт. Общий обзор структур,характеристик и архитектур 32-разрядных микропроцессоров. Cтруктуры различных типов МП могут существенно различаться, однако с точки зрения пользователя наиболее важными параметрами являются архитектура, адресное пространство ...

0 комментариев