Навигация

Наличие архива данных о разработках, хранимого на долговременных машинных носителях информации

2. Наличие архива данных о разработках, хранимого на долговременных машинных носителях информации

3. Широкое применение интерактивных режимов на всех этапах проектирования

4. Обеспечение работы САПР в режиме коллективного пользования. Учитывая большую размерность залачи проектирования, большинство существующих САПР матричных БИС реализовано на высокопроизводительных ЭВМ. Однако в последнее врем все больше зарубежных фирм применяет и мини-ЭВМ

ОСНОВНЫЕ ЭТАПЫ ПРОЕКТИРОВАНИЯ Процесс проектирования матричных БИС традиционно делится на следующие укрупненные этапы: 1. Моделирование функционирования объекта проектирования. 2. Разработка топологии. 3. Контроль результатов проектирования и доработка. 4. Выпуск конструкторской документации

Рассмотрим каждый шаг в отдельности. Поскольку матричная БИС является ненастраиваемым и не ремонтоспособным объектом, то необходимо еще на этапе проектирования обеспечить его правильное функционирование. Достижение этой цели возможно двумя способами: созданием макета матричных БИС на основе дискретных элементов и его испытанием и математическим моделированием. Первый способ связан с большими временными и стоимостными затратами. Поэтому макет используется тогда, когда он специально не разрабатывается, а уже существует (например, при переходе от реализации устройств на печатных платах к матричным БИС). Второй способ требует создания эффективной системы моделирования схем большого размера, так как при моделировании необходимо учитывать схемное окружение матричных БИС, которое по числу элементов во много раз больше самой схемы

Этап разработки топологии связан с решением следующих задач: размещение элементов на БМК, трассировка соединений, корректировка топологии. Иногда в качестве предварительного шага размещения решается специальная задача компоновки (распределения элементов по макроячейкам). В этом случае возможны различные методы решения задачи размещения. Первый метод состоит в том, чтобы после компоновки размещать группы элементов, соответствующих макроячейкам, а затем размещать элементы внутри каждой макроячейки. При этом критерий оптимальности компоновки включает составляющие, определяемые плотностью заполнения макроячеек и связностью элементов макроячейки. Достоинствами этого метода являются сокращение размерности задачи размещения и сведение исходной задачи к традиционным задачам компоновки и размещения. Возможность применения традиционных методов компоновки предопределяется тем, что условие существования реализации группы элементов в макроячейке для получивших распространение БМК легко выражается через суммарную площадь элементов и отношение совместимости пар элементов. Отметим, что так как расположение элементов внутри макроячеек существенно влияет на условия трассировки соединений между макроячейками, рассмотренный метод решения задачи размещения для некоторых типов БМК может давать сравнительно низкие результаты

Другой метод размещения состоит в распределении элементов по макроячейкам с учетом координат макроячеек. В этом случае в ходе компоновки определяются координаты элементов с точностью до размеров макроячеек и появляется возможность учета положения транзитных трасс. Для матричных схем небольшой степени интеграции (до 1000 элементов на кристалле) применяются модификации традиционных алгоритмов размещения и трассировки. Для СБИС на БМК необходима разработка специальных методов

Задача корректировки топологии возникает в связи с тем, что существующие алгоритмы размещения и трассировки могут не найти полную реализацию объекта проектирования на БМК. Возможна ситуация, когда алгоритм не находит размещение всех элементов на кристалле, хотя суммарная площадь элементов меньше площади ячеек на кристалле. Это положение может быть обусловлено как сложностью формы элементов, так и необходимостью выделения ячеек для реализации транзитных трасс. Задача определения минимального числа макроячеек для размещения элементов сложной формы представляет собой известную задачу покрытия

Возможность отсутствия полной трассировки обусловлена эвристическим характером применяемых алгоритмов. Кроме того, в отличие от печатных плат навесные проводники в матричных БИС запрещены. Поэтому САПР матричных БИС обязательно включает средства корректировки топологии. При этом в процессе корректировки выполняются следующие операции: выделение линии соединяемых фрагментов; изменение положения элементов и трасс с контролем вносимых изменений; автоматическая трассировки указанных соединений; контроль соответствия результатов трассировки исходной схеме. Уже сейчас актуальной является задача перепроектирования любого фрагмента топологии. Для матричных БИС таким фрагментом может быть канал для трассировки, или макроячейка, в которой варьируется размещение элементов и др. Решение последней задачи, помимо реализации функций проектирования с заданными граничными условиями (определяемыми окружением фрагмента), требует разработки аппарата формирования подсхемы, соответствующей выделенному фрагменту

На этапе контроля проверяется адекватность полученного проекта исходным данным. С этой целью прежде всего контролируется соответствие топологии исходной принципиальной (логической) схеме. Необходимость данного вида контроля обусловлена корректировкой топологии, выполненной разработчиком, поскольку этог процесс может сопровождаться внесением ошибок. В настоящее время известны два способа решения рассматриваемой задачи. Первый сводится к восстановлению схемы по топологии и дальнейшему сравнению ее с исходной. Эта задача близка к проверке изоморфизма графов. Однако на практике для ее решения может быть получен приемлемый по трудоемкости алгоритм ввиду существования фиксированного соответствия между некоторыми элементами сравниваемых объектов. Дополнительная сложность данной задачи связана с тем, что в процессе проектирования происходит распределение инвариантных объектов (например, логически эквивалентных выводов элементов), поэтому для логически тождественных схем могут не существовать одинаковые описания и, следовательно, требуются специальные модели, отображающие инвариантные элементы. В общем случае универсальные модели для представления инвариантных элементов не известны, что и явилось одной из причин развития второго способа, согласно которому проводится повторное логическое моделирование восстановленной схемы

Функционирование спроектированной схемы мотает отличаться от требуемого не только из-за ошибок, внесенных конструктором, но и в результате образования паразитных элементов. Поэтому для более полной оценки работоспособности матричных БИС при восстановлении схемы по топологии желательно вычислять значения параметров паразитных емкостей и сопротивлений и учитывать их при моделировании на логическом и схемотехническом уровнях

Существуют причины, по которым перечисленные методы контроля не позволяют гарантировать работоспособность матричных БИС. К ним относятся, например, несовершенства моделей и методов моделирования. Поэтому контроль с помощью моделирования дополняется контролем опытного образца. Для этого на этапе лроектирования с помощью специальных программ осуществляется генерация тестов для проверки готовых БИС. Отметим, что при проектировании матричных БИС проведение трудоемкого геометрического контроля не требуется, так как трассировка ведется на ДРП, а топология элементов контролируется при их разработке

Заключительным этапом проектирования матричных БИС является выпуск конструкторской документации, которая содержит информацию (на соответствующих носителях) для управления технологическими станками-автоматами и сопроводительные чертежи и таблицы, состав и содержание которых регламентируются ГОСТами, а оформление требованиями ЕСКД. Для автоматизированного выпуска графической и текстовой документации обычно разрабатывается входной язык, который позволяет: компактно и наглядно описывать отдельные фрагменты документа; размещать отдельные фрагменты на площади документа; извлекать требуемую информацию из архива и включать ее во фрагменты документов; распечатывать требуемый документ.

Похожие работы

... (ШД), адресов (ША) и управления (ШУ). Однокристальные микропроцессоры получаются при реализации всех аппаратных средств процессора в виде одной БИС или СБИС (сверхбольшой интегральной схемы). По мере увеличения степени интеграции элементов в кристалле и числа выводов корпуса параметры однокристальных микропроцессоров улучшаются. Однако возможности однокристальных микропроцессоров ограничены ...

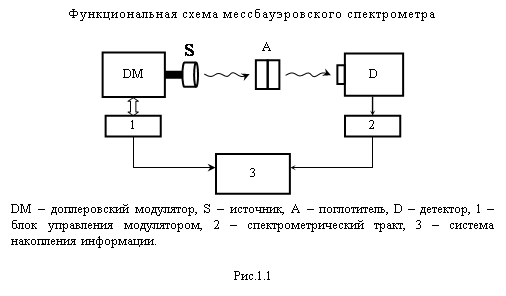

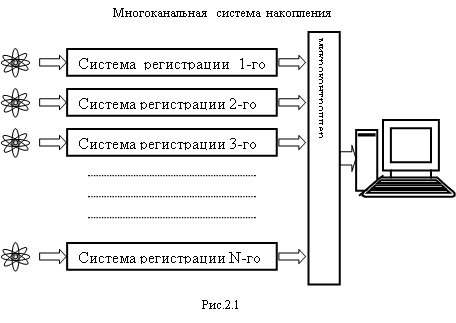

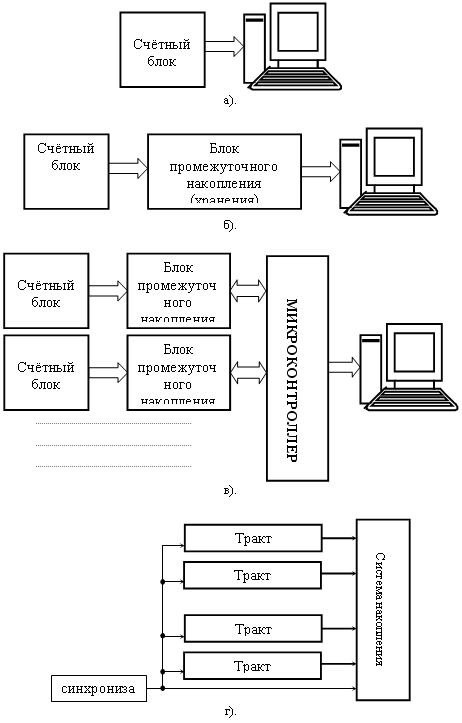

... программирование микроконтроллера, как инструмента накопления данных и управления ресурсами, с учётом необходимой и достаточной степени доступа к конечной аппаратуре. Модуль накопления для задач многомерной мессбауэровской спектрометрии спроектирован с учётом следующих условий: - Синхронизация накопителя с системой доплеровской модуляции осуществляется внешними тактовыми импульсами “старт” и ...

... рисунков в формате А0-А1 со скоростью 10-30 мм/с. Фотонаборный аппарат Фотонаборный аппарат можно увидеть только в солидной полиграфической фирме. Он отличается своим высоким разрешением. Для обработки информации фотонаборный аппарат оборудуется процессором растрового изображения RIP, который функционирует как интерпретатор PostScript в растровое изображение. В отличие от лазерного принтера в ...

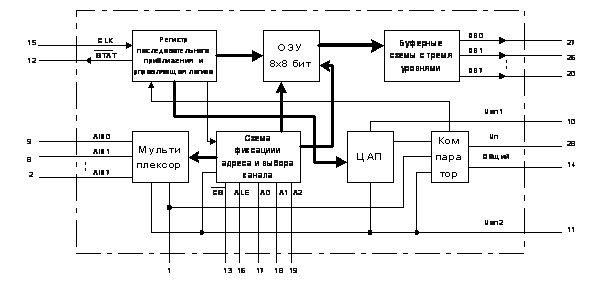

... К572ПВ4 Рис 5.5. Условное обозначение ИМС К561ЛН2 Микросхема представляет собой 6 буферных инверторов (элементов НЕ). Назначение выводов: 1, 3, 5, 9, 11, 13—входы; 2, 4, 6, 8, 10, 12 — выходы; 7 — общий; 14 — напряжение питания. Значительно упростить построение системы сбора может СБИС однокристальной аналогово-цифровой системы типа К572ПВ4. Структурная схема однокристальной системы сбора и ...

0 комментариев