Навигация

2.8.3.1 Умова припинення ділення

Якщо дільник малий порівняно з діленим, частка може показатися дуже великим і не поміститися в регістрі Q. В випадку виникнення такої ситуації, називається переповненням при діленні, частка буде неправильне, і ділення необхідно зупинити.

Раніше

було прийнято,

що ділене і

дільник – дробові

числа. Бажано,

щоб і частка

була дробовим

числом, звідки

слідує, що ділене

повинно бути

меншим дільника.

Це і є критерій,

який дозволяє

сформувати

умови припинення

ділення.

Є чотири

випадки, при

яких виникає

необхідність

зупинки ділення.

2.8.3.2 Блок-схема алгоритма

Блок-схема

послідовності

перевірки

переповнення

зображена

на

малюнку

6.11.

малюнок 6.11 Чу стр. 243

Як видно

з цієї блок-схеми,

алгоритм знаходиться

в циклі очікування,

неперервно

провіряючи

стан регістра

DSTEST. Коли вміст

регістра DSTEST стає

рівним 1, починається

виконання

основної частини

алгоритма.

Регістри BC, C і

E скидуються

в 0, регістр N

встановлюється

в 1 (при додаванні)

або скидується

в 0 (при відніманні).

Потім починається

цикл послідовного

додавання (або

віднімання).

Під час циклу

додавання (або

віднімання)

біт переноса

(або позики)

запам’ятовується

в регістрі C,

але біт суми

(різниці) ігнорується,

так як він не

використовується,

за винятком

випадку переносу

з самого лівого

біта, який

запам’ятовується

в регістрі SA.

Вміст регістра

SA використовуєтсья

оператором

DVSTOP. Крім цього,

під час додавання

(віднімання)

в регістрі E

запам’ятовується

результат

логічної операції

OR над бітом суми

(або різниці)

і E; тому якщо

вміст регістра

Е; тому якщо

вміст регістра

E дорівнює 0, то

це означає, що

модуль суми

(різниці) дорівнює

0. Цикл виконуєтсья

24 рази. Після

виходу з циклу

перевіряється

DVSTOP. Якщо виникло

переповнення,

регістр DV встановлюється

в

1. На цьому виконання

алгоритму

закінчується,

і регістр DSTEST

встановлються

в 0, щоб забезпечити

повернення

до алгоритму

ділення.

Після повернення

з перевірки

регістра DV

починається

послідовність

ділення. Якщо

вміст цього

регістру дорівнює

1, виконання

ділення припиняється.

В

протилежному

випадку починається

цикл ділення.

В цьому циклі

виконується

шість мікрооперацій,

а саме встановлення

біта Q(23) в 1 або 0,

зсув вмісту

касрегістра

AQ вліво, звернення

до послідовності

SUM – DIF, скидання

регістра OV в

0, а також збільшення

лічильника

WC і його перевірка.

Якщо вміст

регістра WC не

дорівнює 23, цикл

повторюється.

Вихід з циклу

здійснюється

при WC, рівним

23. Тоді вміст

регістру Q зсувається

вліво на 1 біт,

а частка коректується.

Корекція додається

в інвертуванні

біта Q(0) і встановленні

біта Q(23) в 1. На цьому

виконання

послідовності

ділення закінчується.

2.8.4 Алгоритм десяткового ділення

Десяткове

ділення засновано

на використанні

алгоритма

ділення з

відновленням

залишку. Початкове

ділення знаходиться

в масиві регістрів

R,

а 16-розрядне

ділене – в

касрегістрі

AQ. Після виконання

операції ділення

частка розміщується

в масиві регістрів

Q, а залишок –

в масиві регістрів

A; ділене губиться.

Переповнення

індикується

вмістом регістру

DV.

На малюнку 6.20 і 6.21 приведені блок-схеми алгоритма ділення десяткових чисел.

Вхід DDIV

Вихід

малюнок 6.20 Чу стр. 265

малюнок 6.21 Чу стр. 266

Додовання

і віднімання,

які використовуються

цим алгоритмом,

виконуються

підпослідовністю

SUM – DIF, а перевірка

переповнення

– з допомогою

підпослідовності

DSTEST. З малюнку

6.20 видно, що ділення

починається

з скидання

регістру WC в 0

і звернення

до підпослідовності

DSTEST з цілью перевірки

можливості

переповнення

при діленні.

Підпослідовніст

DSTEST, зображена

в виді блок-схеми

на малюнку

6.21, в свою чергу

починається

з звернення

до підпослідовності

SUM – DIF; останні

здійснює віднімання

дільника, який

знаходиться

в масиві регістрів

R, з старшої частини

діленого, який

знаходиться

в масиві регістрів

A. Різниця залишається

в масиві регістрів

A.

Потім виконується

перевірка, яка

дозволяє встановити,

чи не містить

регістр OV позики.

Якщо регістр

OV містить 0, значить

місце переповнення

при діленні

немає, і ділене

відновлюється

шляхом звернення

до підпослідовності

SUM – DIF, здійснюється

додавання

дільника з

масива регістрів

R і різниці масива

регістрів A. В

цей момент

виконання

підпослідовності

DSTEST закінчується

скидуванням

регістра DSTEST в

0.

Після повернення з підпослідовності DSTEST до підпослідовності ділення виконується перевірка регістра DV на рівність 1. Випадок рівності DV одиниці вказує на переповнення при діленні, що викликає припинення операції ділення. Якщо ж в індикаторі переповнення DV міститься нуль, ділення продовжується. Так як успішний вихід перевірки умови переповнення при діленні означає, що вміст масива регістрів A менше дільника, який знаходиться в масиві регістрів R, ділене в масиві регістрів A множиться на 10 шляхом зсуву на одну десяткову цифру вліво.

Як видно з малюнка 6.20, в алгоритмі є два цикла – внутрішній і зовнішній. Внутрішній цикл починаєтсья з встановлення лічильника DVC в 0. Потім починається внутрішній цикл додавання-віднімання. В внутрішньому циклі виконується звертання до підпослідовності SUM –DIF, яка здійснює додавання або віднімання, а також перевірки виникнення позики при відніманні.Якщо позики немає, лічильник DVC збільшується на 1, і керування передається до початку внутрішнього циклу. Цикл віднімання повторюється до тих пір, поки не виникне позика, на чому виконання циклу закінчується. Наявність позики означає, що вміст лічильника DVC є цифра частки; значення вмісту DVC пересилається в субрегістр Q(,8). Лічильник WC збільшується на 1, після чого його нове значення порівнюється з константою 8. Якщо вміст WC дорівнює 8, касрегістр A зсувається вліво на одну десяткову цифру, і управління передається до початку зовнішнього циклу. Зовнішній цикл повторяється до тих пір, поки лічильник WC на стане рівним 8. В цей момент визначаються знаки частки і залишку, які поміщаються в регістри SA і SQ відповідно. На цьому виконання операції ділення закінчується.

2.9 КМОН

З багатьох серій цифрових мікросхем на польових транисторах найбільше використання одержали серії мікросхем КМОП.

Скорочено

КМОП – це початкові

букви чотирьох

слів з повного

визначення:

комплементарні

польові транзистори

з структурою

металл – окисел

– напівпровідник.

Слово комплементарний

переводиться

як взаємно

доповнюючий.

Так називаються

пару транзисторів,

які подібні

по абсолютним

значенням

параметрів,

але з напівпровідниковими

структурами,

взаємно відображені

як би в вигляді

негатива і

позитива. В

біполярній

схемотехніці

– це транзистори

n-p-n і p-n-p, в польовій

p-канальні і

n-канальні. Тут

p – перша буква

від слова positive,

n

– negative.

Цікаво, що на перших етапах розвитку біполярних цифрових мікросхем пророкували широке розповсюдження комплементарних біполярних логічних елементів на n-p-n і p-n-p транзисторах. Для прикладу, якщо в ТТЛ вдалось би замінити вихідний каскад на двохтактний комплементарний, принципово збільшилась би економічність елемента. Але біполярна комплементарна транзисторна логіка не прижилась через труднощі виготовлення на кристалі великої кількості компактних по площині і високоякісних по параметрах інтегральних p-n-p транзисторів.

Нагадаємо, що в аналоговій схемотехніці, де p-n-p транзистори просто необхідні як для спрощення схемотехніки, так і для покращення властивостів підсилювачів, проблема створення добрих p-n-p транзисторів для технологів все ж таки існує. Тому реально біполярні мікросхеми ТТЛмають на виході так називаємі квазікомплементарний каскад. На кристалі роблять тільки n-p-n транзистори. Ця компромісна схема елемента ТТЛ вийшла оптимальною і перспектвною на багато десятеліть.

Перші спроби

випускати серії

простих польових

елементів,

подібний по

схемі з РТЛ, до

успіху не привели.

Логічні елементи

виходили

малошвидкодіючі,

оскільки внутрішній

опір канала

у польового

транзистора

на порядок

більше,

чим

опір між колектором

і емітером

насиченого

біполярного

транзистора.

Однополярні

мікросхеми

МОП не відрізнялись

успіхом ні

перешкодостійкістю,

ні

малою потребуючою

силою. Добрі

результати

дало використання

двополярного

інвертора, який

побудований

на комплементарній

польовій парі.

Тепер можна конкретно вибрати необхідні елементи КМОН для реалізації даної схеми, хоча при проектуванні постійно перевірялася можливість втілення схем за допомогою стандартних мікросхем серій КМОН.

2.10 Мікросхеми

Отже:

- як D-тригери беремо мікросхему К176ТМ2

14

7

Ця мікросхема містить два D-тригера і є корисна тим, що має інверсні виходи, а також має входи скидання (Reset).

Довжина тактового імпульсу не повинна бути меншою 100 нс.

Час встановлення виходів – не менше 25 нс.

Логічні мікросхеми також легко підібрати.

К561ЛА7 К561ЛА8 К561ЛА9 К561ЛИ2

Хоча мікросхеми

серії К561 і підтримують

напругу живлення

до 15 Вольт (чим

більша напруга,

тим більша

швидкодія) але

ми змушені

використовувати

мікросхеми

старішої серії

К176, максимальна

напруга живлення

яких – 9 Вольт.

Тому напруга

живлення всього

автомата не

повинна перевищувати

9 Вольт,

а в ідеальному

випадку бути

рівною цьому

значенню.

3. Розробка графу

Будується на основі автомату Мура, що використовує алгоритм двійкового ділення (паралельний пристрій). Хоча за умовою я повинна розробити пристрій для ділення десяткових чисел, але, враховуючи, що блок-схема десяткового ділення складніша у два рази (Каган) та маючи КМОН, яка є повільною, я буду використовувати двійковий алгоритм (Чу, 23) та шифратори і дешифратори. Модифікований алгоритм приведе до такого графа:

CM – дозвіл

___

CM – логічна операція множення

X0: SR(M)

Похожие работы

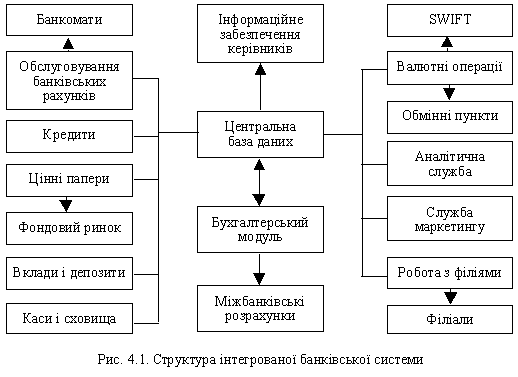

... В АБС АКБ «ПРОМІНВЕСТБАНК» ТА ОЦІНКА РІВНЯ ВРАЗЛИВОСТІ БАНКІВСЬКОЇ ІНФОРМАЦІЇ 3.1 Постановка алгоритму задачі формування та опис елементів матриці контролю комплексної системи захисту інформації (КСЗІ) інформаційних об’єктів комерційного банку В дипломному дослідженні матриця контролю стану побудови та експлуатації комплексної системи захисту інформації в комерційному банку представлена у вигляді ...

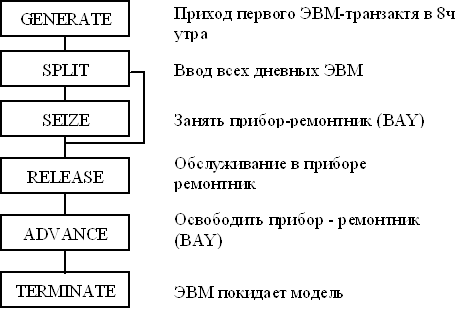

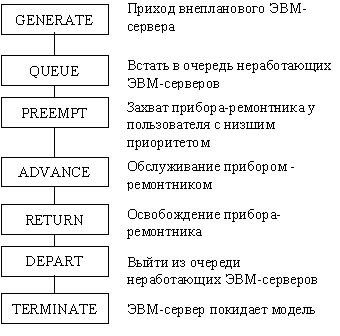

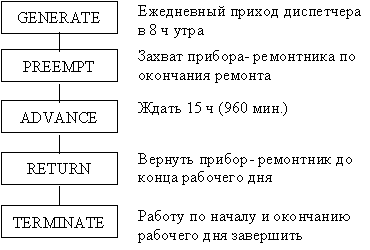

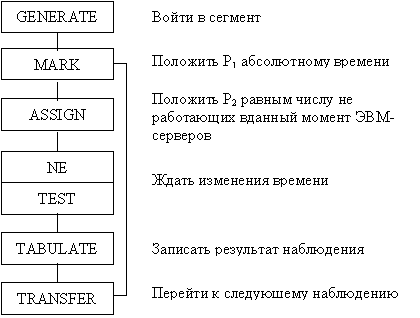

... , визначення основних характеристик одноканальних систем масового обслуговування вимагає великої обчислювальної роботи, в зв’язку з чим всі розрахунки робляться на комп’ютері. 1.2 Побудова моделей задач масового обслуговування (на прикладі роботи обчислювального центру (ОЦ)) 1.2.1 Модель для імітації виробничої діяльності ОЦ 1.2.1.1 Завдання Розробити модель для імітації виробничої ді ...

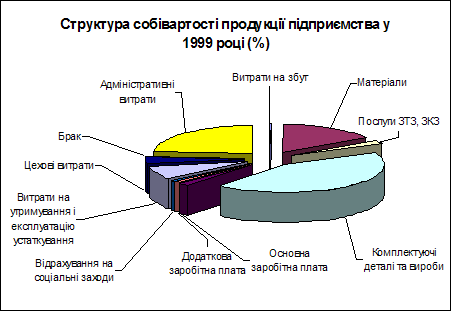

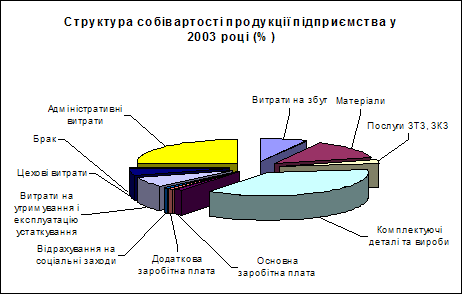

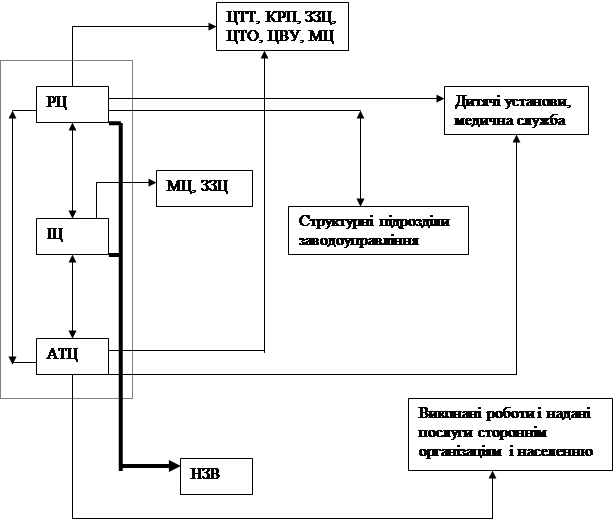

... рішень, зв’язаних із регулюванням витрат і з питань інвестиційної діяльності підприємства. Отже, управлінський облік це формування інформації для управління витратами з метою підвищення ефективності функціонування підприємства. Причому, відповідно до Закону «Про бухгалтерський облік і фінансову звітність в Україні», підприємства вправі самостійно обирати систему і форми ведення управлінського ...

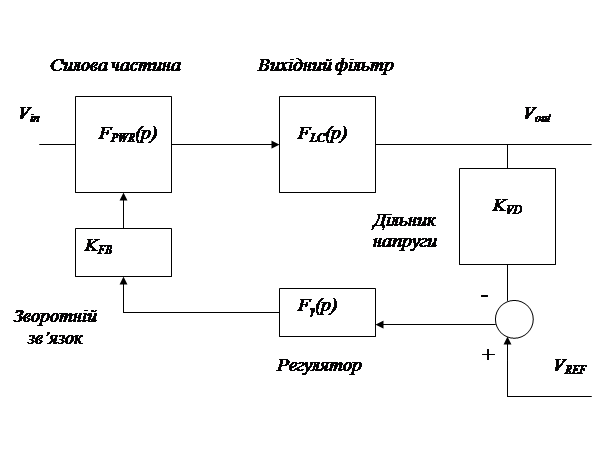

... і вказівки до дипломного проектування для студентів спеціальності “Радіотехніка” /Укл. В.О.Дмитрук, В.В.Лисак, С.М.Савченко, В.І.Правда. – К.: КПІ, 1993. – 20 с. 8. Костиков В.Г., Парфенов Е.М., Шахнов В.А. Источники электропитания электронных средств. Схемотехника и конструирование: Учебник для вузов. – 2-е изд. – М.: Горячая линия – Телеком, 2001. – 344 с.: ил. 9. Перельман Б.Л. ...

0 комментариев