Навигация

Разработка процессорного модуля

2.1 Разработка процессорного модуля

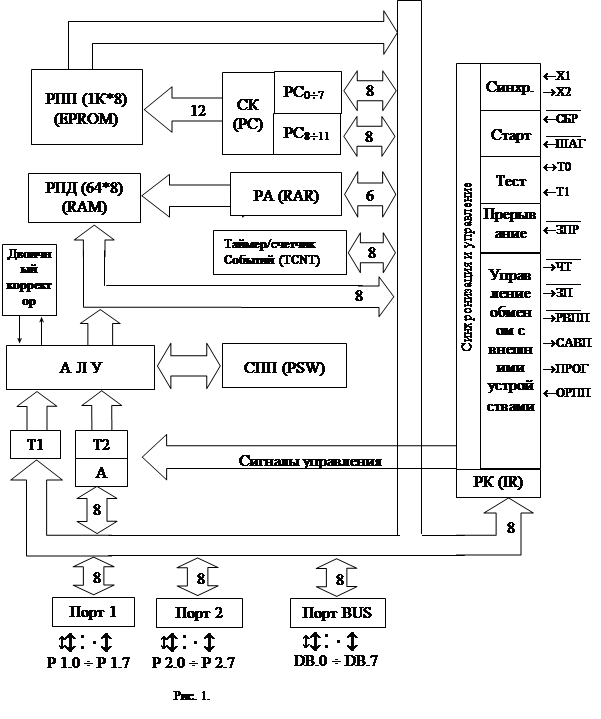

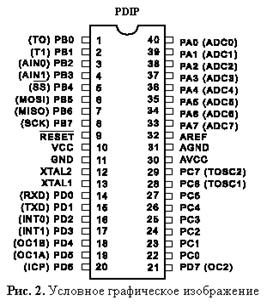

Микропроцессорное ядро (процессорный модуль, ПМ) самая важная часть микроконтроллера. Для построения процессорного ядра прежде всего решают задачу тактирования МП в 8088 это делают с помощью тактового генератора к1810ГФ4. Кроме этого необходимо произвести демультиплексирование магистрали адрес-данные и формирование шины управления в максимальном режиме с помощью контроллера системной шины.

На рисунке 15 показана схема синхронизации работы процессора и сброса. Сигналы синхронизации формируются из колебаний оснавной частоты кварцевого резонатора ZQ1, подключенного ко входам Х1,Х2, микросхемы, через конденсатор C1 емкостью 3…10 пф. Частота работы процессора 5мгц

частота кварцевого резонатора = 3F*fраб МП (при использовании к1810ГФ4). Сигнал готовности формируется при наличии на входе хотябы одного из REY1 или 2. Ко входу RES подключена время задающая RC цепочка которая формирует длительность сигнала сброса R=510 кОм,C=1 мКф (минимальная продолжительность сигнала сброс 50мкс).

Максимальный режим работы предназначен для работы ЦП с несколькими МП или сопроцессором для этого на вход микропроцессора MN\MX подается значение логической (1). Организация буферизации шины показана на рисунке 16. Регистры DD 4, DD 5, DD 6, запоминают адрес установленный микропроцессором по приходу сигнала ALE (строб адреса), на вход «строб(STB)» каждого из регистров смотри рисунок 17 “Временные диаграммы работы процессора”. Адрес устанавливается в первом цикле Т1 (выделено см. рис) и сохраняется до канца цикла.

.

Буферный усилитель DD7 усиливает сигналы шины данных в двух направлениях это нужно для обеспечения нормальной работы процессора (из за нагрузочной способности входов МП). Буферный усилитель управляется стробом данных (DEN) МП (контроллер системной шины DD12 в максимальном режиме работы МП), который подается на вход OE микросхемы DD7 в каждом машинном цикле см.(рис 18) и сигналом определяющим направление передачи данных (DT\R) он подается на вход T.

Шина управления формируется с помощью микросхемы DD12. Блок управления работает по таблице истиности (минимальный режим таблица 3). И по таблице в максимальном с помошью контроллера системной шины

Таблица 3. Алгоритм работа схемы управления

| RD | WR | M\IO | MEMR | MEMWR | IO\R | IO\WR |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 0 |

Таблица декодирования сигналов управления системного контроллера.

| S1 | S2 | S3 | Сигнал управления | Тип цикла шины |

| 0 | 0 | 0 | INTA | Подтверждение прерывания |

| 0 | 0 | 1 | IORC | Чтение ВУ |

| 0 | 1 | 0 | IOWC,AIOWC | Запись ВУ |

| 0 | 1 | 1 | ------- | Останов |

| 1 | 0 | 0 | MRDC | Выборка команды |

| 1 | 0 | 1 | MRDC | Чтение ЗУ |

| 1 | 1 | 0 | MWTC,AMWC | Запись ЗУ |

| 1 | 1 | 1 | ------- | Цикла шины нет |

CLK

t

t

ALE

t

A15-A8

t

T1 T2 T3 T4

QS0,QS1

ST0-ST1

t

A16-A19

A16-A19

D0-D7

AD0-AD7

t

ST3-ST7

A0-A7

t

RD

DT\R

t

t

DEN

MRDC IORC

t

t

A16-A19

A16-A19

ST3-ST7

AD0-AD7

A0-A7

D0-D7

t

DEN

t

t

AMWC

AIOWC

MWTC

IOWTC

t

t

Рисунок 18. Диаграммы работы микропроцессора в циклах чтения и записи данных из памяти.

2.2 Организация памяти микроконтроллера

Память микрокантроллера организована в соответствии с техническим заданием. ПЗУ-64 кбайт ОЗУ-8 кбайт. На рисунке 19 приведена карта памяти микрокантроллера. Схема блока памяти приведена на рисунке 20.

ПЗУ1(32кб)

DD8

ПЗУ2(32кб)

DD9

ОЗУ (8К)

DD9

Не используется

0000h

7FFFh

FFFFh

12000h

FFFFFh

В блоке на микросхемах DD8 DD9 построено постоянное запоминающее устройство а на DD10 построено ОЗУ статического типа каждая микрохема подключена к дешифратору адреса на ПЗУ приходят сигналы чтения с шины управления. ОЗУ управляется с помощью 3 сигналов; дешифратор адреса ,чтение и запись шины управления.

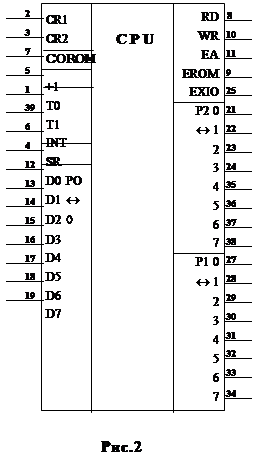

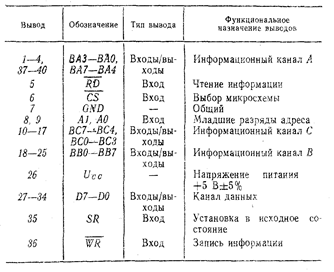

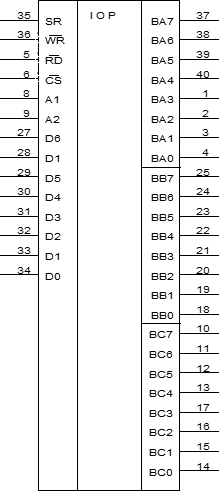

2.3 Организация параллельного порта ввода/вывода

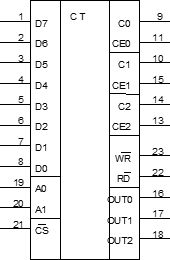

На рисунке 21 приведена схема паралельного порта ввода\вывода на микросхеме DD11. Сигналы чтения и записи подключаются к шине управления к выходам чтение из ВУ и запись в ВУ соответственно, сигнал сброса подключается к линии RESET формируемой микросхемой DD1, адресные входы подключаются соответственно к шине адреса А0,А1.

Разработка схемы дешифратора адреса памяти

Дешифратор адреса выполняет функции включателя и выключателя соответствующих данному адресу микросхем памяти блока памяти схема приведена на на рисунке 22. Дешифратор формирует 3 сигнала CS1,2,3 соответственно (ПЗУ ПЗУ ОЗУ) См.также карту памяти и таблицу двоичные и десятичные числам таблица 4.

Таблица 4

| HEX | BIN | |||||||||||||||||||

| 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 7FFFh | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| FFFFh | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 11FFFh | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Данные на буфере DD7

A15-A8

t

A16-A19

t

AD0-AD7

t

A16-A19

ST3-ST7

A0-A7

D0-D7

RD

t

t

t

t

Направление из шины данных в процессор

Рисунок 23. Диаграммы работы буферного усилителя DD7.

AD0-AD7

t

t

t

A16-A19

ST3-ST7

A0-A7

D0-D7

A16-A19

WR

t

t

t

Направление из процессора в шину данных

DT\R- (T DD7)

DEN-(OE DD7)

Данные на буфере DD7

DEN-(OE DD7)

RD ,DT\R- (T DD7)

Заключение

По полученному заданию было разработано устроуство закреплены знания работы с микропроцессорами и получен полезный опыт разработки подобных устройств.

Список литературы

1. Хвощ С.Т. и др. Микропроцессоры и микроЭВМ в системах автоматического управления: Справочник. - Л.: Машиностроение, 1987. - 640 с.

2. Щелкунов Н.Н. Микропроцессорные средства и системы - М.: Радио и связь. 1989 г.

3. Микропроцессорный комплект К1810: Структура, программирование, Применение. /Ю М. Казаринов и др. - М.: Высшая школа, 1990.

6. Петровский И.И. и др. Логические ИС К 1533, К 1554: Справочник / В двух частях. - М.: ТОО "БИНОМ", 1993.

7. Лебедев О.Н. Микросхемы памяти и их применение. - М.: Радио и связь, 1990. -303 с.

Похожие работы

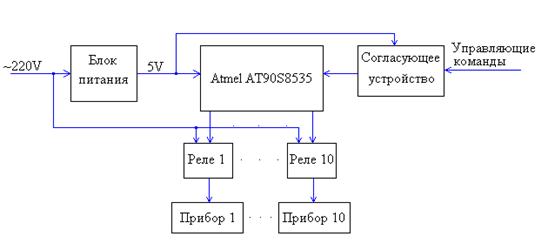

... один сигнал запроса прерывания INT для процессора, причем назначения сигналов IR0…IR3 определены внутренними потребностями контроллера. 6. Описание диаграмм временных Рассмотрим функционирование универсального одноплатного микроконтроллера на однокристальной ЭВМ по временным диаграммам, показанным в графической части лист 3, согласно схеме электрической принципиальной в графической части лист ...

... информации о количестве полученной потребителем или выработанной производителем тепловой энергии, температуре, давлении, объеме (массе) теплоносителя и о времени работы в открытых и закрытых водяных системах теплоснабжения при давлениях до 1,6 МПА (16 кгсм2) и температурах до +150 °С. Область применения - теплоэнергетика, системы коммерческого учета расхода горячей воды и тепловой энергии, ...

... ход выполнения программы и видеть соответствие между исходным текстом, образом программы в машинных кодах и состоянием всех ресурсов эмулируемого микроконтроллера. Следует отметить, что высокоуровневый отладчик обеспечивает выполнение всех своих функций только в том случае, если используется кросс-компилятор, поставляющий полную и правильную отладочную информацию (не все компиляторы, особенно их ...

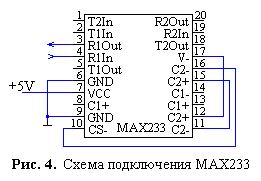

... обработчиков прерываний; · Блок обработки режимов микроконтроллера; · Блок служебных подпрограмм. Рассмотрим эти алгоритмы более подробно. Блок начальной инициализации системы содержит операции для программирования таймера, UART-интерфейса и других различных настроек. Инициализация UART заключается в установке скорости его работы в значение 9600 бит/с путём загрузки в регистр UBRR значения ...

0 комментариев