Навигация

Разработка одноплатного микроконтроллера

Министерство образования Российской Федерации

Северокавказский Государственный Технический Университет

Кафедра электроники и микроэлектроникиКурсовая работа По дисциплине :

Выполнил: студент курса группы УПЭ-991 Козидубов Е. Н.

Принял: Якушев В.М.

Ставрополь 2001

ТЕХНИЧЕСКОЕ ЗАДАНИЕ

На выполнение курсовой работы по тему "Разработка одноплатного микроконтроллера"

Микропроцессор …………………………………………… к 1810 вм 88

Заданный объем РПЗУ (кбайт) ……………………………………….. 64

Заданный объем ОЗУ (кбайт) ……………………………………….. 8

Паралельный порт ввода\вывода …………………………………… ВВ55

Включение порта ввода\вывода как ………………. внешнее устройство

Режим работы максимальный

Содержание

Введение ____________________________________________________

1. Разработка структурной схемы микроконтроллера _______________

Краткое описание микропроцессорной системы _________________

Описание структурной схемы микроконтроллера _________________

Предварительный выбор элементной базы _______________________

2. Разработка принципиальной схемы микроконтроллера ___________

2.1 Разработка процессорного модуля _____________________________

2.2 Организация памяти микроконтроллера ________________________

2.3 Организация параллельного порта ввода/вывода _________________

2.4 Разработка схемы дешифратора адреса памяти __________________

Заключение____________________________________________________

Список литературы _____________________________________________

вВЕДЕНИЕ

В данной работе будет рассмотрен один из вариантов построения микроконтроллера на основе микропроцессора 8088. С целью закркпления знаний пиобретенных на лекциях и приобретения навыков разработки микропроцессорных систем

Разрабатываемое устройство является контроллером(блок местного управления) он необходим для управления устройствами ввода вывода информации, для первичной обработки информации.

Может применятся для запуска электрических двигателей, управления выпрямительными вентелями и их группами, электромеханическими переключателями, принимать и осушествлять первичную обработку данных от информационных датчиков.

В обшем такой контроллер может найти применение в различных областях науки и техники и даже в сфере развлечения, при совместном его использовании с персональными ЭВМ и без нее тоже.

1.Разработка структурной схемы микроконтроллера

1.1Краткое описание микропроцессорной системы

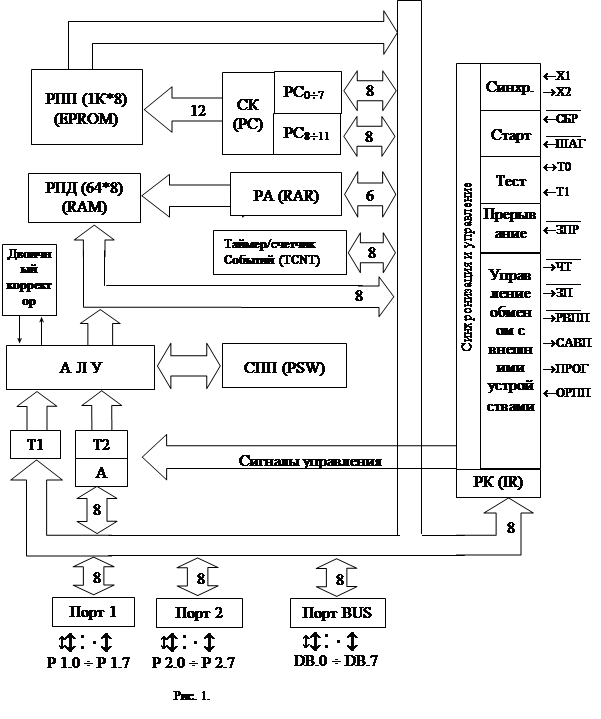

На рисунке 1. Приведина структурная схема полной микропроцессорной системы (микроконтроллер), содержащей сам микропроцессор, устроуства хранения информации блоки памяти и устройство связи системы с внешними участниками (УВВ-устройство ввода\вывода). Внешнее управление микро-ЭВМ становится возможным и при помоши системного разъема (СР) но по другим правилам в отличие от порта ввода\вывода, что расширяет возможности контроллера, с его помощью может осуществлятся связь с шинами базовой ЭВМ(например шины ISA,PCI, широко распространенных в настоящее время персональных компьютеров типа IBM).Также этот разъем может быть использован при отладке работы микропроцессорной системы в целом.

В системе присутствуют три шины (управления, адреса, данных), они представляют из себя проводные линии(проводники) соединяющие между собой составные части всей системы. Шины имеют разрядность (4,8-разрядная,16,32) т.е соответственно (4,8-проводников в линии,16,32 и.т.д).Разрядность шины может зависеть от производительности системы. Большое количество информации большая шина.

Шина данных – служет для передачи данных идуших из памяти или УВВ к процессору или из процессора в память т.е она двунаправленная.(8,16-разрядов)

Шина адреса - используется для указания адреса ячеек памяти или портов ввода\вывода, ее разрядность зависит в основном от необходимого размера памяти (8-разрядов 256 байт, 16-раз. 64кбайт, 20-разрядов 1мбайт, и т.д )

Шина управления – передает информацию УВВ или памяти о готовности микропроцессора выполнить пересылку данных. По управляющей шине передаются и сигналы которые позволяют УВВ или памяти обращатся к процессору с запросами. Разрядность этой шины зависит в основном от типа используемого процессора и количества его управляющих (используемых) сигналов.(не менее 5 - разрядов )

Из схемы видно что инициатором действий выполняемых системой является микропроцессор который вырабатывает сигналы управления и выдает их на шину управления. По ней они подаются на устройства памяти и УВВ, также процессором задается адрес выбранной ячейки памяти он подается на шину адреса и на адресные входы микросхем памяти, по шене данных информация идет в процессор или из него.

Описание структурной схемы микроконтроллера

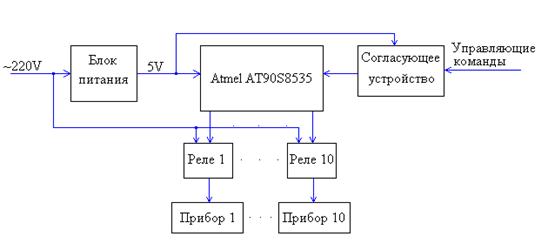

Рассмотрим работу микроконтроллера на основе схемы электрической структурной, показанной на рисунке 2.

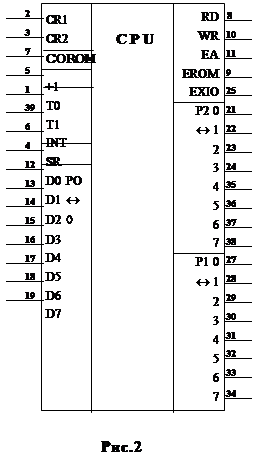

Микроконтроллер состоит из следующих узлов:

микропроцессорное ядро на основе 8088-го микропроцессора, схемы формирования сигналов управления(контроллер системной шины в максимальном режиме работы), внешнего тактового генератора,регистры шины адреса и буфера шины данных;

памяти программ ПЗУ, объемом 64 Кбайта;

ОЗУ, объемом 8 Кбайт ;

дешифратор адреса;

устройства ввода\вывода (параллельный интерфейс) ;

Схема формирования сигналов управления формирует 4 инвертированных сигнала IOWR ( внешнее устройство запись), IORD(внешнее устройство чтение),MEMR (память чтение), MEMW (память ..).В максимальном режиме (МР) работа процессора возможна только с системным контроллероим К1810ВГ88 (i8288) который формирует необходимые сигналы управления. Тактовый генератор вырабатывает синхронизирующие импульсы тактовой частоты, которые позволяют синхронизировать работу ЭВМ и остальных узлов микроконтроллера, например системный контроллер при работе процессора в МР или других микропроцессоров если система много-процессорная . Регистры адреса предназначены для фиксации старшей и младшей части адреса. Буфер шины данных выполняет усиление сигнала данных в двух правлениях

ОЗУ для временного хранения данных, основной программы расположенной в ПЗУ.

Порт ввода/вывода представляет собой двунаправленный буфер с тремя состояниями и предназначен для побайтного ввода, вывода или ввода/вывода информации.

Рисунок 2. Структурная схема микроконтроллера

Рисунок 2. Структурная схема.

Предварительный выбор элементной базы

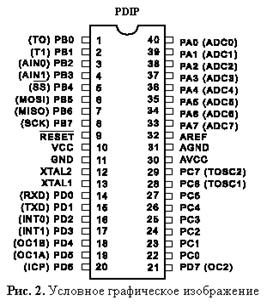

Для создания схемы электрической принципиальной микроконтроллера в курсовом проекте используются интегральные микросхемы серий К1810, К1533, КР573, К537, КР580. Серия К1810 представлена микросхемой 1810ВМ88(I8088). Она представляет собой 16-битный процессор с 8-битовой шиной данных. Микропроцессоры 8088 и 8086 имеют одинаковую архитектуру различия состоят в изменении разрядности шины данных. Условно графическое обозначение (УГО) приведено на рисунке 3. Процесс выполнения любой команды в МП состоит из следующих этапов:

1.Извлечение кода команды и операндов (если это требуется) из памяти.

2.Выполнение команды.

3.Запись результата (если это требует команда).

Как правило, эти этапы выполняются последовательно, что приводит к временной недогрузки магистралей микро ЭВМ. В МП процес выполнения, состоящий из техже этапов, выполняется в двух раздельных процессорных блоках EU и BUI и может идти паралельно. В функции блока BUI входит извлечение из памяти кода команды и их операндов, а в функции блока EU непосредственное выполнение команд. За счет паралельной работы блоков возрастает быстродействие МП БИС и магистрали микро ЭВМ используются более эффективно.

Структурная схема приведина на рисунке 4. Блок выполнения команд имеет 16-разрядный АЛУ с регистром состояний и флагом управления, а также регистры общего назначения. Все регистры и внутренние магистрали блока 16-разрядные. Блок не имеет связи с внешними магистралями. На АЛУ поступают коды команд из конвейера команд расположенного в BIU. Если в результате дешифрации кода команды в АЛУ необходимо получение одного или нескольких операндов по внешним магистралям МП БИС , то EU запрашивает BIU на получение и размещение необходимых данных в BIU. Несмотря на то что все адреса с которыми оперирует EU, 16-разрядные, BIU преобразует их так, чтобы иметь возможность адресоваться ко всему возможному адресному пространству (1 Мбайт) микропроцессорной ссистемы.

Блок сопряжения с магистралями BIU производит все пересылки данных и кодов для EU. Пересылка между МП БИС и памятью или внешними устройствами осуществляется по требованию EU. В то время как EU занят выполнением команд, блок BIU получает последующие в программе коды команд из памяти и сохраняет их в конвеере команд. Конвеер может содержать до шести (8086) и до четырех (8088) кодов команд и выдовать их в EU по мере необходимости без загрузки внешних магистралей. Коды команд подаются в EU последовательно, так как они записаны в программе. Если EU выполняет команду передачи управления, в другое место программы, то BIU очишает конвейер команд, получает код команды из нового адреса, передает его в BIU и начинает заполнять конвейер заново Если EU требует обрашения к памяти или внешнему устройству, то BIU приостанавливает процесс получения команд в конвейер и организует необходимый цикл обмена данными.

Назначение выводов в максимальном режиме работы 1810ВМ88:

Таблица 1.

| Об означение | Вывод№ | Направление | Назначение |

| AD0-AD7 | 9-16 | I\O | Шина адрес\данные двунаправленная |

| A15-A8 | 2-8. 39 | O | Шана адреса 8-15 разряды |

| A19-A16 | 35-38 | O | Адрес 16-19 разряды |

| RD | 32 | O | Строб чтения данных из памяти или ВУ |

| READY | 22 | I | Сигнал готовности ВУ или памяти к обмену данными. Если ВУ или память выдает БИС READY=0, то микропроцессор переходит в режим ожидания который будет длится до прихода READY=1 |

| INTR | 18 | I | Вход маскируемого прерывания |

| TEST | 29 | I | Вход програмной проверки готовности устройства в системе. Используется совместно с командой ожидания WAIT. Выполняя эту команду БИС проверяет уровень сигнала на входе «тест». Если TEST=0, то МП БИС переходит к выполнению следующей по порядку команды. Если TEST=1 то БИС вводит холостые такты Т1 и периодически с интервалом 5Т проверяет значение сигнала TEST. |

| NMI | 17 | I | Вход не маскируемого прерывания |

| RESET | 21 | I | Сигнал начальной установки |

| CLK | 19 | I | Вход синхронизации от внешнего генератора. Периуд синхронизации 200-500 нс (те f= 2-5 Мгц) |

| Vcc | 40 | Питающее напряжение +5в | |

| GND | Земля | ||

| MN\MX | Режим работы минимальный(1)\ максимальный(0) | ||

| LOCK | 29 | O | Блокировка шины. Сигнал на данном выходе информирует устройства системы о том что они не должны пытатся запрашивать шину |

| QS1 | 24 | O | Сигнал идентефицирующий состояние внутренней четырех байтовой очереди команд микропроцессора |

| QS0 | 25 | O | Сигнал идентефицирующий состояние внутренней четырех байтовой очереди команд микропроцессора |

| S1 | 27 | O | Сигнал состояния микропроцессора |

| S0 | 26 | O | Сигнал состояния микропроцессора |

| S2 | 28 | O | Сигнал состояния микропроцессора |

| RQ/GT0 RQ/GT1 | 30 31 | O O | Две одинаковые линии для передачи импульсных сигналов запроса \ подтверждения доступа к локальной шине(каналу) . |

| HIGH | 34 | - | Всегда «1» в максимальном режиме |

Микропроцессор выпускается в 40-выводном корпусе

Сигналы микропроцессора S1 S2 S3 выдают информацию о типе цикла шины микропроцессора . сигналы состояния подаются на контролер шины, который дешифрирует их и формирует расширенный набор управляющих сигналов. (см.таблицу)

| S1 | S2 | S3 | Тип цикла шины |

| 0 | 0 | 0 | Подтверждение прерывания |

| 0 | 0 | 1 | Чтение ВУ |

| 0 | 1 | 0 | Запись ВУ |

| 0 | 1 | 1 | Останов |

| 1 | 0 | 0 | Выборка команды |

| 1 | 0 | 1 | Чтение ЗУ |

| 1 | 1 | 0 | Запись ЗУ |

| 1 | 1 | 1 | Цикла шины нет |

QS0 QS1 Сигнал идентефицирующий состояние внутренней четырех байтовой очереди команд микропроцессора , действует в течении такта синхронизации после выполнения операции над очередью.

| QS0 | QS1 | Операции над очередью |

| 0 | 0 | Операции нет, в последнем такте небыло выборки из очереди |

| 0 | 1 | Из очереди выбран первый байт команды |

| 1 | 0 | Очередь пуста в результате выполнения команды передачи управления |

| 1 | 1 | Из очереди выбран следующий байт команды |

Работа микропроцессора 8088 в максимальном режиме во многом аналогична работе в минимальном однако изменяется значение 8 управляющих сигналов также работа процессора невозможна без контроллера системной шины i8288 (К1810ВГ88). Условно графическое обозначение приведено на рисунке. Структурная схема приведена на рисунке

Назначение выводов контроллера дано в таблице

| Обозначение | Вывод | назначение |

| S0-S3 | 20,19,18 | Входы сигналов состояния МП |

| CLK | 2 | Вход сигналов генератора тактовых импульсов |

| AEN | 6 | Сигнал управляющий выдачей командных сигналов контроллера которая осуществляется через 115 нс после поступления сигнала AEN |

| CEN | 15 | Сигнал управления выдачей командных сигналов управления DEN и PDEN. Действует как определитель возможности использования командных сигналов , формируемых контроллером системной шины при 1 контроллер функционирует нормально, а при 0 все командные сигналы удерживаются в неактивном состоянии. Это используется для для разделения адресного пространства и устранения конфликтов между внешними устройствами подключенными к системной шине. |

| IOB | 1 | Сигнал управления режимом работы контроллера при 1 задается режим режим работы с шиной ввода вывода, а при 0 с системной шиной |

| MRDC | 7 | Сигнал чтения из памяти |

| MWTC | 9 | Запись в память |

| AMWC | 8 | Опережающий сигнал записи в память |

| IORC | 13 | Ввод информации из ВУ |

| IOWC | 11 | Вывод информации в ВУ |

| AIOWC | 12 | Опережающий сигнал вывода информации в ВУ |

| DT/R | 4 | Направление передачи шинных формирователей |

| DEN | 16 | Включение шинных формирователей |

| ALE | 5 | Фиксация адресного регистра |

| MGE/PDEN | 17 | (При IOB=1) PDEN сигнал включения шинных формирователей (При IOB=0) MGE он управляет считыванием номера ведомого кантроллера прерываний, подлежащего обслуживанию |

Тактирование работы МП БИС (к1810ВМ88) осушествляет генератор тактовых импульсов к1810ГФ84 (i8284) генератор включает схемы формирования тактовых импульсов (OSK,CLK,PCLK), сигнала сброса (RESET) , и сигнала готовности (READY). Условно графическое обозначение показано на рисунке 6.

В описываемом контроллере также применяются микросхемы серии К1533, это ригистры шины адреса ИР22, буфер 1533АП6

усиливает сигналы шину данных, логические простые 1533ЛЛ1 и ЛЕ1 а также дешифратор адреса выполненый на 1533ИД7.

Ригистры шины адреса 1533ИР22 предназначены для хранения адреса установленного микропроцессором, по управляющему сигналу ALE он появляется каждый машинный цикл. Условнографическое обозначение приведено на рисунке 7.

Микросхема 1533АП6 восьмиканальный двунаправленный шинный формирователь предназначен для усиления по мощности сигналов шины данных при чтении и записи, показан на рисунке 8.

Микросхема 555ЛЛ1 - 4 логических элемента 2ИЛИ предназначена для формирования сигналов шины управления показана на рисунке 9.

Микросхема 1533ЛЕ1 - 4 логических элемента 2ИЛИ-НЕ предназначена для формирования сигналов шины управления и дешифратора адреса показана на рисунке 10.

Микросхема 1533ИД7- двоичный дешифратор на восем направлений использован для дешифрации адреса и выбора соответствующей микрасхемы памяти. На рисунке 11 токазано условно графеческое обознечение

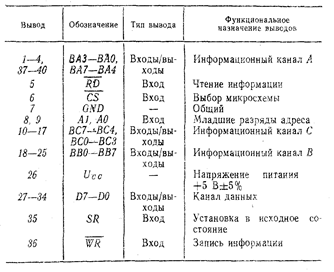

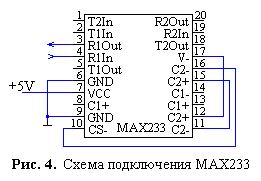

Адаптер параллельного интерфейса построен на ИМС КР580ВВ55А, который обеспечивает стробированный и нестробированный ввод/вывод информации по параллельным каналам связи, сбор данных с внешних измерительных устройств и (или) управление исполнительными устройствами.

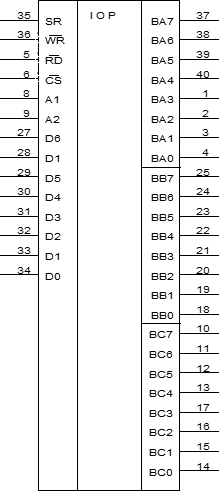

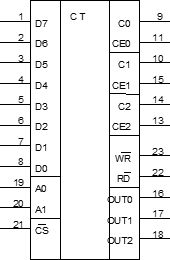

Микросхема КР580ВВ55А — программируемое устройство ввода/вывода параллельной информации, применяется в качестве элемента ввода/вывода общего назначения, сопрягающего различные типы периферийных устройств с магистралью данных систем обработки информации. Условное графическое обозначение микросхемы приведено на рис. 12. Назначение выводов приведено в таблице 2.

О

Характеристики ИМС:

Рпотр= 680 мВт:

tвыбор= 110 нс.

бмен информацией между магистралью данных систем и микросхемой КР560ВВ55А осуществляется через 8-разрядный двунаправленный трехстабильный канал данных (D). Для связи с периферийными устройствами используются 24 линии вводам/вывода, сгруппированные в три 8-разрядых канала ВА, ВВ, ВС, направление передачи информации, и режимы работы которых определяются программным способом.

Память программ хранится в постоянном запоминающем устройстве ПЗУ выполненом на ИМС К573РФ8 представляет собой многократное программируемое ПЗУ, выполненное по ЛИЗМОП технологии. Стирание записанной информации производится с помощью ультрафиолетового облучения. Емкость ИМС 573РФ8 составляет 32К*8 бит. Условное графическое обозначение микросхемы приведено на рис. 13.

Промежуточные значения вычислений хранятся в оперативном запоминающем устройстве (ОЗУ) построенном на микросхеме К537РУ17 8К*8 бит. Обозначение микросхемы приведено на рис. 14.

Микросхемы этой серии представляют из себя ОЗУ статического типа т.е. каждый элемент памяти выполнен на тригерах. Микросхема выполнена на МОП транзисторах.

В устройствах памяти на этих микросхемах для снижения потребляемой мощьности следует предусматреть возможнось автоматического переключения на источник с меньшим напряжением для хранения информации достаточно 2,2 вольта. Также может быть предусмотрен дополнительный источник питания для обеспечения автономной работы блока памяти при случайном отключении питания.

2.Разработка принципиальной схемы микроконтроллера

Похожие работы

... один сигнал запроса прерывания INT для процессора, причем назначения сигналов IR0…IR3 определены внутренними потребностями контроллера. 6. Описание диаграмм временных Рассмотрим функционирование универсального одноплатного микроконтроллера на однокристальной ЭВМ по временным диаграммам, показанным в графической части лист 3, согласно схеме электрической принципиальной в графической части лист ...

... информации о количестве полученной потребителем или выработанной производителем тепловой энергии, температуре, давлении, объеме (массе) теплоносителя и о времени работы в открытых и закрытых водяных системах теплоснабжения при давлениях до 1,6 МПА (16 кгсм2) и температурах до +150 °С. Область применения - теплоэнергетика, системы коммерческого учета расхода горячей воды и тепловой энергии, ...

... ход выполнения программы и видеть соответствие между исходным текстом, образом программы в машинных кодах и состоянием всех ресурсов эмулируемого микроконтроллера. Следует отметить, что высокоуровневый отладчик обеспечивает выполнение всех своих функций только в том случае, если используется кросс-компилятор, поставляющий полную и правильную отладочную информацию (не все компиляторы, особенно их ...

... обработчиков прерываний; · Блок обработки режимов микроконтроллера; · Блок служебных подпрограмм. Рассмотрим эти алгоритмы более подробно. Блок начальной инициализации системы содержит операции для программирования таймера, UART-интерфейса и других различных настроек. Инициализация UART заключается в установке скорости его работы в значение 9600 бит/с путём загрузки в регистр UBRR значения ...

0 комментариев