Навигация

БАЗОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

1.6.1 БАЗОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

На рисунке приведена упрощенная схема И-НЕ и его условное обозначение.

Напряжения на базах транзисторов VT1 и VT2 находятся в противофазе и, если x0*x1=1, то нижний транзистор открыт, а верхний закрыт, так как ~(x0*x1)=0 . Потенциал коллектора VT2 в этом случае примерно равен нулю и следовательно y=0. При других значениях x0 и x1 нижний транзистор закрыт, а верхний открыт и на выходе схемы - высокий уровень, т.е. схема работает как элемент И-НЕ. Выходы нескольких БЛЭ категорически нельзя соединять вместе, потому что, если n-1 элементов находятся в состоянии "1", а n-ый в состоянии "0", то n-1 транзисторов VT1 будут "сливать" (sink) токи в единственный транзистор VT2 n-го элемента. Суммарный ток может превысить допустимое значение и VT2 выйдет из строя.

1.7 ЭЛЕМЕНТ С ОТКРЫТЫМ КОЛЛЕКТОРОМЛогический элемент И-НЕ с открытым коллектором (ОК) (см.рис.2. слева) обозначается в поле элемента ромбом с чертой внизу.

К открытому коллектору снаружи могут подключаться резисторы, обмотки реле и двигателей, светодиоды и т.д. Открытые коллекторы нескольких элементов в отличие от базового логического элемента могут соединяться вместе, образуя "монтажное И" (рис.2 - справа) для прямых значений переменных т.к. y=y0*y1=1 при y0=y1=1. Иногда такую схему называют "монтажное ИЛИ", потому что y = ~(x0*x1) * ~(x2*x3) в соответствии с соотношением двойственности равно ~(x0*x1 + x2*x3) (рис.2). Логический элемент И с открытым эмиттером, обозначается ромбом, но с чертой сверху.

1.8 ЭЛЕМЕНТЫ "И - ИЛИ - НЕ" И РАСШИРИТЕЛИТакие схемы объединяют несколько элементов И, подключенных выходами к элементу ИЛИ-НЕ (рис.3). Если количества переменных a,b,..e недостаточно, используются элементы-расширители, подключаемые к входам расширения C и E (входы для открытых коллектора и эмиттера). Символ &1 обозначает функцию И, объединяемую по ИЛИ (рис.4). Здесь и далее символом * обозначаются вспомогательные входы у логических элементов.

В этих схемах, как и вообще в элементах ИЛИ, неиспользуемый вход ИЛИ д.б. подключен к 0. Поэтому, если одна из секций И незадействована, на один из ее входов необходимо подать 0. В противном случае Y всегда будет равен 0. Это особенность схем, выполненных по ТТЛ(Ш) технологии, т.к. неподключенный логический вход этих схем эквивалентен логической 1 (правда при этом ухудшаются некоторые характеристики микросхемы).

1.9 ТРИСТАБИЛЬНЫЕ ЭЛЕМЕНТЫНаряду с двумя логическими состояниями существует третье технологическое состояние, когда выход элемента отключается от внутренней схемы. При этом сопротивление между выходом и "землей" становится очень большим и выход микросхемы не оказывает никакого влияния на подключенные к нему выходы других микросхем. Выходы нескольких таких элементов также могут соединяться вместе. Такое включение , разновидность "монтажного И", применяется там, где несколько источников сигналов по очереди подключаются к входам одного или нескольких приемников, не мешая друг другу. Третье состояние называют также высокоимпедансным или Z - состоянием. Схема И-НЕ с Z-состоянием выхода приведена на рис.5. слева, а ее условное обозначение - справа.

Если сигнал ~OE=0, транзистор VT3 закрыт и включенные встречно диоды не оказывают влияния на логические выходы элемента И. Напряжения на базах транзисторов VT1 и VT2 находятся в противофазе и, если x0*x1=1, то верхний транзистор закрыт, а нижний открыт. Потенциал коллектора VT2 примерно равен нулю и следовательно y=0. При других значениях x0 и x1 нижний транзистор заперт, а верхний открыт и на выходе схемы - высокий уровень, т.е. при ~OE=0 схема работает как обычный элемент И-НЕ. Картина существенно изменится при ~OE=1. Транзистор VT3 откроется до насыщения и на базах транзисторов VT1 и VT2 потенциал опустится примерно до нуля, запирая их. Выход "y" окажется отключенным от внутренней логической схемы. На схемах тристабильные элементы обозначаются ромбом с поперечной чертой или буквой Z.

Такие элементы используются там, где необходима передача инфориации по одной линии от нескольких источников к одному или нескольким приемникам. Причем, так как линия одна, то чтобы выходы пассивных источников не искажали информацию на выходе активного источника, они должны переводиться в третье состояние. Z - состояние используется по этой причине в микросхемах памяти, шинных формирователях.

· Дополнительный инверсный вход относится к категории управляющих или функциональных. Функция входа зашифрована в его обозначении (Output Enable - разрешение выхода (~OE)),а значение активного уровня на этом входе,при котором функция выполняется, равно 1, если вход прямой, и равно 0, если вход инверсный, как на схеме.

1.10 МИНИМИЗАЦИЯ ЛОГИЧЕСКИХ ФУНКЦИЙПолученные по формуле СДНФ (12) выражение может быть преобразовано (не всегда) к виду, имеющему меньшее число переменных и операций по сравнению с исходным. Такое преобразование называется минимизацией.

Рассмотрим пример. Имеется три двоичных датчика xi. Необходимо реализовать ЛФ Yмажор принимающую значение 1, когда равны 1 значения двух и более датчиков. Такая функция называется мажоритарной. Ее таблица истинности имеет вид:

По формуле (12): Yмажор = ~x2*x1*x0 + x2*~x1*x0 + x2*x1*~x0 + x2*x1*x0. (3,5,6,7 - строчки таблицы ). Полученному выражению соответствует схема на рис.6.

Схема содержит 4 трехвходовых элемента "И" и 1 четырехвходовый элемент "ИЛИ". Нахождение минимальной формы ЛФ производится методом алгебраических преобразова- ний, с помощью таблиц Карно или машинными методами для больших проектов.

1.11 ТАБЛИЦА КАРНОТаблица Карно (ТК) это видоизмененная запись таблицы истинности. Для функции мажоритарности из последнего примера (ТК) выглядит следующим образом:

Правила построения ТК следующие: 1)Количество клеток ТК равно количеству строк таблицы истинности. 2)Слева и сверху располагаются значения аргументов. Порядок размещения аргументов таков, что в двух соседних по горизонтали и вертикали клетках отличается значение только одного аргумента (поэтому соседними считаются и клетки, находящиеся на противоположных краях таблицы). 3)В клетки заносятся соответствующие значения ЛФ. 4)Единичные клетки объединяются в прямоугольники (импликанты) по 2^i клеток. 5)Для каждого прямоугольника записывается произведение тех аргументов, которые в соседних клетках не изменяют своего значения. 6)Переменные входят в произведение в прямом виде, если их значение в соседних клетках равно 1, в противном случае в инверсном. 7)Полученные произведения складываются по ИЛИ в искомую ЛФ.

В примере имеется 3 прямоугольника - A,B,C, причем Ya = x2*x0 (x1 в соседних клетках меняет свое значение, поэтому в конъюнкцию не входит). Yb = x1*x0 и Yс = x2*x1.

Yмажор = Ya + Yb + Yc = x2*x0 + x1*x0 + x2*x1. (13)

Соответствующая схема (рис.7.) проще, чем на рис.6.

1.12 ПРЕОБРАЗОВАНИЕ ЛФ К БАЗИСУ "И-НЕ" И "И-ИЛИ-НЕ"Применяя к выражению (13) аксиому двойного отрицания (9) получим:

Yмажор =~(~( x2*x0 + x1*x0 + x2*x1)) (14)

Формуле (14) соответствует схема (рис.8,слева) в базисе И-ИЛИ-НЕ.

Применяя к выражению (14) соотношение двойственности (11) получим ~( ~(x2*x0) * ~(x1*x0) * ~(x2*x1)) . Последнему выражению соответствует схема в базисе И-НЕ (рис.8, справа).

1.13 ВРЕМЕННЫЕ ПАРАМЕРЫ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВРассмотрим реакцию инвертора на изменение входного сигнала (рис.9). Инерционные свойства инвертора приводят к задержке сигнала при его прохождении от входа к выходу.

Процесс изменения напряжения от низкого уровня L к высокому H, называется фронтом сигнала (положительным перепадом, положительным фронтом), а обратный процесс - спадом (отрицательным перепадом, отрицательным фронтом). Если существенно их взаимное расположение, то фронт может быть передним и задним. Длительность фронтов на рис.9 обозначена t1,0 - отрицательный и t0,1 - положительный.

Величинами tзд.р.0,1 и tзд.р.1,0 обозначается время задержки распространения сигнала от входа до выхода при переходе из 0 в 1 и наоборот (рис.9). Минимальная длительность импульса на входе элемента tи.мин пропорциональна среднему значению tзд.р.ср. равному полусумме tзд.р.0,1 и tзд.р.1,0. Максимальная частота входных импульсов Fмакс обратно пропорциональна tзд.р.ср. Из сказанного следует, что быстродействие элемента тем выше, чем меньше tзд.р.ср.

Определения вышеуказанных величин с их отечественными и международными обозначениями приведены в разделе обозначения некоторых параметров микросхем.

Быстродействие схемы зависит также от алгебраической формы представления ЛФ. Пусть y = a*b + c*a + d = a*(b+c)+d. Первой форме (ДНФ) соответствует схема (A), а второй - схема (B) см. рис.10.

Если среднее время задержки сигнала в каждом элементе одинаково, то 2tзд.р.ср. < 3tзд.р.ср. и двухъярусные схемы (СДНФ) в общем случае быстрее. Правда в записи со скобками может уменьшиться количество элементов и/или проводников (в схеме (B) на один провод меньше).

1.14 ПЕРЕХОДНЫЕ ПРОЦЕССЫ В ЛОГИЧЕСКИХ СХЕМАХОтличие времени задержки tзд.р. от нуля при прохождении сигнала через логическую схему может приводить к возникновению помех в выходном сигнале. Эти помехи имеют вид коротких импульсов, и в некоторых случаях приводят к серьезным сбоям в работе схем. Рассмотрим устройство на рис.11. Если элементы схемы не вносят задержки сигнала, а x0 и x1 находятся в противофазе, т.е. x0 = ~x1, то y = ~(x1 * ~x1) = 1. Если же каждый из пяти ЛЭ имеет задержку tзд.р., тогда x0' запаздывает относительно x0 на 4tзд.р. и на выходе схемы возникает незапланированный "отрицательный" импульс (интервал 1..2), сдвинутый на tзд.р. элемента И-НЕ (интервал 0..1). Процесс прохождения входных сигналов до общего выхода называется состязаниями или "гонками".

Вредный эффект "гонок" может быть устранен несколькими способами, один из которых заключается в добавлении к ЛФ дополнительного слагаемого. Пусть некоторая ЛФ равна F = x1*x2 + ~x1*x0, тогда при x2=x0=1 может появиться помеха, вызванная тем, что сигнал ~x1 задержан относительно x1 на величину задержки инвертора (см. рис.12).

Добавление лишнего импликанта (в таблице обведен точками) устраняет проблему, т.к.при критической ситуации, когда x2=x0=1, дополнительная составляющая x0*x2=1 и функция F = x1*x2 + ~x1*x0 + x0*x2 равна всегда 1 при x2=x0=1.

В устройствах индикации такие короткие помехи можно игнорировать, так как они будут незаметны для глаз.

Список литературы

СА Майоров, ВВ Кириллов, АА Приблуда Введение в микро-ЭВМ

http://www.assembler.webservis.ru

http://www.kalashnikoff.ru

http://www.vlata.com

Похожие работы

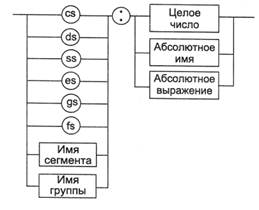

... как единое целое. Результатом вычисления выражения может быть адрес некоторой ячейки памяти или некоторое константное (абсолютное) значение. В табл. 2.2 приведены поддерживаемые языком ассемблера операторы и перечислены их приоритеты. Арифметические операторы. К ним относятся унарные операторы «+» и «-», бинарные «+» и «-», операторы умножения «*», целочисленного деления «/», получения остатка ...

... ) ФАКУЛЬТЕТ ЭЛЕКТРОНИКИ И ПРИБОРОСТРОЕНИЯ КАФЕДРА КЭС группа Э-92 ДАТА ЗАЩИТЫ апреля 1997 г. Отзыв на дипломную работу студента гр.Э-92 Сорокина Ю.В. “Разработка программы контроллера автоматически связываемых объектов для управления конструкторской документацией в среде Windows 95/NT”. Широкое использование вычислительной техники в народном хозяйстве требует увеличения производства и ...

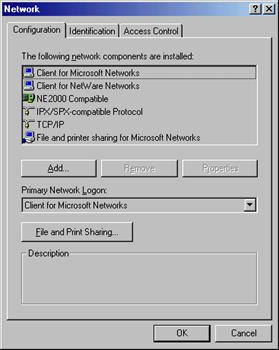

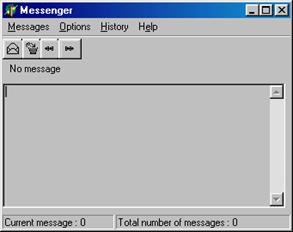

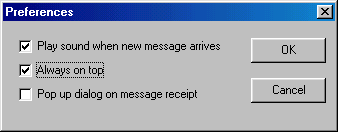

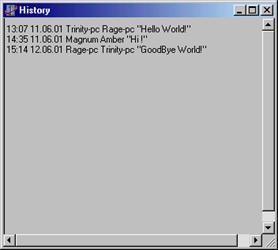

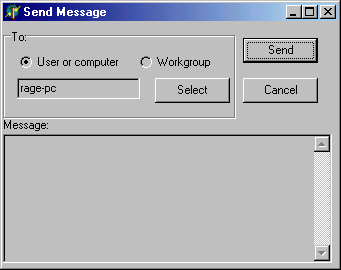

... выбрать имя в ListBox’e и нажать кнопку «OK», после чего выбранное имя автоматически отобразиться в окне получателя сообщения. Рис. 1.10. Выбор адресата получателя Поиск компьютеров в локальной сети Приведём пример кода программы, реализующую поиск компьютеров в локальной сети Microsoft. procedure TForm4. Button1Click (Sender: TObject); var Q, BufferSize: DWord; R: THandle; Buf: ^ ...

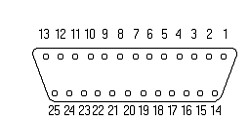

... значения низкого порога температуры, высвечивается сообщение и остается до пор, пока температура не станет выше, сохраненного значения низкого порога температуры. 3. Разработка программы Для того чтобы нам реализовать программу, необходимо компьютером считывать сигналы. Считывать сигналы будем с помощью параллельного порта LPT1. Pin In/Out Signal Name Pin In/Out Signal ...

0 комментариев