Навигация

1.1.3. Система команд

Набор команд 8086/88 включает следующие основные группы:

инструкции пересылки данных

арифметические и логические инструкции;

инструкции со строками;

инструкции передачи управления;

инструкции управления процессором;

Каждая команда имеет один или два байта инструкции, за которыми может следовать 1, 2 или 4 байты операнда. Перед кодом инструкции возможно применение префиксов CS;, DS;, ES;, SS;, указывающих на использование заданных сегментных регистров вместо обычного, префикса REP, указывающего на необходимость повтора инструкции указанное в регистре СХ число раз, и префикса LOCK, блокирующего системную шину на время выполнения инструкции. С позиции сегодняшнего дня можно считать, что система команд 16-разрядного процессора 8086/88 является подмножеством команд 32-разрядных процессоров 80х86.

. Процессоры 80186/80188

Процессоры i80186/80188 и их модификации 80С186/80С188 не представляют нового представления архитектуры: как и 8085/8088, они являются процессорами с 16-разрядной внутренней архитектурой и программно совместимыми с 8086ю Разрядность шины адреса - 20 бит, шины данных у 80186 – 16 бит, у 80188 – 8 бит. Эти процессоры имеют встроенные периферийные контроллеры прерывания, прямого доступа к памяти, трехканальный таймер и генератор синхронизации. За счет архитектурных улучшений сокращенно число тактов, требуемых для выполнения некоторых команд. Процессоры 80С186/80С188 имеют средства управления энергопотреблением, есть их модификации со встроенными последовательными портами и контроллерами регенерации динамической памяти. Встроенная периферия этих процессоров имеет программный интерфейс, не совместимы с IBM РС - спецификациями. Эти процессоры используются во встраиваемых контроллерах и компьютерах, не требующих 100% IBM – совместимости (возможно обеспечение совместимости на уровне MS DOS).

1.2.1. Математический сопроцессор 8087

Сопроцессор 8087, официально (фирмой Intel) называемый NPX (Numeric Processor eXtension), предназначен для расширения вычислительных возможностей центрального процессора (CPU) 8086/8088, 80186/80188. Его применение к системе команд 8086 добавляется 68 мнемоник, включающих арифметические, тригонометрические, экспоненциальные и логарифмические.

Процессор 80286

Процессор 80286, выпущенный в 1982 году, представляет второе поколение 16-разрядных процессоров. Он имеет специальные средства для работы в многопользовательских и многозадачных системах. Самым существенным отличием от 8086/88 является механизм управления адресации памяти, который обеспечивает четырехуровневую систему защиты и поддержки виртуальной памяти. Специальные средства предназначены для поддержки механизма переключения задач (Task switching). Процессор имеет расширенную систему команд, которая кроме команд управления защитой включает все команды 8086 н и несколько новых команд общего назначения. Процессор может работать в двух режимах:

8086 Real Address Mode – режим реальной адресации (или просто реальный режим - Real Mode), полностью совместимый с 8086. В этом режиме возможна адресация до 1 Мбайт физической памяти (на самом деле, за счет “удачной” ошибки, почти на 64 Кб больше).

Protect Virtual Address Mode – защищенный режим виртуальной адресации (или просто защищенный режим - Protect Mode). В этом режиме процессор позволяет адресовать до 16 Мбайт физической памяти, через которые при использовании страничной адресации могут отображаться до 1 Гб виртуальной памяти каждой задачи. Система команд в этом режиме также включает набор команд 8086, расширенный для обеспечения аппаратной реализации функций супервизора многозадачной ОС и виртуальной памяти. Переключение в защищенный режим осуществляется одной командой (с предварительно подготовленными таблицами дескрипторов) достаточно быстро. Обратное переключение в реальный режим возможно только через аппаратный сброс процессора.

По составу и назначению в реальном режиме регистры 80286 в основном совпадают с регистрами 8086/88. Изменения касаются назначения бит регистра 8086, процессор 80286 имеет 16-битную шину данных и очередь команд 6 байт. За счет архитектуры сокращенно время выполнения операций: процессор 20286 с тактовой частотой 12,5 МГц работает более чем в 6 раз быстрее чем 8086 с тактовой частотой 5 МГц. Предусмотрена возможность использования высокопроизводительного процессора 80287, программно совместимого с 8087.

Под управлением MSDOS процессор 80286 обычно используют в реальном режиме работы. Защищенный режим используют ОС типа XENIX, UNIX, OS/2, NetWare286 и оболочка MS Windows. Хотя его преимущества в РС реализованы лишь частично (он в основном использовался как быстрый процессор 8086), именно с этим процессором связан настоящий “бум” на рынке РС.

1.3.1. Организация памяти 80286

Как и у процессоров 8086/8088, для обращения к памяти процессор (совместно с внешней схемой) формирует шинные сигналы MEMWR# (Memory Write) и MEMRD# (Memory Read) для операции записи и считывания соответственно. Шина адреса разрядностью 24 бита позволяет адресовать 16 Мб физической памяти, но в реальном режиме доступен только 1 Мб, начинающийся с младших адресов. С программной точки зрения память также организуется в виде сегментов, но управление сегментацией имеет существенные различия для реального и защищенного режимов.

В реальном режиме по адресации памяти декларируется полная совместимость с процессором 8086, который своей 16-битной адресной шиной охватывает пространство в 1 Мб. На самом деле на радость разработчиков программного обеспечения РС, 80286 имеет ошибку, “узаконенною” и в следующих поколения процессоров. При вычислении физического адреса возможно возникновение переполнения, которое с 20-битной шиной адреса просто игнорируется. Например, Seg=FFFFh и EA=FFFF, физический адрес, вычисленный по формуле PA=16*Seg+EA=10FFEF, процессором 8086 трактуется как 0FFEF – адрес, принадлежащий первому мегабайту. Однако на выходе А20 процессора 80286 в этом случае устанавливается единичное значение, что соответствует адресу ячейки из второго мегабайта физической памяти. Для обеспечения полной программной совместимости с 8086 в схему РС был введен специальный вентиль Gate A20, принудительно обнуляющий бит А20 системной шины адреса. Не оценив потенциальной выгоды от этой ошибки, управление вентилем узаконили через программно-управляемы бит контроллера клавиатуры 8042. Когда оперативная память подешевела, а “аппетит” программного обеспечения вырос, в эту небольшую область (64К-16 бит) стали помещать некоторые резидентные программы или даже часть операционный системы, а для ускорения управлением вентилем появились более быстрые способы (Gate A20 Fast Control).

В отличии от 8086 процессор 80286 имеет средства контроля за переходом через границу сегмента, работающие в реальном режиме. При попытке адресации к слову, имеющему смещение FFFh (его старший байт выходит за границу сегмента), или выполнения инструкции, все байты которой не умещаются в одном сегменте, процессор вырабатывает прерывание – исключение 13 (0Dh) – Segment Overrun Exception. При попытке выполнения инструкции ES-CAPE с операндом памяти, не умещаемся в сегменте, вырабатывается исключение 9 – Processor Extension Segment Interrupt.

В защищенном режиме работают не все режимы адресации, допустимые для 8086 и реального режима 80286. Отличия касаются определения сегментов:

сегментные регистры CS, DS, SS и ES хранят не сами базовые адреса сегментов, а селекторы, по которым из таблицы, хранящейся в ОЗУ, извлекаются дескрипторы сегментов;

дескриптор описывает базовый адрес, размер сегмента (1-64 Кб) и его атрибуты;

базовый адрес сегмента имеет разрядность 24 бита, что и обеспечивает адресацию 16 Мб физической памяти.

Селекторы, загружаемые в 16-битные сегментные регистры, имеют три поля:

RPL (биты 0, 1), TI (бит 2) и INDEX (биты 3-15):

RPL (Requested Privilege Level) – запрошенный уровень привилегий;

TI (Table Indicator) – индикатор использования GDT – глобальный (TI=0) или LDT – локальной (TI=1) таблицы дескрипторов;

INDEX – номер дескриптора в таблице.

Дескрипторы хранятся в слове и занимают по четыре смежных слова (8 байт). При загрузке нового значения селектора дескрипторы считываются из ОЗУ и кэшируются во внутренних программно не доступных (и невидимых) регистрах процессора. До смены значения селектора при обращения к памяти используются значения дескрипторов только из кэш-регистров. Обращение к дескрипторам выполняются как заблокированные шинные циклы, что обеспечивает целостность дескрипторов и при наличии других контроллеров шины.

Для функций передачи управления и переключения задач определенны специальные типы дескрипторов

Похожие работы

... . В качестве такого разъема AMD решила использовать 462-контактный Socket A, который по своим размерам, да и по внешнему виду похож как на Socket 7, так и на Socket 370. Поэтому, с Socket A процессорами AMD можно использовать старые Socket 7 и Socket 370 кулеры. Единственное, не следует при этом забывать, что тепловыделение Duron несколько превосходит количество тепла, отдаваемое Celeron, поэтому ...

... меньше размер транзистора, тем меньше тепла он излучает при работе. Первые процессоры Итак, разобравшись с некоторыми основными свойствами процессоров, перейдем непосредственно к истории. В далеком 1971 году корпорация Intel явила миру первый микропроцессор, прадедушку того гигагерцового монстра, что стоит у тебя в компьютере. Первый микропроцессор имел индекс 4004. Это был четырехразрядный ...

... оснащать их дополнительными устройствами сотен различных производителей. Итак, после начала широкого внедрения персональных компьютеров в повседневную жизнь, продолжилось быстрое развитие вычислительной техники. Остановимся на наиболее важном элементе: микропроцессор – это эффективный с технологической и экономической точки зрения инструмент для переработки возрастающих потоков информации. Новое ...

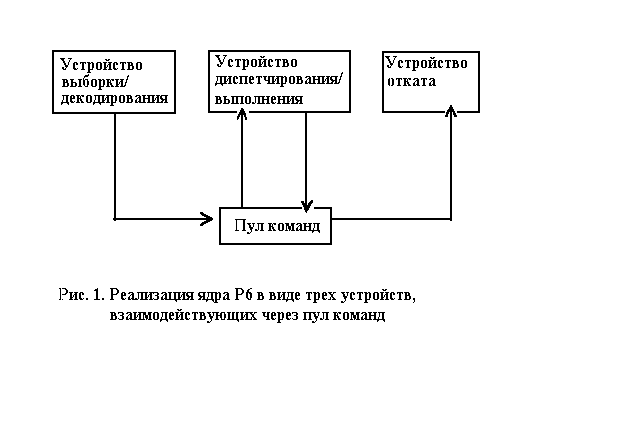

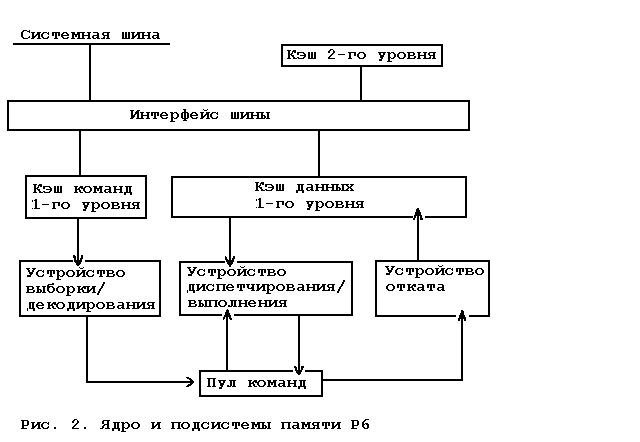

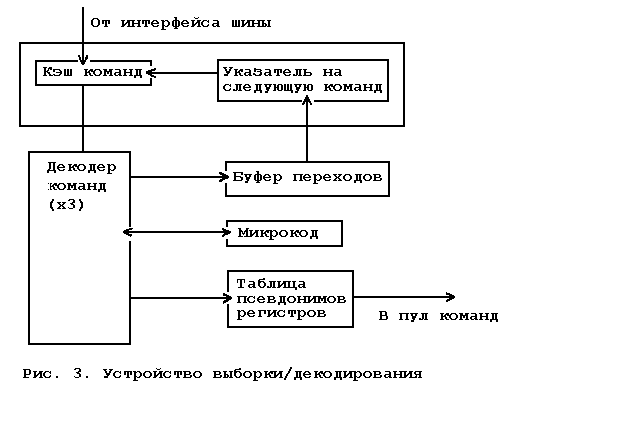

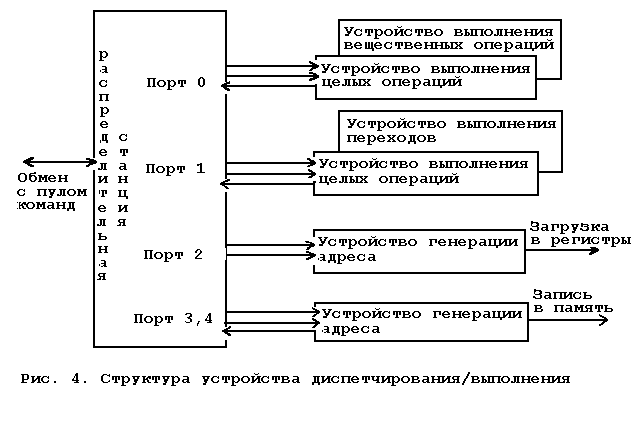

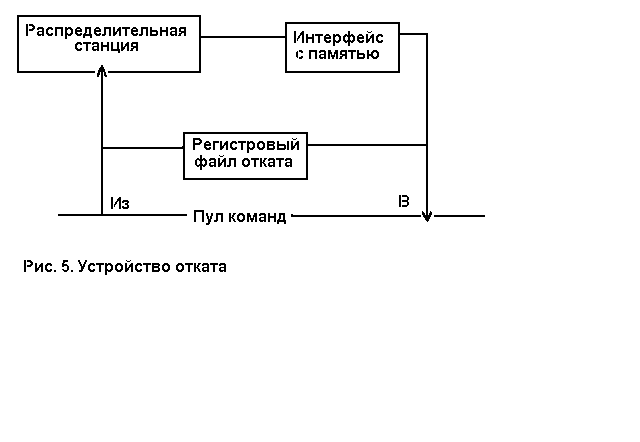

... устройство выбор- ки/декодирования должно правильно предсказать для того, чтобы ра- бота устройства диспетчирования/выполнения не оказалась бесполез- ной. Небольшое количество регистров в архитектуре процессоров «Intel» приводит к интенсивному использованию каждого из них и, как следствие, к возникновению множества мнимых зависимостей меж- ду командами, использующими один и тот же регистр ...

0 комментариев