Навигация

ЯЧЕЙКА ПАМЯТИ

5.5 ЯЧЕЙКА ПАМЯТИ

Ячейка памяти является еще одним базовым элементом, на основе которого строятся запоминающие устройства различных блоков. Ячейка памяти предназначена для хранения информации поступившей по входной

шине и считывания информации по выходной шине, причем ячейка должна памяти должна обеспечивать координатную выборку информации. Ячейка памяти представляет собой простейший триггер, содержащий две пары КМДП транзисторов и два п-канальных транзистора в качестве ключей (см. рис. 5.8). Необходимо отметить, что при разработке элементов ячейки памяти учитывались требования миниатюризации с одной стороны и требования обеспечения определенного запаса по быстродействию с другой.

Рис. 5.8. Принципиальная схема запоминающей ячейки.

Рассмотрим принцип работы данной ячейки. При поступлении напряжения логической единицы на адресный вход (Адрес), транзисторы VT5 и VT6 открываются и триггер, собранный на VT1 - VT4, начинает работать в обычном режиме, т.е. при поступлении на вход логической единицы, на выходе образуется логический ноль, и, наоборот, при поступлении логического нуля, на выходе образуется логическая единица. Это происходит из-за того, что один из транзисторов VT1 или VT2 открыт, т.к. они включены в противофазе. Транзисторы VT3 и VT4 играют роль динамической нагрузки . Если использовать один из входов триггера для записи

информации (Запись), а с другого эту информацию считывать (Считывание), то получится ячейка памяти, но с инверсным выходом, т.к. считанные сигналы необходимо усилить, то это можно сделать при помощи инвертирующих усилителей считывания.

Для объединения ячеек памяти в единое запоминающее устройство необходимо объединить в общие шины входные и выходные выводы, так чтобы была возможность записывать и считывать информацию в соответствии с функциональными требованиями, а выводы выбора адреса объединить в одну параллельную шину. Схема фрагмента запоминающего устройства из четырех ячеек приведена на рисунке 5.9.

Рис. 5.9. Схема объединения запоминающих ячеек.

Результаты разработки топологии запоминающих ячеек проектируемой БИС рассмотрены в главе « Конструктивные особенности проектируемого устройства », там же рассмотрен принцип размещения ячеек на одном кристалле .

РАЗРАБОТКА СТРУКТУРНОЙ СХЕМЫ ПРОЕКТИРУЕМОГО УСТРОЙСТВА

БИС группового канального интерфейса ( ГКИ ) необходима для сопряжения исходящих и входящих абонентских каналов с линией передачи ИКМ-30/32 со стороны абонентского оборудования , а также сопряжения линии ИКМ-30/32 с коммутационным полем со стороны ЭАТС и обеспечивает кроме того ввод/вывод служебных каналов линии ИКМ для передачи служебной информации коммутационной системы (КС ), что позволяет сократить номенклатуру требуемых БИС. БИС ГКИ может подключаться на обоих концах линии ИКМ-30/32 .

3. РАЗРАБОТКА СТРУКТУРНОЙ СХЕМЫ УСТРОЙСТВА

СРАВНЕНИЕ ПРОЕКТИРУЕМОЙ СИСТЕМЫ С ЦИФРОВОЙ ТРАНСПОРТНОЙ СЕТЬЮ КОМПАНИИ “МТУ-ИНФОРМ”.

Прежде всего необходимо отметить, что обе системы имеют в своей основе кольцевой принцип построения сети, что обеспечивает преимущества по сравнению с радиальной схемой построения сети . Основным отличием проектируемой системы от сети , построенной по принципу Синхронной Цифровой Иерархии, является снижение минимальной пропускной способности канала до 2,048 Мбит/с, это накладывает определенные условия на построение устройств обеспечивающих работу сети. Вторым важным отличием проектируемой системы является децентрализация управления, которая позволяет использовать устройства системы независимо от центрального узла управления, что в конечном итоге позволяет продолжить работу сети при выходе из строя центрального управляющего элемента , и тем самым повысить надежность системы вцелом .

АНАЛИЗ РАЗЛИЧНЫХ ВАРИАНТОВ ПОСТРОЕНИЯ СТРУКТУРНОЙ СХЕМЫ ГКИ .

Исходя из назначения устройства, можно представить устройство в виде некоего блока, который обеспечивает сопряжение 64х входящих цифровых каналов с линией передачи ИКМ –30/32 32 со стороны абонентского оборудования , а также сопряжения линии ИКМ-30/32 с коммутационным полем со стороны ЭАТС и обеспечивает кроме того ввод/вывод служебных каналов линии ИКМ для передачи служебной информации коммутационной системы (КС ) . Структурная схема такого устройства показана на рисунке 3.1.

Комму-татор

Групповой

канальный

интерфейс

Групповой

канальный

интерфейс

УСТРОЙСТВО УПРАВЛЕНИЯ

Шина обмена Входящий канал 16,384 Мбит/с .

Исходящий канал 16,384 Мбит/с .

Групповые каналы 2,048 Мбит/с .

Рис. 3.1. Общее строение устройства .

Для выделения из входящего тракта 16,384 Мбит/с групповых кана-лов ИКМ-30/32 и служебного канала в КАНАЛЬНОМ ИНТЕРФЕЙСЕ необходим специальный блок , отвечающий за их выделение (назовем этот блок БЛОКОМ ТАКТОВОЙ СИНХРОНИЗАЦИИ ), а для синхронизации по циклам необходимо выделить синхроимпульсы цикловой и сверхцикловой синхронизации. Тогда структурная схема примет вид, показанный на рис. 3.2. Этот вариант укрупненной структурной схемы включает в себя дополнительно БЛОК ЦИКЛОВОЙ СИНХРОНИЗАЦИИ .

БЛОК

ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

БЛОК

ТАКТОВОЙ СИНХРОНИЗАЦИИ

УСТРОЙСТВО УПРАВЛЕНИЯ

2,048 Мбит/с

Шины обмена

Рис . 3.2.

Далее необходимо выравнивание по циклам ( синхронизация по нача-лу цикла входящего тракта с началом КС ) . Это можно сделать в БУФЕ-РЕ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ . Одновременно в БЦС выполняется преобразование формата входящих групповых каналов ИКМ-30/32 в формат тракта коммутационного поля ( рисунок 3.3.).

БУФЕР

ЦИКЛОВОЙ СИНХРОНИ-ЗАЦИИ

БЛОК

ТАКТОВОЙ СИНХРОНИ-ЗАЦИИ

БЛОКЦИКЛОВОЙ СИНХРОНИЗА-ЦИИ

УСТРОЙСТВО УПРАВЛЕНИЯ

2,048 Мбит/с

Шины обмена

Рис . 3.3.

Для связи внутренней шины ГКИ с информационными и служебными каналами тракта ИКМ служит МУЛЬТИПЛЕКСОР / ДЕМУЛЬТИПЛЕ-КСОР . И для передачи цикловых синхроимпульсов в формате стандарт-ного канала ИКМ-30/32 нужен ФОРМИРОВАТЕЛЬ ИКМ ( рис 3.4.) .

2,048 Мбит/с

16,384 Мбит/с

Шины обмена

УСТРОЙСТВО УПРАВЛЕНИЯШина обмена с внешним контроллером управления

Рис . 3.4.

При детальном рассмотрении структуры можно заметить, что для обеспечения циклового выравнивания входящих групповых каналов необходимо запомнить информацию из этих каналов , приходящую в разное время , а затем начать считывание информации по сигналу синхронизации из УСТРОЙСТВА УПРАВЛЕНИЯ . Для выполнения временной коммутации также необходимо запомнить приходящую информацию , а затем считывать эту информацию в порядке соответ-ствующим карте коммутации . Отсюда несложно сделать вывод о целесообразности объединения БЛОКА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ и БУФЕРА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ . Такая структурная схема представлена на рис. 3.5.

УСТРОЙСТВО УПРАВЛЕНИЯ

2,048 Мбит/с

16,384 Мбит/с

Шины обмена

Шина обмена с внешним контроллером управления

Рис . 3.5.

Рассмотрим подробнее назначение блоков:

Блок тактовой синхронизации .

Синхронизация по тактам ( фазе ) входящей линии тракта передачи с фазой коммутационного поля КС .

Блок цикловой синхронизации .

Блок цикловой синхронизации должен выполнять следующие фун-кции :

поиск синхросигнала ;

вхождение в синхронизм ;

поддерживание синхронизма ;

обнаружение входа из синхронизма при сбоях .

Блок мультиплексора / демультиплексора .

Мультиплексор / демультиплексор осуществляет связь внутренней шины с информационными и служебными каналами тракта ИКМ . Мульти-плексная внутренняя шина служит для обмена информацией между каналами ИКМ тракта и шиной управляющей микро-ЭВМ , через соответствующие интерфейсы :

интерфейс служебных сигналов выполняет функции выделения , буферизации и ввода/вывода сигналов информационных каналов ( например , посылка вызова , отбой и др .) ;

интерфейс 16–го канала осуществляет ввод/вывод служебной информации 16–го канала , необходимой для межпроцессорного обмена ;

интерфейс абонентских каналов обеспечивает доступ к любому абонентскому каналу и может использоваться для сопряжения уплотненного канала передачи данных с групповым трактом ИКМ , а также для диагностики абонентских каналов .

Блок формирователя ИКМ .

Передатчик цикловых синхроимпульсов предназначен для формирования в групповом исходящем канале циклового и сверхциклового синхросигналов в формате внутрисистемного обмена , либо в формате стандартного канала ИКМ–30/32 .

ВЫБОР СХЕМО-ТЕХНОЛОГИИ ПРОЕКТИРУЕМОЙ БИС

КРАТКИЙ ОБЗОР СУЩЕСТВУЮЩИХ СХЕМО-ТЕХНОЛОГИЙ ПРИМЕНЯЕМЫХ В

ИНТЕГРАЛЬНЫХ СХЕМАХ

Рассмотрим наиболее распространенные схемотехнологии применяемые в интегральных схемах:

Транзисторно-транзисторная логика (ТТЛ).

Эмиттерно-связанная логика (ЭСЛ).

Логика, построенная на основе структуры метал-диэлетрик-полупроводник с п-каналом (пМДП).

Логика, построенная на основе структуры метал-диэлетрик-полупроводник с транзисторами разной проводимости (КМДП).

ТЕХНОЛОГИЯ ТТЛ.

Технология ТТЛ основана на биполярных структурах. Базовый элемент ТТЛ представляет собой схему, содержащую один многоэмиттерный транзистор и один обычный (см. рис. 4.1), это логическая схема И-НЕ (функцию И выполняет транзистор VT1, а функцию инверсии выполняет транзистор VT2).

Рис. 4.1. Базовый элемент ТТЛ.

Подобная схема обладает низкой помехоустойчивостью и низким быстродействием, быстродействие можно увеличить, используя сложный инвертор, который позволяет сократить время включения (переход из логического «0» в логическую «1»); но время выключения (переход из логической «1» в логический «0») сократить, не удается.

Более высокое быстродействие позволяют получить схемы субсемейства ТТЛШ (транзисторно-транзисторная логика с использованием транзисторов с барьером Шотки; см. рисунок 4.2). В таких схемах барьер Шотки создает нелинейную обратную связь в транзисторе, в результате транзисторы не входят в режим насыщения, хотя и близки к этому режиму. Следовательно, практически исключается время рассасывания, что позволяет существенно увеличить быстродействие.

Р

ис. 4.2. Транзистор Шотки.

ТЕХНОЛОГИЯ ЭСЛ.

Т

ехнология ЭСЛ является так же, как и технология ТТЛ, биполярной, т.е. элементы строятся с использованием биполярных структур. Основой элементов ЭСЛ является так называемый «переключатель тока», на основе которого строится базовый элемент этой технологии - ИЛИ- -НЕ (см. рис. 4.3); по выходу1 данной схемы реализуется логическая функция ИЛИ-НЕ, а по выходу2 - ИЛИ.

Рис. 4.3. Базовый элемент ЭСЛ.

Из-за низкого входного сопротивления схемы ЭСЛ обладают высоким быстродействием и работают преимущественно в активном режиме, следовательно, помеха попавшая на вход усиливается. Для повышения помехоустойчивости шину коллекторного питания делают очень толстой и соединяют с общей шиной.

По сравнению со схемами ТТЛ схемы ЭСЛ обладают более высоким быстродействием, но помехоустойчивость у них гораздо ниже. Схемы ЭСЛ занимают большую площадь на кристалле, потребляют большую мощность в статическом состоянии, так как выходные транзисторы открыты и через них протекает большой ток. Схемы, построенные по данной технологии не совместимы со схемами, построенными по другим технологиям, использующим источники положительного напряжения.

ТЕХНОЛОГИЯ пМДП.

В отличие от технологий, рассмотренных выше, технология пМДП основана на МДП - структурах, которые обеспечивают следующие преимущества по сравнению с биполярными:

Входная цепь (цепь затвора) в статическом режиме практически не потребляет тока (высокое входное сопротивление);

Простая технология производства и меньшая занимаемая площадь на кристалле.

Основными логическими схемами изготовлеваемыми на основе пМДП являются схема ИЛИ-НЕ и И-НЕ (см. рис. 4.4 и рис. 4.5).

Р

ис. 4.4. Схема ИЛИ-НЕ.

Рис. 4.5. Схема И-НЕ.

К недостаткам этих схем можно отнести невысокое быстродействие, по сравнению со схемами ТТЛШ и ЭСЛ. Но в настоящее время благодаря применению новых технологий (окисная изоляция, использование поликремневых затворов, технология «кремний на сапфире») создаются быстродействующие МДП структуры.

Похожие работы

... местному или удаленному DTE о необходимости восстановления потока информации. Знак XOFF представляет собой символ CTRL-S ("S), a XON — символ CTRL-Q (*0). Если управление потоком разрешено по канальному интерфейсу модема и по последовательному порту, и знак XOFF принят по каналу связи, то этот знак заставляет модем приостановить передачу данных из своего буфера в канал связи. Буфер модема ...

... этому представлен данный дипломный проект, который является первым в своем роде в г. Астрахани. В данном дипломном проекте рассматривается проблема построения локальной корпоративной сети звукового обеспечения интеллектуального здания на основе технологии Fast Ethernet для Областного центра детского и юношеского творчества г. Астрахани. Целью дипломного проекта является организация локальной ...

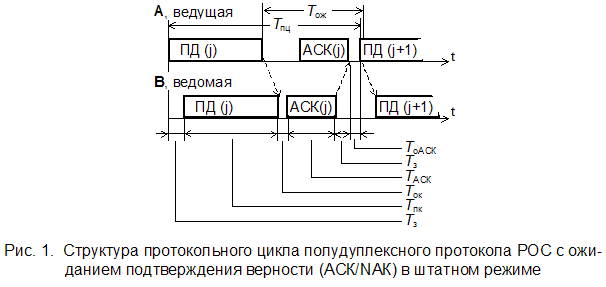

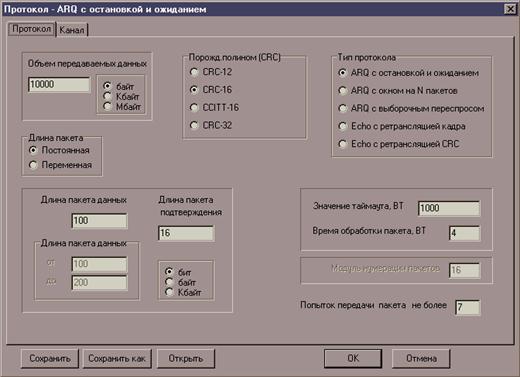

... Задача 1. Сопоставление эффективности различных протоколов с обратной связью в тех или иных условиях (ограничения на длину кадров, запаздывание в каналах и проч.) Задача 2. Исследование эффективности протоколов с обратными связями в зависимости от интенсивности ошибок в каналах. Исследовать, как влияет наличие ошибок по отдельности в прямом и обратном каналах на общую эффективность протоколов ...

... сигналами времени. Ядро предлагает интерфейс для программирования приложения с целью получения функций в виде отдельных программ. 1.2 Разработка автоматизированной системы управления электроснабжением КС «Ухтинская» 1.2.1 Цель создания АСУ-ЭС Целью разработки является создание интегрированной АСУ ТП, объединяющей в единое целое АСУ электрической и теплотехнической частей электростанции, ...

0 комментариев