Навигация

3.2 Синтез регистров

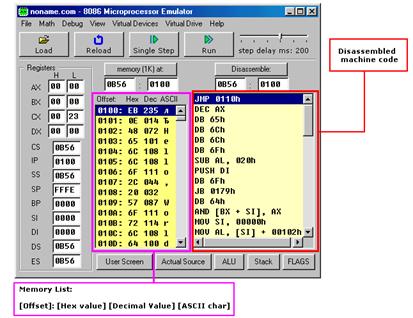

Для хранения и сдвига множителя Y и суммы S необходим шестнадцатиразрядный регистр сдвига. Для хранения множимого понадобится один восьмиразрядный регистр RgX.

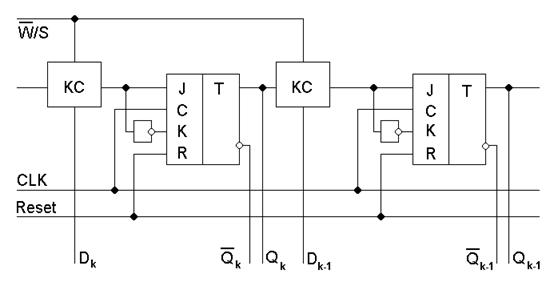

Структурная схема регистра сдвига показана на рис.3.4, из которого видно, что необходимо синтезировать одну комбинационную схему. Таблица истинности для этой схемы представлена в табл. 3.3, где значение управляющего сигнала W/S равное нулю соответствует режиму записи, а равное единице - режиму сдвига на один бит вправо за такт.

Рисунок 3.4 Структурная схема регистра сдвига.

Таблица 3.3

| D | Q | S | J |

| X | 0 | 0 | 0 |

| X | 1 | 0 | 1 |

| 0 | X | 1 | 0 |

| 1 | X | 1 | 1 |

По приведенной таблице истинности находим логические выражения, описывающие работу синтезируемой схемы, и приводим их к заданному базису.

![]() (3.9)

(3.9)

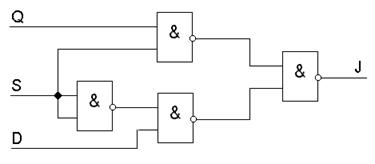

Рисунок 3.5 Схема управления сдвигом.

Принципиальная схема, построенная по выражению (3.9), приведена на рис.3.5.

Восьмиразрядный регистр для хранения Х будет представлять собой восемь JK – триггеров с объединенными тактовыми входами.

Мощность, потребляемую регистрами, определим по формуле

![]() ,

(3.10)

,

(3.10)

где ![]() ,

, ![]() – количество триггеров в регистрах RgX и RgY соответственно;

– количество триггеров в регистрах RgX и RgY соответственно;

![]() – мощность, потребляемая триггером (12 мВт).

– мощность, потребляемая триггером (12 мВт).

![]() - мощность, потребляемая схемой управления сдвигом (8 мВт).

- мощность, потребляемая схемой управления сдвигом (8 мВт).

Подставив численные значения в формулу (3.10), получим:

![]() .

.

Время предустановки регистра равно времени предустановки триггера ![]() , а время задержки – времени задержки триггера

, а время задержки – времени задержки триггера ![]() .

.

Похожие работы

... nразъем = 135 резист = 0,05*10-6 час-1 nрезист = 3 общ = 344,1*10-6 час-1 Т = 2906,14 час Р = 0,6 ЗАКЛЮЧЕНИЕВ данном курсовом проекте был разработан процессор для ограниченного набора команд. Исходя из критерия проектирования, то есть максимального быстродействия блоки процессора построены на основе ТТЛШ технологии, на перспективных быстродействующих сериях, эти серии имеют ...

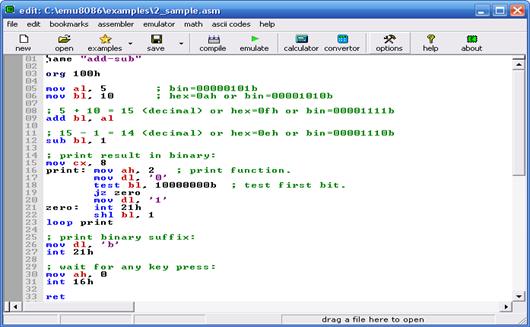

... AVR Studio запомнит расположение окон и использует эти установки при следующем запуске проекта. 3.2. Анализ методики реализации разработки программного обеспечения 3.2.1. Классификация вариантов заданий Цель заданий – практическое освоение методики программирования на ассемблере микроконтроллеров ATMEL семейства AVR, отладка программы на симуляторе AVR Studio и программирование кристалла с помощью ...

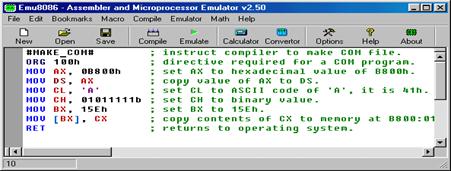

... . В случае выбора пункта «выход», необходимо реализовать завершение работы программы и передачу управления операционной системе DOS. 1.3. Требования техническим и программным средствам Программа выполнена на языке ассемблера 8086 процессора, соответственно ей необходим IBM PC – совместимый компьютер с процессором не ниже 8086, также программа может выполняться на компьютерах с ...

аучного цикла является отсутствие возможности реальной постановки учебного, и лабораторного эксперимента. Хотя в настоящее время имеются разработки виртуальных лабораторных практикумов, однако окончательно решение проблемы требует пристального внимания специалистов различных профилей, в том числе и психолого-педагогического. 1.2 Роль технологии виртуальных приборов обучения в техническом вузе ...

0 комментариев