Навигация

Разработка структурной схемы

2. Разработка структурной схемы

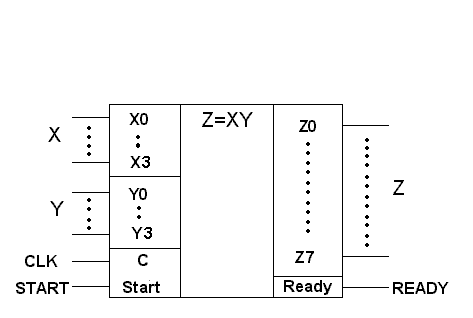

Разрабатываемое АЛУ будет иметь восьмиразрядный вход данных X, восьмиразрядный вход данных Y, шестнадцатиразрядный выход результата Z, вход начала вычисления START, выход готовности результата READY, вход принудительного сброса R и тактовый вход C (рис.2.1).

Рисунок 2.1 Условное графическое изображение АЛУ.

При разработке структурной схемы необходимо обратить внимание на уменьшение количества применяемых элементов , что в свою очередь приведет к снижению потребляемой мощности. Одновременно с этим необходимо обеспечить время вычисления менее заданного. Также необходимо уделить внимание предотвращению гонок в схеме.

Исходными данными для разработки структурной схемы является алгоритм вычисления. В соответствии с заданным алгоритмом вычисления для его реализации как минимум потребуются два регистра для хранения и сдвига операндов. Для реализации счётчика потребуется три триггера. Для определения окончания вычисления необходима схема сравнения J с 0.

Для реализации математических вычислений потребуется восьмиразрядный сумматор.

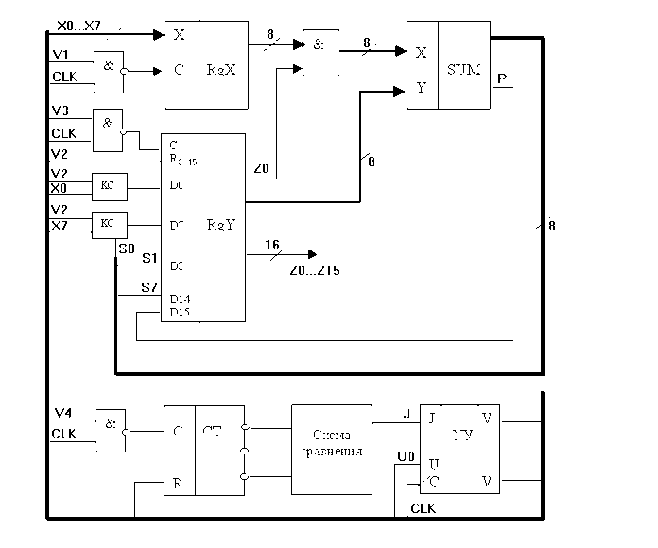

Разработанная структурная схема показана на рис. 2.2. В этой схеме множитель Y и результат Z хранятся в одном сдвиговом 16-ти разрядном регистре RgY. Регистры RgХ и RgY имеют как прямые, так и инверсные выходы , что позволяет уменьшить количество элементов в сумматоре.

Рисунок 2.2 Структурная схема АЛУ для умножения двоичных чисел.

Рисунок 2.2 Структурная схема АЛУ для умножения двоичных чисел.

Как видно из схемы активный уровень сигналов управления - высокий, и устройство управления тактируется по фронту импульса, а исполнительные устройства - по спаду, что позволяет избежать гонок в схеме.

3 Синтез Компонентов

3.1 Синтез сумматора

Так как построить сумматор сразу для восьми разрядов достаточно сложно, сумматор будем выполнять по схеме последовательного соединения полных одноразрядных сумматоров.

Таблица истинности полного двоичного сумматора приведена в табл.3.1, где а и b - слагаемые, S - сумма, P - перенос из предыдущего разряда. Рn – перенос в следующий разряд.

Таблица 3.1

| а | B | P | S | Рn |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

По таблице истинности строим карты Карно (рис.3.1) и проводим минимизацию логических выражений, описывающих работу полного сумматора.

S Pn

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 | 1 | 0 | 1 |

|

| 0 | 0 | 1 | 0 |

| P | 1 | 0 | 1 | 0 |

| P | 0 | 1 | 1 | 1 |

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 3.1 Карты Карно для полного сумматора.

![]() (3.1)

(3.1)

![]() (3.2)

(3.2)

Полученные выражения (3.1) и (3.2) приводим к заданной элементной базе:

![]() (3.3)

(3.3)

![]() (3.4)

(3.4)

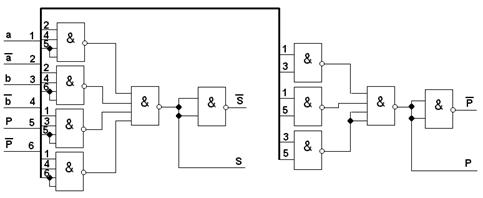

По полученным выражениям строим схему полного сумматора (рис.3.2).

Рисунок 3.2 Принципиальная схема полного сумматора.

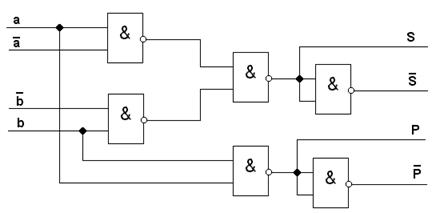

Нулевой разряд сумматора для экономии элементов построим по схеме полусумматора. Таблица истинности полусумматора представлена в табл.3.2.

Таблица 3.2

| А | B | S | Ро |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

По таблице истинности получаем логические выражения:

![]() (3.5)

(3.5)

![]() (3.6)

(3.6)

По полученным выражениям строим принципиальную схему (рис.3.3).

Рисунок 3.3 Принципиальная схема полусумматора.

Потребляемую схемой мощность найдем по формуле:

![]() . (3.7)

. (3.7)

где N – количество логических элементов в схеме;

![]() – мощность, потребляемая одним элементом.

– мощность, потребляемая одним элементом.

Количество элементов в схеме равно 83 а мощность элемента – ![]() . Подставляя данные в формулу (3.7) получим:

. Подставляя данные в формулу (3.7) получим:

![]() .

.

Время вычисления будет максимально в случае формирования переноса последовательно в семи младших разрядах сумматора. Таким образом, время счета будет определяться как сумма времени формирования переноса в семи младших разрядах и времени формирования выходного сигнала в старшем разряде:

![]() ,

(3.8)

,

(3.8)

где ![]() – время срабатывания одного логического элемента;

– время срабатывания одного логического элемента;

![]() – максимальный путь (количество последовательно пройденных элементов) формирования переноса в i-ом разряде;

– максимальный путь (количество последовательно пройденных элементов) формирования переноса в i-ом разряде;

![]() – максимальный путь формирования результата в старшем разряде (3 элемента).

– максимальный путь формирования результата в старшем разряде (3 элемента).

Время срабатывания равно 4![]() . Пути

. Пути ![]() для сумматора (разряды 1 – 7) и для полусумматора (разряд 0) равны трём. Тогда по формуле (3.8) получим:

для сумматора (разряды 1 – 7) и для полусумматора (разряд 0) равны трём. Тогда по формуле (3.8) получим:

![]() .

.

Похожие работы

... nразъем = 135 резист = 0,05*10-6 час-1 nрезист = 3 общ = 344,1*10-6 час-1 Т = 2906,14 час Р = 0,6 ЗАКЛЮЧЕНИЕВ данном курсовом проекте был разработан процессор для ограниченного набора команд. Исходя из критерия проектирования, то есть максимального быстродействия блоки процессора построены на основе ТТЛШ технологии, на перспективных быстродействующих сериях, эти серии имеют ...

... AVR Studio запомнит расположение окон и использует эти установки при следующем запуске проекта. 3.2. Анализ методики реализации разработки программного обеспечения 3.2.1. Классификация вариантов заданий Цель заданий – практическое освоение методики программирования на ассемблере микроконтроллеров ATMEL семейства AVR, отладка программы на симуляторе AVR Studio и программирование кристалла с помощью ...

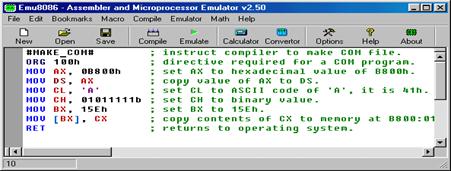

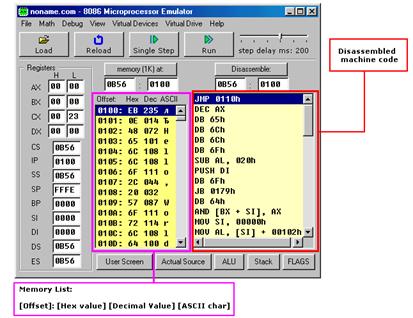

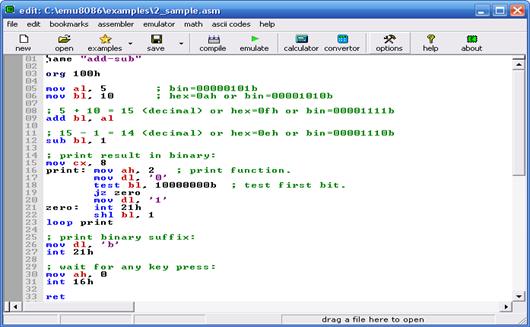

... . В случае выбора пункта «выход», необходимо реализовать завершение работы программы и передачу управления операционной системе DOS. 1.3. Требования техническим и программным средствам Программа выполнена на языке ассемблера 8086 процессора, соответственно ей необходим IBM PC – совместимый компьютер с процессором не ниже 8086, также программа может выполняться на компьютерах с ...

аучного цикла является отсутствие возможности реальной постановки учебного, и лабораторного эксперимента. Хотя в настоящее время имеются разработки виртуальных лабораторных практикумов, однако окончательно решение проблемы требует пристального внимания специалистов различных профилей, в том числе и психолого-педагогического. 1.2 Роль технологии виртуальных приборов обучения в техническом вузе ...

0 комментариев