Навигация

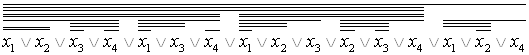

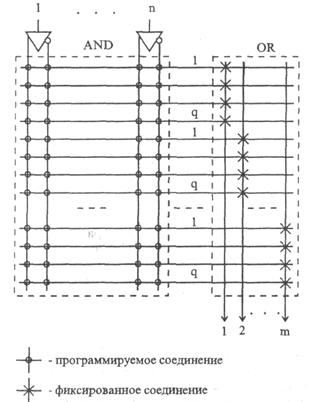

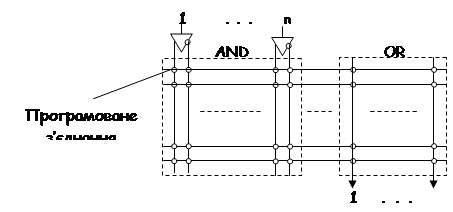

2 або-ні

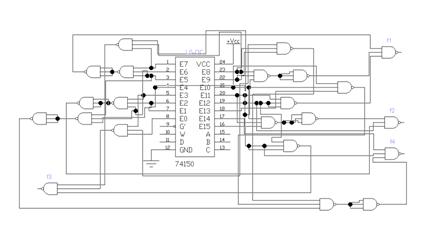

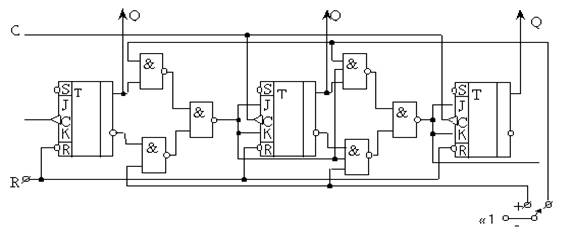

Дивитись у додаток Схема 1.

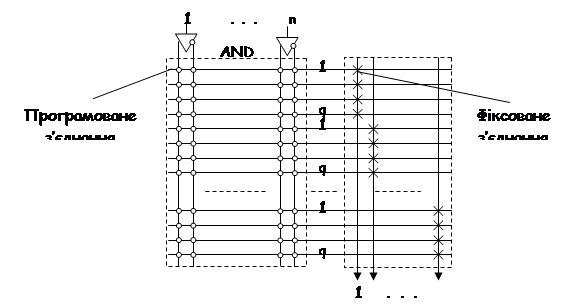

2 і-ні / 3 і

![]()

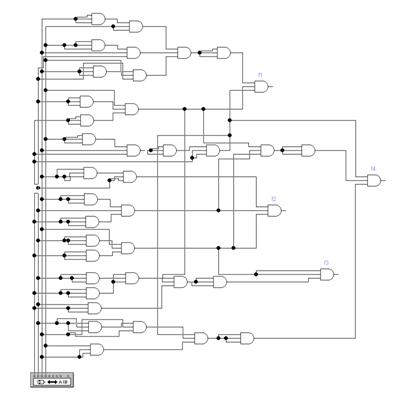

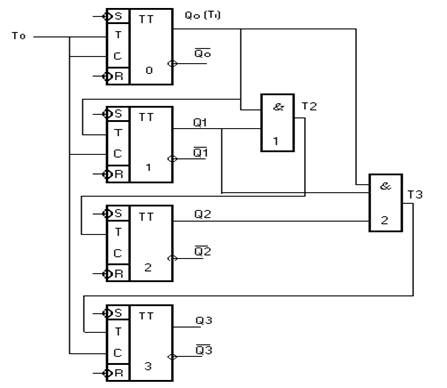

Дивитись у додаток Схема 2.

Вибраємо операторні форми, що забезпечують одержання комбінаційної схеми з максимальною швидкодією і комбінаційною схемою з мінімальним числом умовних корпусів, тобто схему з кращим параметром T і схему з мінімальним значенням N. Усі мікросхеми мають по 14 виходів.

Знаходимо час затримки сигналу:

![]() ,

,

де ![]() – кількість елементів, що входять у максимальну по довжині ланцюжок елементів,

– кількість елементів, що входять у максимальну по довжині ланцюжок елементів, ![]() – усереднене значення часу затримки, що знаходиться по формулі:

– усереднене значення часу затримки, що знаходиться по формулі:

![]() .

.

![]()

![]() ,

,

![]()

![]()

![]()

![]()

![]() ,

,

![]() .

.

Розраховуємо складність схем:

,

,

де ![]() – кількість елементів у мікросхемі,

– кількість елементів у мікросхемі, ![]() – число виводів мікросхеми і-того типу,

– число виводів мікросхеми і-того типу, ![]() – число типів мікросхем.

– число типів мікросхем.

![]()

![]() 4,6.

4,6.

![]()

![]() 4,3.

4,3.

На елементах ЗІ-НІ будуємо перетворювач кодів відповідно до таблиці 1.3. У процесі проектування використовуємо методи спільної мінімізації системи перемикальних функцій.

Таблиця 1.3

|

|

|

|

|

|

|

|

|

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

Мінімізація систем булевих функцій відбувається згідно з наступним алгоритмом, який представляє собою модифікацію алгоритму Квайна.

Будуємо повну множину ![]() елементарних кон’юнкцій отриманої системи, приписуючи в дужках після кожної констітуенти ознаку (у вигляді номеру чи номерів БФ у системі) її належності до тих чи інших БФ системи.

елементарних кон’юнкцій отриманої системи, приписуючи в дужках після кожної констітуенти ознаку (у вигляді номеру чи номерів БФ у системі) її належності до тих чи інших БФ системи.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() .

.

Виконуємо мінімізацію функції ![]() , застосовуючи модифікований алгоритм Квайна. Модифікація полягає в тому, що:

, застосовуючи модифікований алгоритм Квайна. Модифікація полягає в тому, що:

– при виконані операції неповного склеювання двох констітуент, елементарній кон’юнкції, що виникає в результаті склеювання, приписується ознака, яка складається із номерів БФ, спільних для двох констітуент (останнє також справедливо для двох елементарних кон’юнкцій, що склеюються). Якщо ознаки констітуент не містять спільних номерів, то склеювання не відбувається;

– операція поглинання відбувається тільки для елементарних кон’юнкцій з однаковими ознаками.

Отримані в результаті склеювання і поглинання елементарні кон’юнкції називаються простими імплікантами системи БФ.

Для зручності виконання операції неповного склеювання пронумеруємо кожну констітуенту із ДДНФ функції ![]() і виконуємо склеювання.

і виконуємо склеювання.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Подальші склеювання і поглинання неможливі, тобто ми отримали всі прості імпліканти системи БФ і остання форма – це скорочена ДНФ БФ ![]() .

.

Будуємо ІТ з тією лише відмінністю, що для кожної констітуети виділяються стільки стовпчиків, скільки різних номерів БФ містить її ознака; строчки ІТ позначаються простими імплікантами скороченої ДНФ; « * » в ІТ проставляються згідно з наступним правилом:

а) проста імпліканта і констітуента мають спільні ознаки;

б) проста імпліканта накриває констітуенту;

в) « * » проставляються лише у клітини, що знаходяться на перетині строчок (з простими імплікантами) і стовпчиків (з констітуентами 1), які мають спільні ознаки.

Далі знаходимо ядро БФ і так далі.

Дивитись у додаток Таблиця 1.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

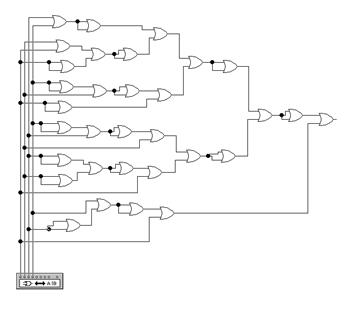

Отримана мінімальна система БФ служить основою для побудови комбінаційної схеми.

Дивитись у додаток Схема 3

Для отриманої схеми визначаємо L, Т и N.

Знаходимо час затримки сигналу:

![]()

![]() ,

, ![]() 100.

100.

Розраховуємо складність схем:

де ![]() – кількість елементів у мікросхемі,

– кількість елементів у мікросхемі, ![]() – число виводів мікросхеми і-того типу,

– число виводів мікросхеми і-того типу, ![]() – число типів мікросхем.

– число типів мікросхем.

![]()

![]() .

.

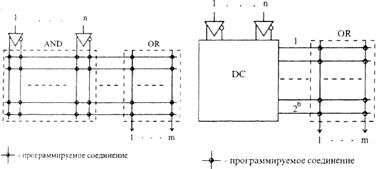

Будуємо схему для реалізації функції, заданої табл. 1.1 з використанням мультиплексорів з двома керуючими входами.

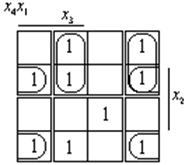

При реалізації функції від чотирьох перемінних з використанням мультиплексора, що має два керуючі входу, треба виключити шістьох різних пар перемінних (x4x3, x4x2, x4x1, x3x2, x3x1, x2x1). При виключенні кожної пари перемінних діаграму Вейча заданої функції можна розглядати як чотири самостійні діаграми для залишкових функцій f0, f1, f2, f3.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Найбільш проста реалізація заданої функції є при виключенні за допомогою мультиплексора перемінних х2х1:

![]()

![]()

![]()

![]()

Дивитись у додаток Схема 4.

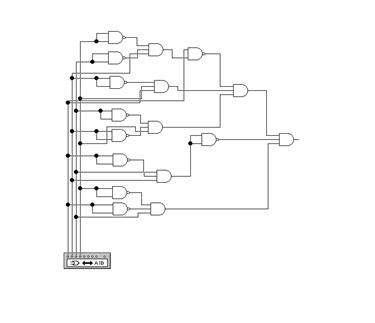

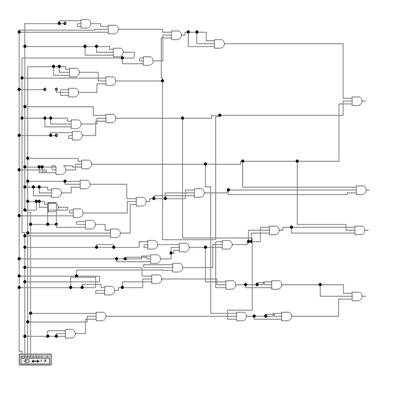

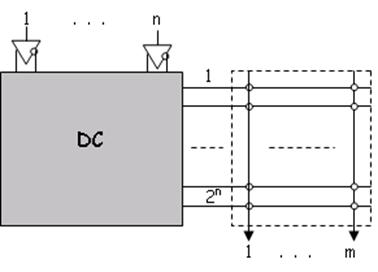

Побудувати перетворювач кодів по табл. 1.3 з використанням елементів ЗІ-НІ і четирьохвхідного дешифратора з інверсними виходами.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Дивитись у додаток Схема 5.

Перелік літератури

1. Акулич И.Л. Математическое программирование в примерах и задачах. – М.: Высшая школа.

2. Вентцель Е.С. Исследование операций. – М.: Наука, 1976.

3. Горелик В.А., Ушаков И.А. Исследование операций. – М: Машиностроение, 1986.– 286с.

4. Давыдов Э.Т. Исследование операций: Учебное пособие для студентов вузов. – М.: Высшая школа, 1990.- 383с.

5. Ермолаев Ю.М. Математические методы исследования операций. – К.: Наука, 1979.

6. Кузнецов Ю.Н. Математическое программирование. – М.: Наука, 1976.

7. Минц М. Математическое программирование. Теория и алгоритмы. – М.: Наука, 1990.

8. Таха Х. Введение в исследование операций. – м.: Мир, 1985.

9. Толбатов Ю.А. Эконометрика в Excel. – К.: Четверта хвиля, 1997.

Додаток

Похожие работы

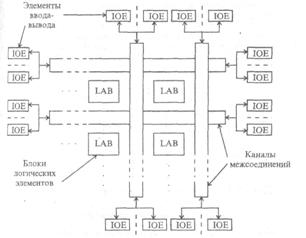

... ім часом компанії-виробники PLD звернули увагу на розробку саме таких програмних пакетів. 2. Призначення та структура системи автоматизованого проектування MAX+PLUS II Система автоматизованого проектування MAX+PLUS II являє собою інтегроване середовище для розробки цифрових пристроїв на базі програмувальних логічних інтегральних схем фірми Altera. Він забезпечує виконання всіх етапів, необхі ...

... цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС. Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності бі ...

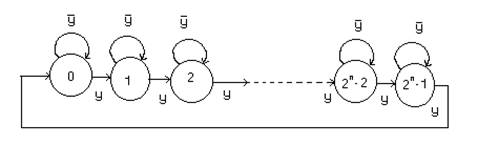

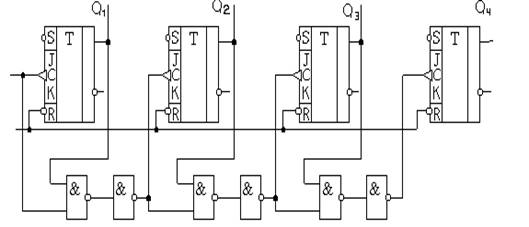

... тригері об’єднані і на них подається рівень логічної „1”; вхід С кожного тригера є лічильним входом. Рисунок 2.1 – Схема електрична принципова дільника частоти з коефіцієнтом ділення К=210 на JK-тригерах 2.3 Розрахунок споживаної потужності Відповідно до схеми електричної принципової до складу лічильника входять п’ять ІМС К555ТВ9 . Споживаний струм складає: К555ТВ9- 0.03 А; Напруга ...

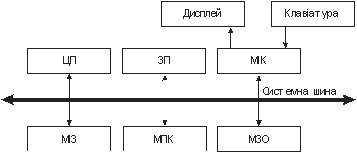

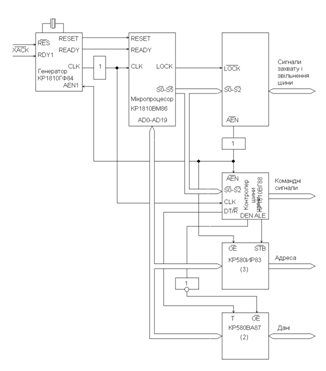

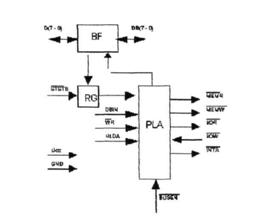

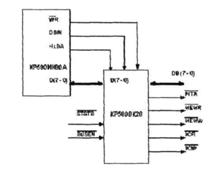

... асемблера, яка дає можливість найбільш повно і раціонально використовувати апаратні і програмні ресурси мікро-ЕОМ. У даному курсовому проекті розроблено схему електричну принципову процесорного модуля з використанням мікропроцесора КР580ВМ80А 1. Загальний розділ 1.1. Призначення проектуємого пристрою У курсовому проекті прийняті наступні скорочення: БА - буфер адреси; БД - буфер ...

0 комментариев