Навигация

Описание функциональной схемы

5. Описание функциональной схемы

В приложении 1 находится функциональная схема ССПИ, рассмотрим особенности ее работы.

Устройство распределения информации УР собранно на буферных регистрах DD1-DD196 сгруппированных по 14 штук на источник. Управлением УР осуществляется регистрами сдвига DD197-DD211, дешифратором DD229 и микроконтроллером DD231. Микроконтроллер берет на себя также функции синхронизации работы всего устройства и преобразования собранной информации в последовательный код с последующей выдачей ее в КС. Элементы НЕ DD212-DD228 нужны для адаптации управляющего сигнала сдвиговых регистров.

Источники опрашиваются по появлении на них запроса. Общий запрос формируется схемой собранной на элементах DD364-DD366.

Особенностью схемы УР является формирование адреса источника на его выходе с помощью сигналов запроса. Таким образом адрес источника считывается как дополнительный 4 разряда данных.

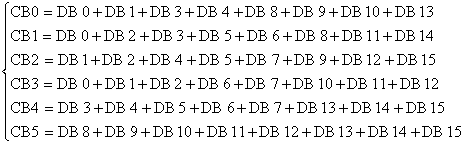

Микросхема DD230 представляет собой шестнадцатиразрядную схему контроля по коду Хемминга. Вход DB предназначен для приёма информационных сообщений, а выход СВ для выдачи контрольных разрядов. В данном случае схема используется для кодирования, управляется выводом Р1.5 микро-ЭВМ DD231.

Таким образом информация с выхода одного из шинных драйверов попадает на вход микро-ЭВМ и схемы контроля по коду Хемминга. Затем микро-ЭВМ подаёт управляющие импульсы на схему контроля и считывает через порт Р3 контрольные символы, которые затем передаются в КС вместе с сообщениями через последовательный интерфейс Р3.1. Система проверок для кода Хемминга обеспечиваемая микросхемой DD230:

(3)

(3)

На приёмной стороне используются аналогичные элементы, но схема контроля по коду Хемминга включена в режиме декодирования. Дешифратор DD232 используется аналогично для выбора получателя сообщения. Вывод Р3.0 является входом данных из КС, Р3.1- Р3.6 выдают контрольные разряды на декодер DD233(этими же выводами производится чтение синдрома), а вывод Р3.7 запрещает выдачу данных в приемные регистры DD267- DD363. Принятый из КС адрес вместе с данными декодируется и в случае отсутствия многократной ошибки, выдается микроконтроллером на дешифратор DD232 , который собственно и выбирает нужный приемник. Отдельные линии приемника также как и на приемной стороне выбираются регистрами сдвига DD235-DD249.

6. Описание принципиальной схемы

Принципиальная схема разрабатываемого устройства находится в приложении 2. Рассмотрим особенности этой схемы. Для реализации связи с приемниками и источниками использованы буферные регистры КР1533ИР33 в таблице 1 находится описание данного типа драйверов.

Таблица1

| ОЕ1 | ОЕ2 | OD |

| 1 | 0 | Z |

| 0 | 0 | DI |

Символ ’’Z‘‘ означает, что выходы регистров переводятся в третье состояние. Дешифраторы реализованы посредством К1533ИД3 с прямыми выходами, что необходимо для управления регистрами сдвига (сдвиг осуществляется по переднему фронту сигнала). При этом входы разрешения работы дешифраторов постоянно подключён к земле, что является разрешением работы.

Схема контроля по коду Хемминга имеет следующие выводы:

Е – управляющий;

DB – вход / выход информационного слова;

СВ – вход / выход контрольного слова;

EF – выход ошибки;

МEF – выход многократной ошибки.

Задание режима микросхемы производится подачей управляющего кода на вход Е согласно таблице2 режимов схемы.

Таблица2

| Е0 | Е1 | Режим работы |

| 0 | 0 | Формирование контрольных разрядов |

| 1 | 0 | Приём информационных и контрольных слов |

| 1 | 1 | Блокировка информации |

| 0 | 1 | Выдача исправленного информационного слова и синдрома ошибки |

Достоверное обнаружение ошибок возможно, если их число не превышает двух. Исправление же совершается только в случае одиночной ошибки в информационном слове. В таблице3 приведены признаки возможных ошибок.

Таблица3

| Число ошибок | EF | MFE | |

| Информационное слово | Контрольное слово | ||

| 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 |

| 2 | 0 | 1 | 1 |

| 0 | 2 | 1 | 1 |

Для поиска и исправления ошибок микросхему предварительно переводят в режим блокирования информации (Е0= Е1=1), после чего на входе Е0 устанавливается уровень логического нуля; ИС переходит в режим выдачи исправленного информационного слова на выход DB и синдрома на выход СВ. Параллельно на выходах EF и MEF появляются признаки наличия ошибок (см. таблицу 3).

ОПИСАНИЕ РАБОТЫ СХЕМЫ ПЕРЕДАТЧИКА

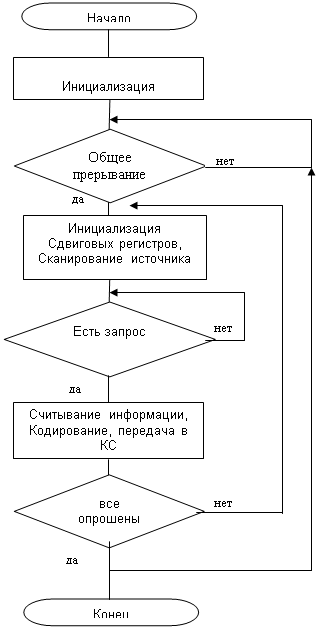

Схема передатчика изображена в приложение 3.

После появления сигнала запроса хотя бы от одного источника схема формирования общего запроса посылает прерывание на вход INT микроконтроллера. Микроконтроллер начинает последовательно опрашивать первые пары буферных регистров каждого источника на наличие запроса. Собственно последние 4 разряда первой пары регистров являются и запросом и адресом источника. Адрес источника формируется как 4-х разрядный двоичный код в котором биты устанавливаются сигналом запроса. Так при ненулевых адресных разрядах МК включает схему кодирования и снимает с нее контрольные разряды, которые вместе с информационными отправляет в КС. Этот цикл опроса повторяется для всех пар регистров схемы УР соответствующих источнику, выставившему запрос на обслуживание.

Так как шинные формирователи управляются сигналами низкого уровня , а сдиговые регистры управляющие ими имеют прямые выходы, то инверсии применяются логические элементы НЕ микросхемы К1533ЛИ2.

Перед циклом опроса источников осуществляется инициализация сдвиговых регистров , посредством которых опрашиваются источники. Через дешифратор подается сигнал RSTR высокого уровня, который сбрасывает все сдвиговые регистры, после этого

На входы всех регистров подается сигнал SETR, который по переднему фронту сигнала с дешифратора, записывает “1” в младший разряд сдвиговых регистров. Выход младшего разряда всех сдвиговых регистров не задействован, поэтому после инициализации сдвиговых регистров все шинные формирователи отключены от шины данных. После этого сдвиговые регистры готовы к работе.

Далее выбор источника осуществляется подачей кода номера источника на дешифратор. А выбор пары шинных формирователей осуществляется подачей на вход синхронизации сдвигового регистра N положительных импульсов, где N – номер пары шинных формирователей соответствующих выбранному источнику. Подача импульсов осуществляется поочередным занесением в дешифратор кода номера источника и кода 1111, выбирающего последний не задействованный выход дешифратора. По появлению положительного импульса на входе С сдвигового регистра ‘1’ из младего разряда сдвигается

вправо и на его выходе Q1 формируется “1” , которая потом инвертируется логическим элементом НЕ микросхемы DD212 и коммутирует первую пару шинных формирователей с шинной данных. При этом все остальные буферные регистры остаются в Z-состоянии.

После этого микроконтроллер запускает кодер DD230, считывает данные с шины данных и контрольные разряды с кодера и передает их в КС. После этого выбирается следующий источник и последовательность повторяется. Работа сдвиговых регистров представлена на диограмах в приложении 3.

По завершению полного цикла опроса источников и при отсутствии сигнала прерывания INT контроллер переходит в режим ожидания или может выполнять какую-либо фоновую задачу.

Для синхронизации работы приемника и передатчика микроконтроллер передает три байта со значением FFh. Такое значение посылки уникально и поэтому может использоваться как управляющая команда.

ОПИСАНИЕ РАБОТЫ СХЕМЫ ПРИЕМНИКА

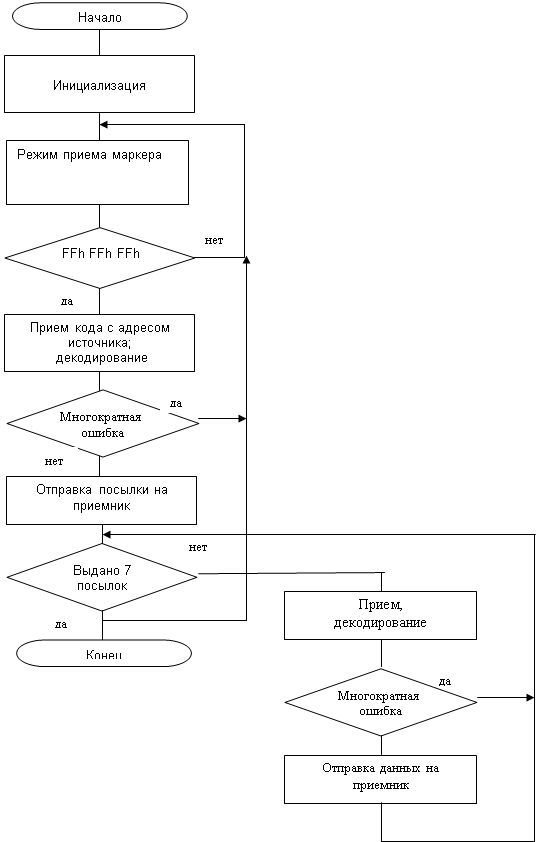

Схема приемника изображена в приложение 4.

После включения питания контроллер переходит в ожидание приема из КС команды начала цикла передачи (FF FF FF). После его получения принимается три байта информации, в которых находится адрес источника, посылает их в декодер кодов Хемминга и включает декодирование. После чего проверяет наличие многократной ошибки, считывая сигнал с декодера Хемминга MFE. При ее наличии микроконтроллер засвечивет светодиодный индикатор VD1, игнорирует все принятые данные и ждет следующей команды (FF FF FF) начала передачи. Так реализована защита от ошибок в адресе источника.

Если же в этих байтах не было обнаружено многократной ошибки, из декодированных данных выделяется адрес источника и соответственно приемника( последние 4 разряда) и посылается на дешифратор DD232. При этом устанавливается номер пары регистров приемника N=1. Работа схемы УР приемника аналогична работе этой схемы в передатчике. Только в передатчике разрешался выход буферных регистров, а в приемнике разрешается запись в них спомощью схемы коньюнкции К1530ЛИ7 .

После приема первой посылки, принимается вторая посылка из 3-х байт и декодируется. Номер пары регистров приемника N инкрементируется перед проверкой на многократную ошибку. При ее отсутствии декодированные данные записываются в пару шинных формирователей с номером N выбранного приемника. В противном случае принятые данные игнорируются, засвечивается светодиодный индикатор ошибки и ожидается следующее сообщение. Цикл приема посылок заканчивается при N=7. При приемник переходит в ожидание команды начала приема от передатчика. По принятии которой тушится светодиодный индикатор ошибки и цикл повторяется.

Таким образом при наличии ошибки во втором и последующих посылках пропускается только эта посылка, все остальные посылки продолжают приниматься. Так реализована защита от ошибки в данных.

7. Описание программного обеспечения.

Программное обеспечение МП – систем является совокупностью всех средств необходимых для разработки и решения на данной системе определенных задач, а так же для обеспечения эффективного функционирования системы.

Программы представлены в приложении (1-5).

Заключение.

Данный курсовой проект посвящён разработке системы сбора, обработки, передачи и распределения информации.

В ходе выполнения курсового проекта были:

1. Изучены теоретические сведения по представленной теме.

2. Был произведён расчет основных параметров схемы, согласно техническому заданию.

3. Был осуществлён выбор кода для кодирования информации, поступающей от источников сообщения в виде знако–буквенного кода.

4. Согласно выбранному коду, была разработана функциональная схема передающего и приёмного устройства.

5. Была разработана принципиальная схема.

Литература.

1. Тутевич В. Н. Телемеханика – М., 1985, 422с.

2. Ильин В. А. Телеуправление и телеизмерение - М., 1982, 560с.

3. Аналоговые и цифровые интегральные микросхемы. Справочник под редакцией С. В. Якубовского - М., 1985.

4. Цифровая электроника для начинающих. Г. Хокинс - М., 1986с.

5. Методические указания.

Приложение 1

Программа передатчика

Основная программа

MOV IE,#81 ;Запрет прерываний кроме INT0

MOV SCON, #DC ;Инициализация переменных и портов

MOV TMOD, #20

Sleep: HALT ;Режим ожидания прерывания

JMP Sleep

Подпрограмма обработки прерывания INT0

;Подготовка сдвиговых регистров к работе

MOV P1,#1E ;Сброс сдвиговых регистров выбором Q14 на DD

NOP

NOP

MOV R0,#0E ;Инициализация сдвиговых регистров(0Еh-кол-во источников+1)

MOV B,#30

NEXT_N:MOV P1,B

NOP

INC B

MOV A,R0

XOR A,B

AND A,#0F

JNC NEXT_N

;Начало цикла опроса источников

MOV R0,#0E

MOV B,#10

CHECK: MOV P1,B

MOV A,P2 ;Считывание байта с адресом

AND A,#0F

JZ NEXT

CALL koder&send

NEXT : INC B

MOV A,R0

XOR A,B

AND A,#0F

JNZ CHECK

RETI

Подпрограмма кодирования и передачи данных в КС

koder&send:

;-------Передача в КС 3-х байт FF FF FF

MOV R5,#07 ;Инициализация циклов по парам шинных формирователей

CLK_R: MOV R2,P0 ; считывание младшего байта данных

MOV R3,P2 ; считывание старшего байта данных

CLRB P1.4 ; Запуск кодера на формирование контрольных разрядов

NOP

NOP

NOP

MOV R4,P3 ;Считывание контрольных разрядов

MOV A,R4 ;Выделение из контрольных разрядов разрядов INT и TX

CLRB A.2

SHR A

JNC M1

SETB A.1

M1: SHR A

MOV R4,A

;-------Передача в КС R2,R3,R4

SETB P1.4 ;Устанавливается режим кодера прием информационных бит

MOV A,B

OR A,#0F ;подача низкого уровня на входы сдвиговых регистров

MOV P1,A ;выбором Q15 на дешифраторе

NOP

NOP

MOV P1,B ;Подача переднего фронта на вход N-го сдвигового регистра

DEC R5

JNC CLK_R

RET

Приложение 2

Программа приемника

Основная программа

MOV IE,#00 ;Запрет прерываний

MOV SCON, #DC ;Инициализация переменных и портов

MOV TMOD, #20

CLRB P3.7 ; Общее запрещение выдачи на приемники

START: CALL First_kadr ; Подпрограмма приема и обработки первого байта данных с адресом источника

CALL Decoder&send

JUMP START

;Подпрограмма декодирования и выдачи информации на приемник

Decoder&send:

MOV R5,#06 ;Инициализация циклов по парам шинных формирователей

CLK_R:

CALL Init_R

;Прием из КС следующих данных ( R2-данные(L), R3-данные(H), R4-контрольные )

;Пересылка принятых данных в кодер

SETB P1.6 ;настройка кодера на прием информации

CLRB P1.7

MOV A,R4

SHL A

MOV P3,A ;пересылка в кодер контрольных разрядов

MOV P0,R2 ;пересылка в кодер младшего байта данных

MOV P2,R3 ;пересылка в кодер старшего байта данных

SETB P1.6 ;Блокировка информации в кодере

SETB P1.7

NOP

NOP

CLRB P1,#6 ;Выдача исправленного кода и синдрома ошибки

SETB P1,#7

MOV P1,A ;Проверка на многократную ошибку (MFE=1)

AND A,#10

JZ NotError2

SETB P1.7 ;Индикация многократной ошибки

DEC R5 ;Цикл по парам сдвиговых регистров

JNZ M1

RET

M1: JMP Get_adders

NotError2:

CLRB P1.7 ; Выключение индикации многократной ошибки

MOV A,R6

;Выдача данных на приемник

MOV P1,R7 ; Посылка переднего фронта на сдвиговый регистр 1-го источника

NOP

NOP

MOV P1,#8E ; Посылка заднего фронта на сдвиговый регистр 1-го источника

SETB P3.7 ; Общее разрешение выдачи на приемники

NOP

NOP

CLRB P3.7 ; Общее запрещение выдачи на приемники

DEC R5 ;Цикл по парам сдвиговых регистров

JNZ M1

RET

Подпрограмма приема и обработки первого байта данных с адресом источника

First_kadr:

;-------Ожидание приема из КС команды начала передачи данных (FF FF FF)

CALL Init_R ;Подготовка сдвиговых регистров к работе

Get_adders:

;-------Прием из КС данных ( R2-данные(L), R3-данные(H), R4-контрольные )

;Пересылка принятых данных в кодер

MOV P1,#40 ;настройка кодера на прием информации

MOV A,R4

SHL A

MOV P3,A ;пересылка в кодер контрольных разрядов

MOV P0,R2 ;пересылка в кодер младшего байта данных

MOV P2,R3 ;пересылка в кодер старшего байта данных

SETB P1,#6 ;Блокировка информации в кодере

SETB P1,#7

NOP

NOP

CLRB P1,#6 ;Выдача исправленного кода и синдрома ошибки

SETB P1,#7

MOV P1,A ;Проверка на многократную ошибку (MFE=1)

AND A,#10

JZ NotError

SETB P1.7 ;Индикация многократной ошибки

JMP Get_adders

NotError:

CLRB P1.7 ;Выключение индикации многократной ошибки

;Выделение из общих данных адреса источника

MOV A,R3

AND A,#F0

SWAP A

SETB A.7 ;

MOV R7,A ;запоминание адреса в R7

;Выдача данных на приемник

MOV P1,A ; Посылка переднего фронта на сдвиговый регистр 1-го источника

NOP

NOP

MOV P1,#8E ; Посылка заднего фронта на сдвиговый регистр 1-го источника

SETB P3.7 ; Общее разрешение выдачи на приемники

NOP

NOP

CLRB P3.7 ; Общее запрещение выдачи на приемники

RET

Подпрограмма подготовка сдвиговых регистров к работе

Init_R:

MOV P1,#4E ;Сброс сдвиговых регистров выбором Q14 на DD

NOP

NOP

MOV R0,#0E ;Инициализация сдвиговых регистров(0Еh-кол-во источников+1)

MOV B,#60

NEXT_Ist:MOV P1,B

NOP

INC B

MOV A,R0

XOR A,B

AND A,#0F

JNC NEXT_Ist

RET

Приложение 3

Схема передающей стороны

Приложение 4

Схема принимающей стороны

Похожие работы

ъявляют соответствующие требования к развитию инфраструктуры рынка, особенно к ее основной части – системам сбора и передачи информации (ССПИ). Необходимое количество информации, обусловленное составом и качеством данных, темпами их поступления в ССПИ, возросло на несколько порядков. 2 Труды молодых ученых № 1, 2008 Нам представляется, что все недостатки существующих ССПИ, фактически ...

... ) 0,1098 4.4 Выбор сторожевого таймера. Т.к. работа системы происходит в автономном режиме и не предусматривает работу оператора с ней, то для случая зависания микро-ЭВМ в схему системы сбора данных добавляется интегральная микросхема MAX690AMJA – сторожевой таймер. Выполняющая две основные функции: выведение МП из состояния зависания и сброс МП при включении питания. Основные характеристики ...

... методик расчетов, инструкций. Тема 5: Проектирование информационного обеспечения. Состав и содержание проектной деятельности по ИО. 2. Проектирование информационной базы. 3. Проектирование систем классификации и кодирования. 4. Входные и выходные документы. 5. Проектирование технологического процесса обработки данных. Состав и содержание проектной документации регламентируется ГОСТом. ...

... Распределенная БД является составной частью распределенной системы обработки данных, которая включает также распределенные вычислительные ресурсы, то есть совокупность ЭВМ, распределенную систему управления этими ресурсами ѕ операционные системы, соединенные с главной ЭВМ, соединяющую их сеть передачи данных. 2.5. Организация внемашинной базы. Документооборот данного объекта представлен на схеме ...

0 комментариев