Навигация

Цифрові мікросхеми

3.7 Цифрові мікросхеми

Напівпровідникова електроніка бере свій початок у 1948 р., коли групою розробників фірми Bell був створений перший транзистор. Через 11 років інженерами фірми Texas Instruments була розроблена перша мікросхема, що складалася усього із шести транзисторів, а в 1971 р. нині всесвітньо відома фірма Intel розробила перший 4-розрядний мікропроцесор 4004, що містив більш 2000 транзисторів. Надалі мікромініатюризація електронних компонентів досягла таких темпів, що це послужило приводом для досить образного порівняння в журналі Sientific American (1982 р.): "Якби авіапромисловість в останні 25 років розвивалася настільки ж стрімко, як і промисловість засобів обчислювальної техніки, то зараз літак "Боїнг-767" коштував би 500 доларів і робив обліт земної кулі за 20 хвилин, затрачаючи при цьому 5 галонів палива". Разючі результати, досягнуті в мікроелектроніці, стали можливі завдяки не тільки новітнім напівпровідниковим технологіям, але і величезному багажеві схемотехнічних рішень, накопиченому протягом десятиліть багатомільйонною армією розроблювачів. Незважаючи на вражаючу уяву кількості транзисторів, зібраних на малюсіньких напівпровідникових кристалах, варто все-таки пам'ятати, що вони являють собою набори з найпростіших елементів, до розгляду яких ми і перейдемо.

У залежності від технології виготовлення інтегральні мікросхеми (ІМС) підрозділяються на серії (сімейства), що розрізняються фізичними параметрами базових елементів і їхнім функціональним призначенням. Найбільше поширення одержали ІМС, виготовлені по ТТЛ- і КМДН-технологіям. (ТТЛ — транзисторно-транзисторна логіка з використанням біполярних транзисторів, КМДН — з використанням комплементарних МДН-транзисторів).

Першої була випущена ТТЛ-серія SN74/SN54 (74 — комерційна, 54 — для військових застосувань). Вітчизняним аналогом серії SN74 стала популярна у свій час серія 155. У 1967 р. додатково розроблені сімейства SN74H/54H (High speed — швидкодіюча, вітчизняні аналоги — серії 131 і 130) і SN74L/54L (Low power — малопотужна, аналоги — серії 158 і 136).

У 1969 р. розроблена серія SN74S/54S (серії 531 і 530), у 1971 р. — серія SN74LS/54LS (серії 555 і 533), у 1979 р. — серія SN74F/54F фірми Fairchild (FAST — Fairchilds Advanced Schottky TTL, серія 1531), у 1980 р. — серія SN74ALS/54ALS (серія 1533), у 1982 р. — серія SN74AS/54AS (у позначеннях серій S — Schottky, LS — Low power Schottky, ALS — Advanced Low power Schottky, AS — Advanced Schottky, Advanced — удосконалена). Використання діодів з бар'єром Шоткі дозволило значно підвищити швидкодію ІМС за рахунок запобігання глибокого насичення транзисторів у ключовому режимі. Приємною для розроблювача особливістю всіх перерахованих серій є повне співпадання номерів висновків і позначення типу для ІМС однакового функціонального призначення. Наприклад, якщо SN7472 — JK-тригер, то позначення 72 буде присутнє для нього у всіх серіях. Цей же принцип використовується й у вітчизняних ІМС, хоча тип тут позначається буквами. Помітимо, що в EWB 5.0 для всіх цифрових IC уведена нумерація висновків, що істотно полегшує задачу визначення їхнього функціонального призначення при зіставленні з вітчизняними аналогами.

У бібліотеці програми EWB використовується тільки серія SN73. У число дактуючих параметрів цифрових ІМС входять наступні (у дужках приводяться позначення для EWB 3.1):

VOH, VOL — верхній і нижній рівні вихідного сигналу (напруга логічної одиниці і логічного нуля); у EWB 3.1 ці параметри відсутні;

VIH (Vih), VIL (Vil) — верхній і нижній рівні вхідного сигналу;

TPLH (Tplh) — затримка поширення сигналу при включенні (звичайно дає на рівні 1,0);

TPHL (Tphl) — затримка при вимиканні (на рівні ОД); VTG (Vth) — середня напруга спрацьовування.

Для полегшення роботи з бібліотекою нижче приводиться список вітчизняних аналогів серії SN74 (для стислості деякі повторювані символи опущені):

4 елементи 2І-НІ (цифра 2 означає двовхідний); 4 елементи 2АБО-НІ;

4 елементи 2І-НІ з відкритим колектором (дозволяють підключати навантаження з живленням більш високовольтного джерела живлення);

6 елементів НІ;

6 елементів НІ з відкритим колектором;

6 елементів НІ з відкритим колектором;

6 буферних елементів з відкритим колектором;

4 елементи 2І;

4 елементи 2І с відкритим колектором;

3 елементи ЗІ-НІ;

3 елементи ЗІ;

3 елементи ЗИ-НІ з відкритим колектором;

6 тригерів Шмітта з інверсією (мають підвищену перешкодозахищеність);

6 буферних елементів НІ;

6 буферних елементів з відкритим колектором;

2 елементи 4І-НІ;

2 елементи 4І;

2 елементи 4І-НІ з відкритим колектором;

2 елементи 4І-НІ з входом стробирования;

4 елементи 2І-НІ з відкритим колектором;

4 елементи 2АБО-НІ;

елемент 8І-НІ;

4 елементи 2АБО;

4 елементи 2І-НІ з відкритим колектором;

4 елементи 2І-НІ з відкритим колектором;

2 елементи 4І-НІ з підвищеною навантажувальною здатністю;

7442 555ИД6 дешифратор 4x10 (декодування 4-розрядного двійкового числа в десяткове);

7451 155ЛР11 елементи 2-2І-2АБО-НІ (2 елементи 2І, виходи яких підключені на кристалі ІМС до елемента 2АБО-НІ) і 2-ЗІ-2АБО-НІ (аналогічно для 2-ЗИ);

7454 155ЛР13 елемент 2-3-3-2І-4АБО-НІ (2 елементи 2І и 2 елементи ЗИ об’єднані через 4АББО-НІ);

7455 155ЛР4 Елемент 4-4І-2АБО-НІ (2 елементи 4І об'єднані через 2АБО-НІ) з можливістю об'єднання по АБО (вихідний каскад елемента 2ИЛИ-НІ має додаткові входи транзистора З — Collector і Е — Emitter, що і дозволяє здійснити об'єднання по АБО);

7472 155ТВ1 JK-тригер з елементом ЗИ на входах;

7474155ТМ2 2 D-тригери;

7475155ТМ7 4 D-тригери з прямими й інверсними виходами;

7476155ТВ7 2 JK-тригери;

7477155ТМ5 4 D-тригери з прямими виходами;

7478134ТВ14 два JK-тригери;

7486155ЛП5 4 елементи що Виключає АБО;

7490 155ИЕ2 4-розрядний асинхронний двійково-десятковий лічильник;

7491 134ИР2 8-розрядний зміщуваний регістр;

7492 155ИЕ4 4-розрядний асинхронний лічильник-дільник на 12;

7493155ИЕ5 4-розрядний асинхронний двійковий лічильник;

74107155ТВ6 2 JK-тригери з роздільною установкою нуля;

74109155ТВ15 2 JK-тригери;

74112 155ТВ9 2 JK-тригери;

74113 155ТВ10 2 JK-тригери з предустановкою нуля або одиниці;

74114 55ТВ11 2 JK-тригери з предустановкою нуля або одиниці і загальним пронуленням;

74125 155ЛП8 4 буфера з трьома станами;

74126155ЛП14 4 формуавтеля з трьома станами;

74132155ТЛЗ 4 тригери Шмітта;

74134155ЛА19 елемент 12І-НІ з трьома станами;

74138155ИД7 дешифратор-демультиплексор 3x8;

74139155ИД142 дешифратора-демультиплексора 2x4;

7414555ИД10 двійково-десятковий дешифратор з відкритим колектором;

74147555ИВЗ пріоритетний шифратор 10-4;

74148155ВЕРБ1 шифратор пріоритетів 8x3;

74150 155КП1 селектор-мультиплексор 16x1;

74151 155КП7 селектор-мультиплексор 8

74 152 155КП5 селектор-мультиплексор 8

74153 155КП2 2 селектора-мультиплексора 4х2.

74154 155ИДЗ дешифратор-демультиплексор 4x16;

74155 155ИД4 2 дешифратора-мультиплексора 2x4;

74156 555ИД5 2 дешифратора-демультиплексора 2x4 з відкритим колектором

74157 533КП16 4-розрядний селектор-мультиплексор 2x1;

74158 1533КП18 4-розрядний селектор-мультиплексор 2x1 з інверсією; 74160 155ИЕ9 4- розрядний синхронний двійково-десятковий лічильник;

74162 1533ИЕ11 4-розрядний синхронний десятковий лічильник;

74163155ИЕ18 4-розрядний синхронний реверсивний двоїчно-десятковийлічильник;

74164 155ИР8 8-розрядний регістр зрушення з рівнобіжними виходами;

74165 555ИР9 8-розрядний регістр зрушення з рівнобіжним введенням інформації;

74166 555ИР10 8-розрядний регістр зрушення із синхронним рівнобіжним уведенням;

74169155ИЕ17 4-розрядний двійково- синхронний реверсивний лічильник;

74173 155ИР15 4-розрядний регістр із трьома станами;

74174 155ТМ9 6 D-тригерів;

74175 155ТМ8 4 D-тригери; 74181 155ИПЗ 4-розрядне АЛУ;

74191 155ИЕ13 синхронний реверсивний двійковий лічильник;

74192 155ИЕ6 двійково-десятковий реверсивний лічильник;

74194 155ИР11 4-розрядний універсальний регістр зрушення;

74195 155ИР12 4-розрядний регістр зрушення з рівнобіжним уведенням;

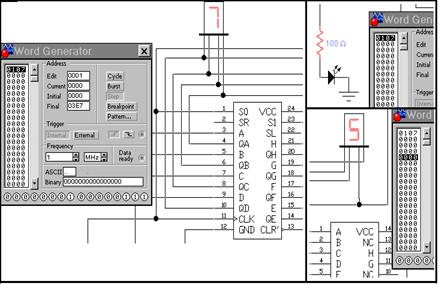

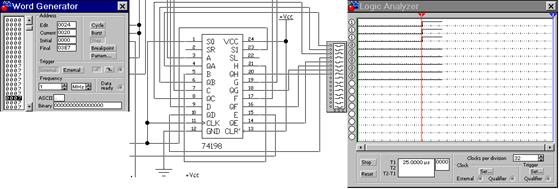

74198 155ИР13 8-розрядний універсальний регістр зрушення;

74240 155АПЗ 8 буферів з інверсією і трьома станами;

74241 155АП4 8 буферів із трьома станами; 74244 155АП5 2x4 буферів із трьома станами;

74251 155КП15 селектор-мультиплексор 8x1 із трьома станами;

74253 155КП12 2 селектора-мультиплексора 4x1 із трьома станами;

74257 155КП11 4 селектора-мультиплексора 2x1 із трьома станами;

74258 155КП14 4 селектора-мультиплексора 2x1 із трьома станами й інверсією;

74273 155ИР35 8-розрядний регістр з установкою нуля;

74279 555ТР2 4 RS-тригера-засувки;

74280 1533ИП5 9-розрядна схема контролю парності;

74283 155ЇМ6 4-розрядний повний суматор із прискореним переносом;

74298 155КП13 4 2-вхідних мультиплексора з запам'ятовуванням;

74353 555КП17 здвоєний мультиплексор 4x1 з інверсією і трьома станами виходу;

74365 155ЛП10 6 повторювачів з керуванням по входах і трьома станами

74367 155ЛП11 6 повторювачів з роздільним керуванням по входах і трьома станами;

174373 155ИР22 8-розрядний буферний регістр із трьома станами і потенціальним керуванням;

74347 155ИР23 8-розрядний буферний регістр із трьома станами й імпульсним керуванням;

174377 155ИР27 8-розрядний регістр із дозволом запису;

74395 533ИР25 4-розрядний рівнобіжний регістр зрушення.

Посилання в цьому переліку на ІМС інших серій викликано їхньою відсутністю в серії 155, однак тут це не має істотного значення, оскільки мова йде тільки з'ясуванні функціонального призначення висновків.

Цифрові ІМС КМДН-серії одержали назву від свого базового елемента,

у якому використовується так називана комплементарна пара з двох МДН-транзисторів різної провідності. Такі ІМС характеризуються малим споживанням потужності в статичному режимі (0,02..Л мквт на вентиль), великим діапазоном живлячих напруга (3...18 У), високим вхідним опором(до десятків Тім), великою навантажувальною здатністю, незначної залежності характеристик від температури, малими розмірами транзисторів у інтегральному виконанні і, як наслідок, більш високим ступенем інтеграції по порівнянні с ТТЛ-мікросхемами.

Перші ИМС по КМДН-технології розроблені фірмою RCA у 1968 р. Ця серія мала назву CD4000 (вітчизняні аналоги — серії 164 і 176), потім пішли серії CD4000A, CD4000B (вітчизняні аналоги — 564, 561 і 1561) а також МС14000А и МС14000В фірми Motorola і 54НС фірми Nationa Semiconductor у 1981 р. (вітчизняний аналог — серія 1564). У програмі EWВ у якості бібліотечних використовуються ІМС фірми RCA, більшість яких приведено в наступному переліку:

4000 176ЛП4 2 елементи З АБО-НІ і І-НЕ;

4001561ЛЕ5 4 елементи 2АБО-НІ;

4002561ЛЕ6 2 елементи 4АБО-НІ;

4008561ЇМ1 4-розрядний повний суматор;

4009176ПУ2 6 перетворювачів рівня з інверсією;

4010176ПУЗ 6 перетворювачів рівня без інверсії;

4011561ЛА7 4 елементи 2І-НІ;

4012561ЛА8 2 елементи 4І-НІ;

4013561ТМ2 2 D-тригери;

4015561ИР2 2 4-розрядних зміщуваних регістри;

4017561ИЕ8 десятковий лічильник з дешифратором;

4019561ЛС2 4 елементи І-ІЛІ;

4023561ЛА9 3 елементи ЗІ-НІ;

4024176ИЕ1 6-розрядний двійковий лічильник;

40251561ЛЕ10 3 елементи ЗАБО-НІ;

4027561 ТВ1 два JK-тригери;

4028561ИД1 двійково-десятковий дешифратор;

40294030561ЛП2 4 елементи ЩО ВИКЛЮЧАЄ АБО;

4040 1561ИЕ20 12-розрядний двійковий лічильник;

4042 561ТМЗ чотири D-тригери;

4043 561ТР2 чотири RS-тригери;

4049 561ЛН2 6 елементів НЕ;

4050 561ПУ4 6 перетворювачів рівня;

4066 561КТЗ 4 перемикачі (цифрового або аналогового сигналу);

4070 1561ЛП14 4 елементи ЩО ВИКЛЮЧАЄ АБО;

4081 1561ЧИ2 4 елементи 2И;

4502 561ЛН1 6 стробіруємих інверторів;

4516 561ИЕ11 4-розрядний реверсивний лічильник;

4520 561ИЕ10 2 4-розрядних лічильники;

4556 1561ИД7 двійковий декодер-демультиплексор.

Приведемо систему позначень входів і виходів найпростіших логічних елементів, використовуваних у програмі EWB. Позначення для ТТЛ-серії приводяться в перших круглих дужках, для КМДН — у других, при однакових позначеннях — без дужок:

Висновок для живлення — (Ucc), (Udd); Загальний висновок — (GND), (Uss); Висновок не підключений — NC;

Входи —(А, У, С...), (I); Виходи — (Y), (ПРО); Вхід стробіровання — G.

Приведемо приклад позначення послідовності висновків для 2-вхідних логічних елементів:

(1А IB 1Y, 2А 2В 2Y, ЗА ЗВ 3Y, 4А 4В 4Y), (II12 01,13 14 02,15 16 03,17 18 04).

Для більш складних ІМС визначення функціонального призначення їхніх висновків доцільно проводити шляхом зіставлення з вітчизняними аналогами [4—10]. Для більш оперативної орієнтації при роботі з цифровими ІМС приведемо перелік найбільш розповсюджених мнемонічних позначень на їхніх функціональних схемах і в таблицях станів [5, 7].

А = У (Parity) — вихід рівності операндів А і В.

A/S (Asynchro/Synchro) — вхід асинхронного і синхронного режимів.

B/D (Binary/Decimal) — вхід переключення рахунку з двійкового на десятковий.

З (Clock input) — вхід тактових імпульсів.

CD (Count down) — вхід тактових імпульсів на зменшення рахунку (у реверсивних лічильниках).

Сс (Count up) — вхід тактових імпульсів на збільшення рахунку.

СЕ (Clock enable) — вхід дозволу для тактових імпульсів.

СІРИЙ (Count enable parallel) — вхід рівнобіжного нарощування розрядів лічильника.

СЕТ (Count enable trickle) — вхід дозволу рахунку при нарощуванні розрядів лічильника.

CLR (Clear) — вхід скидання.

Cn (Carry in) — вхід для розряду переносу.

CS (Chip select) — вибір кристала; визначає доступ до однієї з ІМС пристрою.

D (Data input) — вхід даних тригера, лічильника, регістра.

DSI (Data serial input) — вхід послідовних даних.

DS(Data select) — вхід вибору даних.

DL, DR (Data left, Data right) — входи для послідовного завантаження (регістра) ліворуч, праворуч.

DSL, DSR (Data shift left, Data shift right) — входи для зрушення даних вліво, вправо.

Е (Enable) — вхід сигналу дозволу.

ЄС (Enable count) — вхід сигналу дозволу рахунку.

ЇЇ (Enable even) — вхід сигналу дозволу, рахунковий.

El (Enable input) — висновок ІМС, по якому дається дозвіл на прийом даних.

НЕЮ (Enable input/output) — висновок для одночасного дозволу по входу і виходу.

ЕО (Enable output) — висновок для дозволу по виходу.

LSB (Least significant bit) — молодший значущий розряд (МЗР).

М (Mode control) — вибір режиму "Арифметика-логіка" в АЛУ.

РЕ (Parallel enable load) — вхід дозволу рівнобіжного завантаження.

P/S (Parallel/serial) — вхід переключення режимів рівнобіжного або послідовного завантаження.

R (Reset) — асинхронне скидання даних.

RE (Read enable) — вхід дозволу читання.

S (Set) — установка тригера, лічильника, регістра.

S (Set enable) — дозвіл попереднього рівнобіжного запису.

SI (Serial input) — вхід послідовний.

SIR, SIL (Serial input right, SI left) — вхід послідовний праворуч, ліворуч.

SR (Synchro reset) — вхід скидання синхронно з тактовим імпульсом.

ТС (Terminal count) — вихід закінчення рахунка.

TCD (Terminal count down) — те ж, на зменшення рахунка.

TCU (Terminal count up) — те ж, на збільшення рахунка.

Розглянемо базові елементи, з яких набираються самі складні цифрові ІМС.

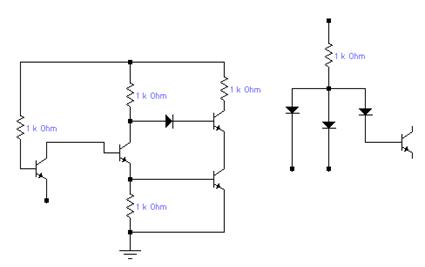

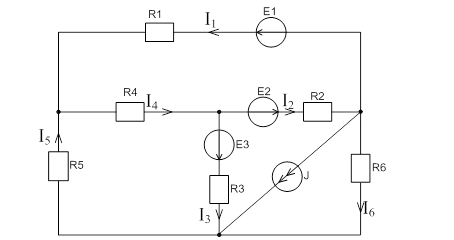

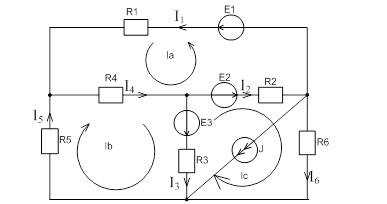

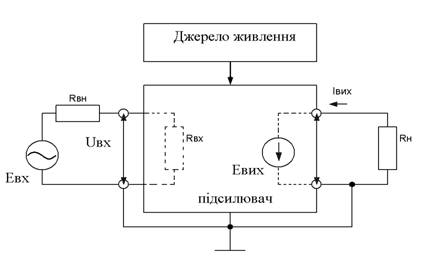

Схема базового елемента (вентиля) ТТЛ-серії показана на мал. 3.70, а. Вона має три основних каскади: вхідний на транзисторі VT1, фазорозподільний на транзисторі VT2 з можливістю реалізації на ньому функції АБО і вихідний підсилювач на транзисторах VT3 і VT4 [49].

Як транзистор VT1 використовується багатоемітерний транзистор, відсутній у бібліотеці EWB. Принцип дії вхідного каскаду легко зрозуміти, якщо переходи база-емітер представити у виді діодів, як показано на мал. 3.70, б. Тоді очевидно, що якщо вхідні діоди (входи А, В) підключені до шини з високою напругою (3...5 В), те струм резистора R1 потече через коллекторний діод у базу транзистора VT2. Якщо ж хоча б один із вхідних діодів підключений до заземляючої шини або до шини з низькою напругою, то в такий же спосіб, виявиться підключеним і резистор R1. На базі транзистора VT1 при цьому буде низька напруга (перевищуюче вхідне на величину напруги база-емітер) і базовий струм транзистора VT2 стане рівним нулеві.

Таким чином, при високих напругах на обох входах на колекторі транзистора VT1 також буде висока напруга; якщо ж хоча б на один із входів подана близька до нуля напруга, то на колекторі VT1 установиться низька напруга, а це означає, що вхідний транзистор виконує логічну функцію І.

Фазорозподільний каскад виконаний на транзисторі VT2 і резисторах R2, R3,у яких приблизно рівні опори (близько 0,25...0,33 від R1). При цьому насичення транзистора VT2 досягається вже при досить малому коефіцієнті підсилення струму. Коли на всі логічні входи схеми подана висока напруга, через перехід бази-колектора транзистора VT1 у базу VT2 подається керуючий струм, у результаті чого VT2 відкривається. При цьому напруга в точці Е може зрости тільки до напруги база-емітер транзистора VT4, а напруга в точці З (на колекторі VT2) знизиться до значення, рівного сумі напруг відкритих діода VD і транзистора VT3. Якщо хоча б на один з логічних входів подається низька напруга (сигнал логічного нуля), то транзистор VT1 відкривається, відключаючи керуючий базовий струм транзистора VT2, у результаті чого VT2 закривається і через резистори R2, R3 протікає тільки струм витоку, тому напруги в точках Е и С близькі до нуля і Ucc відповідно. Логічна функція АБО може бути реалізована при рівнобіжному з'єднанні двох або більш подібних фазорозподільних каскадів (у точках С і Е).

Основним транзистором вихідного каскаду є транзистор VT3. Коли на входи А, В (мал. 3.70, б) подані висока напруга, транзистори VT2 і VT3 відкриті. У цьому випадку напруга в точці З буде дорівнювати, як зазначено вище, напрузі двох відкритих р-n-переходів. Якщо тимчасово виключити з розгляду транзистор VT4 і розглядати тільки ланцюг, що містить діод VD і транзистор VT3, то напруга в точці S буде нижче напруги в крапці З на величину, рівну напрузі на двох р-n-переходах. При цьому напруга на базі транзистора VT4 буде достатнім (саме за рахунок діода VD) для підтримки його у відкритому стані, тобто на виході S буде діяти напруга, рівне напрузі насичення транзистора VT4 (сигнал логічного нуля).

Якщо хоча б на один із входів вентиля А або В подане низька напруга, то транзистори VT2 і VT4 закриті. Через резистор R2 тече тільки струм витоку транзистора VT2, тому напруга в крапці З близько до напруги харчування Vcc, а потенціал у крапці S нижче потенціалу З на величину спадання напруги на двох відкритих переходах. Спаданням напруги на резисторі R2 від базового струму транзистора VT4 можна зневажити. Таким чином, при наявності хоча б на одному з входів вентиля низької напруги вихідна напруга вентиля нижче напруги живлення на спадання напруги на двох р-n-переходах. У різних серіях ТТЛ використовуються різні схеми вихідних каскадів, однак завжди між шиною Ucc і виходом S мається два послідовно включених р-n-переходи. Резистор R4 служить для захисту транзистора VT3 при закорочуванні виходу S на "землю".

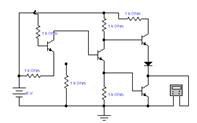

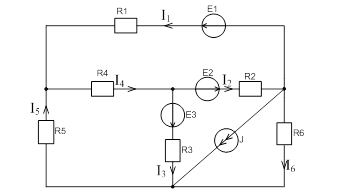

Базовий елемент серії 54/74 (155) (мал. 3.71) небагато відрізняється від розглянутого (мал. 3.70). Основна відмінність полягає в тім, що діод VD включений у емітерний, а не в базовий ланцюг транзистора. На мал. 3.71 показаний також підключений до виходу мультиметр і імітатор вхідного сигналу, виконаний на ключі Z. У положенні ключа, показаному на малюнку, на вході формується сигнал логічної одиниці. При перекладі ключа в інше положення вхід вентиля підключається через резистор Ri до загальної шини, у результаті чого на вході вентиля формується сигнал логічного нуля.

а) б)

Мал.3.70. Базова схема елемента ТТЛ-серії (а) і еквівалентна схема багатоемітерного транзистора(б).

Мал.3.71. Базова схема елемента серії 54/73.

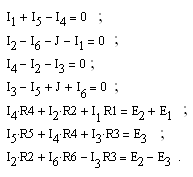

а) б)

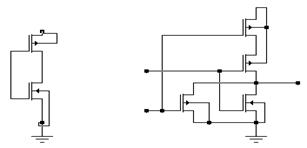

Мал.3.73. Базова схема інвертора (а) і елемента АБО-НІ (б) КМДН-серії.

Розглянемо тепер базові елементи ІМС КМДН-серії. Найпростішим елементом цієї серії є КМДН-інвертор, схема якого показана на мал. 3.72, а. Вона складена з КМДН-транзисторів різного типу провідності. Транзистор n-типу підключений джерелом до нульового потенціалу, транзистор р-типу до позитивної шини джерела живлення. Схема реалізує логічну операцію НІ і забезпечує роботу в режимі позитивної логіки. У такому режимі працюють більшість ІМС КМДН-серій.

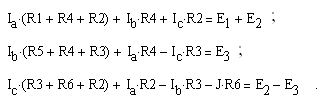

Для реалізації функції АБО-НІ (мал. 3.72, б) використовується рівнобіжне включення МДН-транзисторів n-типу і послідовне (ярусне) включення транзисторів p-типу. Крім того, кожний із вхідних транзисторів n-типу зв'язаний по затворі з транзистором р-типу. Для реалізації функції І-НІ (мал. 3.73) napaлельно включаються транзистори р-типу і послідовно — транзистори n-типу. При подачі на вхід схеми АБО-НІ сигналу X1 високого рівня відкриється транзистортор VT1 і закриється VT3. У результаті на виході схеми формується низький рівень напруги. При подачі на обидва входи (X1 і Х2) сигналів низького рівня транзистори VT1 і VT2 закриваються, але відкриваються транзистори VT3 і VТ4, у результаті чого на виході схеми напруга буде близькою до напруги живлення Ucc. Таким чином, перезаряд ємності навантаження, що підключається між вихідним затискачом Y і загальною шиною, завжди здійснюється через відкритий транзистор р-або n-типу, що підвищує швидкодію схеми.

Потужність, споживана схемою на КМДП-транзисторах, витрачається в основному під час перехідного процесу на заряд вихідних паразитних ємкостей схеми і власних ємкостей транзистора. Тому зі збільшенням частоти переключення, а також при збільшенні вихідної еквівалентної ємності споживана потужність зростає відповідно до вираження Рдин = 2CxFxUсс2 де З — еквівалентна ємність навантаження; F — робоча частота; Ucc — напруга джерела живлення.

У статичному режимі споживана потужність визначається напругою живлення і струмами витоку закритого МДН-транзистора. Для зменшення потужності, споживаної в динамічному режимі, необхідно в першу чергу знижувати їм навантаження.

Мінімальна напруга живлення схеми на КМДН-транзисторах визначається напругою відмикання р-канального транзистора, тому що воно більше, ніж напруга відмикання n-канального транзистора. Природно, що живлення вибирається більше напруги відмикання. Це забезпечує схемі на КМДН-транзисторах високу завадостійкість і швидкодію.

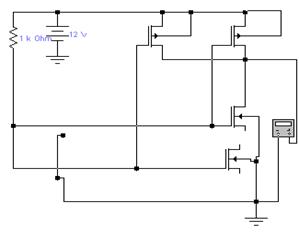

Мал.3.73. Схема базового елемента І-НІ КМДН-серії.

Схема І-НІ на мал. 3.73 містить імітатор вхідного сигналу на ключах А, В і мультиметр для перевірки правильності функціонування схеми. У положенні перемикачів, показаних на схемі, на входи А, В подаються сигнали логічної одиниці. При цьому транзистори VT1, VT2 будуть закриті, а транзистори VT3, VT4 — відкриті і на виході Y мультиметром буде фіксуватися низький рівень сигналу логічного нуля. Досить один з вимикачів перевести в інше положення й один із двох нижніх транзисторів закриється, при цьому на виході Y буде фіксуватися високий рівень сигналу логічної одиниці, що і відповідає логіці роботи І-НІ.

Контрольні питання н завдання

1. Коли і де були створені перша мікросхема і перший мікропроцесор?

2. Що із себе представляють ТТЛ- і КМДН-серии цифрових ІМС?

3. Що дозволило радикально підвищити швидкодію ТТЛ-серії?

4. У чому полягає розходження в позначеннях цифрових ІКС закордонного й вітчизняного виробництва?

5. Яку основну перевагу мають цифрові КМДН-мікросхеми в порівнянні з ТТЛ і на яких частотах воно виявляється?

6. Які функції виконує багатоемітерний транзистор у ІМС ТТЛ-серії?

7. З опису процесу формування на виході S сигналу логічного нуля в схемі вентиля на мал. 4.70, а не зовсім ясно, у якому стані при цьому знаходиться транзистор VT3 — у відкритому або закритому. Для перевірки необхідно при логічній одиниці на входах А, У виміряти за допомогою мультиметра напругу на колекторі VT3, попередньо переконавшись, що на виході S сигнал логічного нуля. Якщо ця напруга дорівнює Ucc = + 5 В, то це означає, що через резистор R4 струм не тече і, отже, транзистор VT3 закритий. Якщо це так, спробуйте пояснити, чому?

8. Перевірте правильність функціонування схеми на рис 4.73.

Похожие работы

інюю промені) – технічні засоби радіозв'язку, зокрема призначені для віщання радіопрограм. Радіотехніка – область науки, що досліджує генерацію, випромінювання і прийом електромагнітних коливань і хвиль радіочастотного діапазону, а також область техніки, що займається розробкою, виготовленням і застосуванням пристроїв і систем, що генерують, випромінюючих і таких, що приймають електромагнітні ...

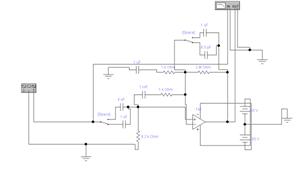

... ГРП М1-61ШУ2 Кео.364.006 ДТУ 2 XXXXXXX ПЕ Змін Літ № докум Підпис Дата Канал послідовної передачі даних Перелік елементів Літ Лист Листів Розроб. Xxxxxxx. К 1 1 Перевірив Xxxxxxx ...

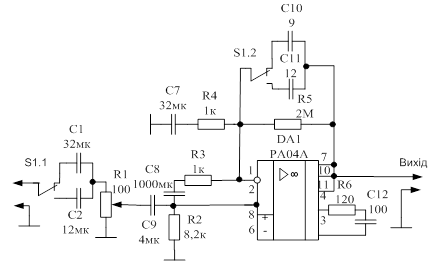

... двокаскадні; – однокаскадні. Анотація УДК.631.317.18 Сисюк М.А. Підсилювач вертикального відхилення Українська мова, 23 стор., 10 іл. В даному курсовому проекті розроблений підсилювач вертикального відхилення осцилографа, діапазон напруг якого лежить у межах від 100мВ до 200B, а діапазон частот лежить у межах від 1кГц до 10МГц. Такі потужні підсилювачі використовуються для підсилення ...

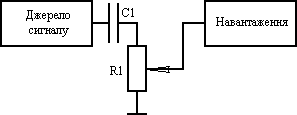

... мінімальний завал. Отже розрахуємо конденсатор С1 у відповідності до опору гучності та необхідного завалу: Отже, обирається конденсатор С1 К50-15-32 мкФ. 2.2 Розрахунок підсилювача потужності на ІМС Резистор R2, що формуватиме вхідний опір буде типу С1-4-0,25 Вт-8,2 кОм2%. В типовій схемі включення даної мікросхеми [рисунок 1.2] резистори в зворотньому зв'язку розраховані на коеф ...

0 комментариев