Навигация

СИНТЕЗ І ВЕРИФІКАЦІЯ VHDL МОДЕЛІ КОМП’ЮТЕРА

3. СИНТЕЗ І ВЕРИФІКАЦІЯ VHDL МОДЕЛІ КОМП’ЮТЕРА

Подамо структурну VHDL модель комп’ютера. Комп’ютер складено з тьох вузлів, а саме, з процесора “Гном”, пам’яті програм і пам’яті даних. Всі вузли подані відповідними VHDL компонентами. Уведеними сигналами (дротами, шинами тощо) компоненти поєднано в комп’ютер.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- project top file

entity gnome_mcu is

Port ( clk : in std_logic;

Reset : in std_logic;

we_view : out std_logic;

carry_view : out std_logic;

oe_view : out std_logic;

sel_ram_view : out std_logic;

pc_view : out std_logic_vector (6 downto 0);

acc_view : out std_logic_vector (3 downto 0);

data_view : out std_logic_vector(7 downto 0);

addr_view : out std_logic_vector(6 downto 0);

ir_view : out std_logic_vector(7 downto 0));

end gnome_mcu;

architecture structural of gnome_mcu is

component gnome port

(

clk: IN STD_LOGIC;-- clock

reset: IN STD_LOGIC;-- reset control input

address: OUT STD_LOGIC_VECTOR (6 DOWNTO 0); -- ext memory addr

data: INOUT STD_LOGIC_VECTOR (7 DOWNTO 0); -- ext memory data bus

--csb: OUT STD_LOGIC;-- active-low chip-select for external RAM

web: OUT STD_LOGIC;-- active-low write-enable for external RAM

oeb: OUT STD_LOGIC;-- active-low output-enable for external RAM

sel_ram: out std_logic;

carry_out : out std_logic;

pc_out: OUT STD_LOGIC_VECTOR (6 DOWNTO 0);

ir_out: out std_logic_vector (7 downto 0);

acc_out: out std_logic_vector (3 downto 0)

);

end component;

component rom port (

sel_ram : in std_logic;

oe : in std_logic;

ADDR : in std_logic_vector (6 downto 0);

DATA : inout STD_LOGIC_VECTOR (7 downto 0));

end component;

component ram port

(clk : in std_logic;

sel_ram : in std_logic;

oe : in std_logic;

we : in std_logic;

address : in std_logic_vector(6 downto 0);

data : inout std_logic_vector(7 downto 0));

end component;

signal w_clk: std_logic;

signal w_reset: STD_LOGIC;

signal b_address: STD_LOGIC_VECTOR (6 DOWNTO 0);

signal b_data: STD_LOGIC_VECTOR (7 DOWNTO 0);

--signal w_csb: STD_LOGIC;-- active-low chip-select for external ROM/RAM

signal w_web: STD_LOGIC; -- active-low write-enable for external RAM

signal w_oeb: STD_LOGIC; -- active-low output-enable for external ROM/RAM

signal w_sel_ram: std_logic;

begin

oe_view <= w_oeb;

sel_ram_view <= w_sel_ram;

w_clk <= clk;

w_reset <= reset;

data_view <= b_data;

addr_view <= b_address;

we_view <= w_web;

U1: gnome port map (

clk => w_clk,

reset => w_reset,

address =>b_address,

data => b_data,

--csb => w_csb,

web => w_web,

oeb => w_oeb,

sel_ram => w_sel_ram,

carry_out => carry_view,

pc_out => pc_view,

ir_out => ir_view,

acc_out => acc_view);

U2: rom port map (

sel_ram => w_sel_ram,

oe => w_oeb,

ADDR => b_address,

DATA => b_data);

U3: ram port map (

clk => w_clk,

sel_ram => w_sel_ram,

oe => w_oeb,

we => w_web,

address => b_address,

data => b_data);

end structural;

В відповідному розділі пояснювальної записки потрібно подати:

-текст моделі з коментарями державною мовою;

-побудовану на основі VHDL моделі структурну схему комп’ютера;

-додаткові роз’яснення щодо семантики VHDL моделі;

-витяги з протоколів синтезу, імплементування, програмування і діаграми часового симулювання виконання комп’ютером тестової програми.

Подамо, як приклад, витяг з протоколу імплементування комп’ютера на ПЛІС Віртекс-2.

Device utilization summary:

Number of External IOBs 40 out of 88 45%

Number of LOCed External IOBs 0 out of 40 0%

Number of SLICEs 64 out of 256 25%

Number of BUFGMUXs 1 out of 16 6%

Number of TBUFs 32 out of 128 25%

Отже, проект вимагає для реалізації 64 слайси. Це число буде меншим для коротших програм і більшим для довших. В нас можлива довжина програми в 64 інструкції.

Наступний витяг з протоколу імплементування засвідчує швидкодію (на цільовій ПЛІС Віртекс-2).

6322 items analyzed, 0 timing errors detected.

Minimum period is 11.235ns.

Maximum delay is 14.267ns.

Отже за оцінкою, комп’ютер спроможний тактуватися максимальною частотою 88 МГЦ, що на трьохциклових інструкціях забезпечувати швидкодію майже 30 MIPS.

Далі подамо розташування апаратури комп’ютера в ПЛІС Віртекс-2 і копію вікна навігатора з нашим проектом.

Текстом пояснювальної записки студент має роз’яснити інформацію, що містить вікно FloorPlanner. Щодо вікна навігатора проектів в пояснювальній записці теж треба подати роз’яснення.

Аналізом отриманих часових діаграм потрібно підтвердити, що функціонування комп’ютера відповідає тестовій програмі.

Подамо два фрагменти часової діаграми функціонування комп’ютера. Симулятор запущено на часове симулювання наступними командами:

1.Force clk 0 0, 1 50ns –repeat 100ns (тактові імпульси з частотою 10 МГц, що розпочинаються нулем).

2.Force reset 1 0. 0 70ns (форсувати скид одиницею від початку, а на 70-й нс перевести його до неактивного одиничного стану).

3.Run 6 us ( викликати симулювання перших 6-ти мікросекунд: аби встигла виконатися наша програма на частоті 10 МГц).

Детальним аналізом часових діаграм (навести його письмово) підтверджують коректне функціонування переходу на кінці програми.

За допомогою утиліти Xpower зі складу САПР WebPack визначаємо споживану розробкою потужність.

Для визначення параметричної надійності розробки обчислюють обернену величину (середній час наробки на відмову, або MTBF) суми пронормованих лямбда-параметрів всіх складових проекту (разом із конекторами, друкованими платами і пайками). Це виконують після розробки принципової схеми емулятора.

Розробка принципової схеми прототипної плати

Як аналогом розробки можна скористатися відомими прототипними платами. Сайт www.xess.com надає описи і принципові схеми низки прототипних плат з різними цільовими ПЛІС.

Розглянемо прототипну плату XS40. Нам мікроконтролер uC8031непотрібен. Його можна виключити зі складу емулятора. Водночас потрібно правильно призначити номери контактів нашої цільової ПЛІС наявним сигналам. Зауважимо, що емулятор XS40 містить зовнішню статичну пам’ять, яку теж можна вилучити. Отже, розробка за аналогією зводиться до спрощень і до переназв номерів контактів. Інформацію щодо цільової ПЛІС (datasheet) Віртекс-2/Cпартан-2/Спартан-2Е отримують на сайті фірми Ксайлінкс або ж від керівника проекту.

4 ІНСТАЛЯЦІЯ САПР Xilinx WebPack

Спочатку інсталюють САПР Xilinx WebPack, потім - симулятор ModelSim фірми Model Technologies. Інсталювати симулятор непотрібно для WebPack 8.2i. Він містить вбудований симулятор. Після кожного кроку інсталяції комп’ютер перезапускають. Ще до інсталяції симулятора записують на диск безкоштовну студентську ліцензію. Потім зі стартового меню інстальованого симулятора викликають менеджер ліцензії симулятора, якому вказують місце розташування на диску ліцензії, а потім наказують перевірити дієспроможність ліцензії. Роботу з менеджером ліцензії завершують. Ще одне перезавантаження і система готова до використання.

Використана література

1.Троценко В.В. – VHDL модель комп’ютера ; методичні вказівки до курсового проекту 21с.

2.www.xilinx.com

3.www.xess.com

4.www.model.com

Похожие работы

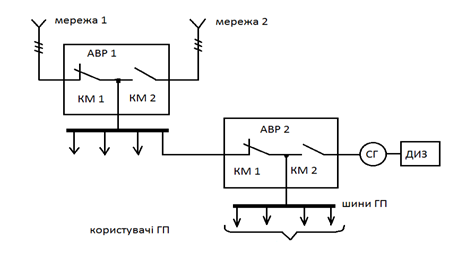

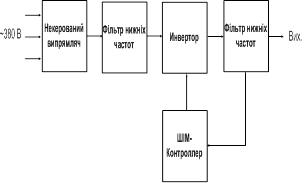

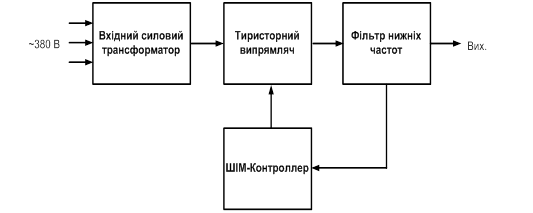

... на автономне (не пов'язану з мережею змінного струму) навантаження. Як навантаження автономного інвертора може виступати як одиничний споживач, так і розгалужена мережа споживачів. 2.1 Джерела безперебійного та гарантованого електроживлення Під гарантованим живленням (ГЖ) варто розуміти забезпечення апаратури зв'язку й засобів автоматизації електроенергією в будь-яких режимах роботи системи ...

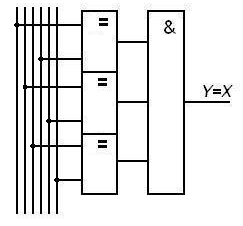

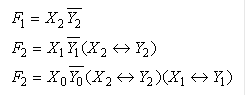

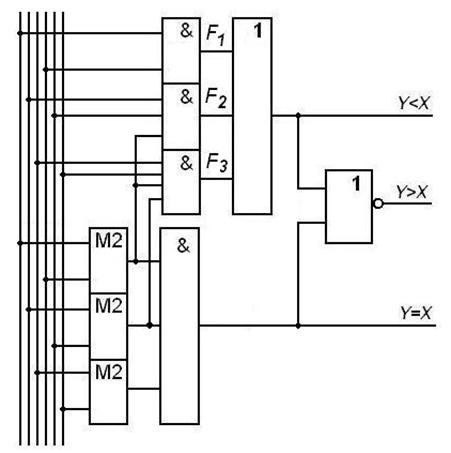

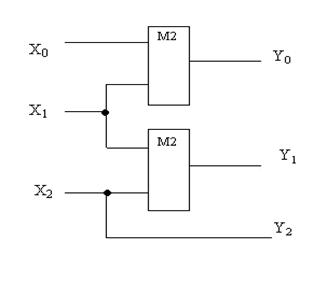

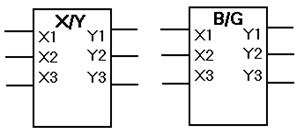

... замість елементів рівності суматори за модулем 2. Отримана схема компаратора трирозрядних кодових слів зображена на рис. 3. Рис. 3. Схема компаратора трирозрядних кодових слів 2. Перетворювачі кодів та схеми контролю. 2.1. Перетворювачі кодів. У цифрових пристроях часто виникає необхідність перетворення інформації з одного двійкового коду в інший. Коди, що ...

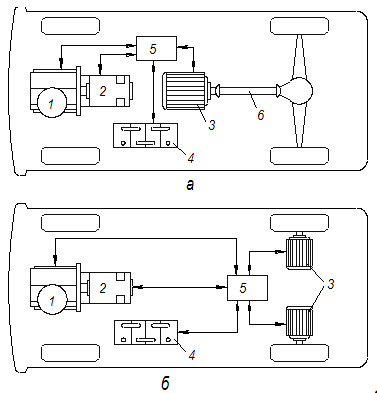

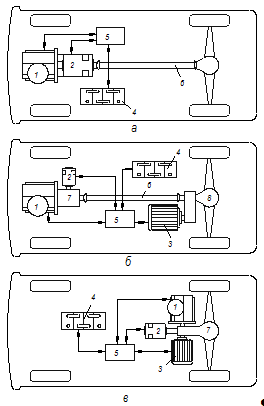

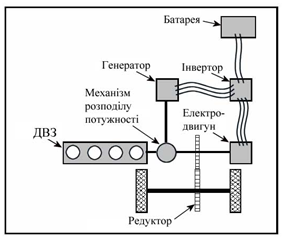

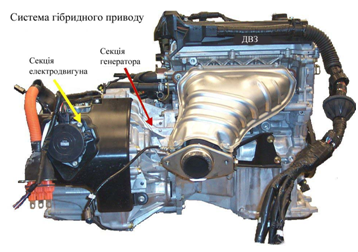

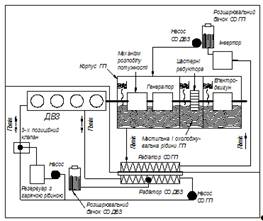

... іля при гальмуванні і русі накатом; - відмова від деяких традиційних вузлів (зчеплення, стартер, коробка передач). На сьогоднішній час створено багато автомобілів з комбінованими енергетичними установками, проте ще далеко не всі потенційні можливості таких схем розкриті. Для досягнення максимальної ефективності комбінованої енергоустановки необхідно розробити оптимальні алгоритми керування ...

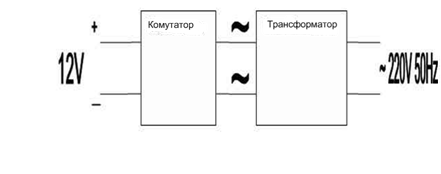

... інверторів живлення, по відношенню до лінійних, є їхньою експлутаційною перевагою. Менші витрати матеріалів ведуть до ресурсозберігання. В даний час на світовий ринок поставляються інверторні джерела живлення різних потужностей призначені як для окремих вживань, так і універсальні. Одночасно зросла кількість фірм, що виготовляють імпульсні джерела живлення. Проведений аналіз публікацій та ринку ...

0 комментариев