Навигация

Схемотехническое проектирование

3. Схемотехническое проектирование

3.1 Блок опорных частот

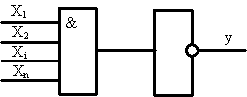

Поскольку сложение происходит последовательно, то сигналы надо считывать в определенные промежутки времени. Для этого вместе с информационным сигналом нужно подавать сигнал «тактирующий». Оба сигнала будут идти на соответствующие входы триггера, что обеспечит синхронную подачу информации. Нужно также указывать какое действие выполнять в каждом такте в зависимости от его номера, т.е. 1‑й, 2‑й и так далее до шестнадцатого. Роль указателя выполняет 4‑х разрядный двоичный счетчик: подавая 4 выходных сигнала счетчика на элемент «И» образуются единицы или нули на выходах блока опорных частот для соответствующего номера такта в том случае, если тактовый сигнал подается синхронно с сигналами счетчика.

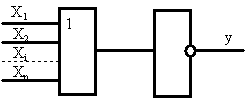

Блок опорных частот – функциональный блок, который падаёт 16 тактовых сигналов синхронно с сигналами счетчика от 0 до 15. Фактически он является управляющим устройством сумматора. Логика работы блока опорных частот основывается на элементе ИЛИ-НЕ (DD2:1). На один из входов элемента ИЛИ-НЕ подается управляющий сигнал X, другой вход соединяется с выходом элемента. Для запуска счетчика на управляющие входы (C1, C2) подается 10. Причем импульс 1 должен чуть превышать задержку элемента ИЛИ-НЕ. Тогда после подачи на вход Х единицы на выходе ИЛИ-НЕ установится ноль. К тому времени как Х снова обратится в ноль, получится ситуация, когда оба входа ИЛИ-НЕ равны нулю, тогда на выходе через определенную задержку, составляющую пол такта, установится 1, а значит и на входе тоже установится 1. Но раз на входе 1, тогда на выходе снова через следующие пол такта установится 0. Для повышения устойчивости единицы блока опорных частот на выходе ИЛИ-НЕ устанавливается повторитель DD4:1.

Тактирующий импульс будет продолжаться до бесконечности, если не создать блокировки. Для этого используется третий вход ИЛИ-НЕ (DD2:1). Как только выполнится 14 счет, на третий вход ИЛИ-НЕ подается 1, и тактирующий сигнал блокируется, D‑триггер DD3:2 не позволит ему снова установиться в 0. Поскольку счетчик имеет задержку, превышающую один такт, то он успеет выполнить также и 15-й счет.

В начальный момент времени пока на X еще не подалась 1, на выходах ИЛИ-НЕ будет неопределенное состояние, выходы счетчика и тактирующий сигнал, тоже имеют неопределенное состояние. Для того чтобы не пропустить случайный сигнал на выход блока опорных частот, используется серия элементов И (DD7:2, DD7:3, DD7:4, DD8:1), управляемых D‑триггером DD3:1. Если импульс X еще не подан – на выходе D‑триггера сохраняется 0, и, следовательно, на выходах элементов И тоже будет 0 независимо от состояния другого входа этих элементов. Как только подается импульс единицы, через определенную задержку на вход И подается 1 и тогда на выходе будут значения сигналов, которые уже успели установиться в определенные состояния. Вместе с номером очередного такта (CN0, CN1, CN2, CN3) на выход (CLK) блока опорных частот выходит тактирующий сигнал для основных элементов последовательного сумматора.

3.2 Блок выбора числа

Блок выбора строится на селекторах-мультиплексорах DD3, DD4, DD5, DD6 (DD8, DD9, DD10, DD11), которые содержат два управляющих сигнала: A, OE. В случае если OE=1, то на выходах мультиплексора всегда ноль, если OE=0, то сигналы на выходах зависит от состояния A. Если A=0, то на выходы мультиплексора подаются сигналы DI00, DI10, DI20, DI30, если A=1, то – DI01, DI11, DI21, DI31.

Выход OE выведен на землю, сигнал A соединен с прямым выходом триггера DD2:2 (DD7:1). В случае подачи логического нуля на вход NX, триггер устанавливается в 0, и на выходы подаются сигналы DI00, DI10, DI20, DI30, если подан импульс PR, триггер устанавливается в 1 и на выход подаются значения входов DI01, DI11, DI21, DI31.

3.3 Блок ввода числа

Основной целью блока ввода является перевод числа подающегося параллельно в прямом коде в последовательную форму обратного кода. Поскольку регистры DD22, DD23 (DD29, DD30) восьмиразрядные, а каждое число-операнд шестнадцатиразрядное, то для правильности извлечения числа из регистров, используется следующий метод: сигналы с обоих регистров подаются на один элемент ИЛИ и организовывается управление регистрами так, чтобы первые 8 тактов подавался сигнал с выхода младшего регистра, а сигнал с выхода старшего регистра оставался нулевым, вторые 8 тактов подавался сигнал с выхода старшего регистра, а сигнал с выхода младшего был бы ноль.

Регистр имеет пять управляющих сигналов DR, L, R, C1, C2. В случае если сигнал DR равен 0, то после сдвига регистр заполняется нулями и после 8‑ми тактов на выходе всегда будет 0, поэтому DR устанавливается на обоих регистрах в 0. Нулевое значение сигнала С1 необходимо для, того чтоб регистры могли реагировать на тактирующий сигнал, поэтому С1=0. Остается только три сигнала управляя, которыми можно осуществлять процесс загрузки числа.

– R – если сигнал 0, то на выходе всегда 0.

– C2 – тактирующий сигнал, при подаче которого происходит либо сдвиг, либо загрузка в зависимости от состояния L.

– L – если сигнал 0, то происходит загрузка числа, если 1 – сдвиг.

На выход регистра подается младший разряд, сдвиг происходит, тоже в сторону младшего разряда. Это позволяет осуществлять подачу числа от младших разрядов к старшим.

Т. к. сигнал вначале надо загрузить, а только потом начать сдвигать, для обоих регистров, действует принцип, что 1 на L подается после подачи первого тактирующего сигнала, и до подачи второго. С первым тактом происходит загрузка числа в регистр, со второго начинается его сдвиг.

С первыми восемью тактами будет подаваться сигнал только с младшего регистра, поскольку сигнал R старшего регистра установиться в 1 только после 8‑го такта. Со вторыми восемью тактами будет подаваться только сигнал со старшего регистра, поскольку младший регистр за счет нулевого DR успеет к этому моменту полностью обнулиться.

Во время перевода из параллельной формы в последовательную, необходимо также перевести число из прямого кода в обратный. Для этого нужно инвертировать все разряды кроме двух старших – знаковых. Но, поскольку, операцию инвертирования отдельных разрядов сделать достаточно сложно, инвертируются все разряды, а на два входа регистра, предназначенных для знаковых разрядов числа, всегда подаются нули. В случае если знаковые разряды равны 0, то на регистр подаются тоже нули, на выходе получается ноль, знаковые разряды не изменились. В случае если знаковые разряды равны 1, то в регистр подаются нули, которые потом инвертируются в 1, знаковые разряды снова не изменились.

При возникновении переноса во втором цикле суммирования на регистры будет подана сумма. Очевидно, что даже, если сумма будет отрицательной инвертировать ее не надо, поскольку она и так уже находится в обратном коде. Для этого введен вход INV разрешающий или запрещающий инвертирование.

3.4 Блок вывода числаОсновная задача блока вывода преобразование числа из последовательной формы в параллельную. Регистры DD34, DD35 блока вывода содержат два информационных сигнала: D1, D2, и два управляющих: R, C. В случае если R=0, то на выходе всегда 0, поэтому на входы R обоих регистров подается логическая единица. В случае подачи тактового сигнала на вход C, значения на выходах регистра сдвигаются в сторону младшего разряда, а в старший разряд добавляется значение информационных сигналов. Тактовые сигналы подаются на регистры через элементы И DD28:3, DD28:4. В случае если на второй вход И подается 1, то тактовый сигнал пропускается если 0, то тактовый сигнал равен 0. Второй вход элемента И для каждого регистра соединен с соответствующим JK‑триггером DD33:1, DD33:2. В начальном состоянии на выходе триггера младшего разряда 1, старшего – 0. Поэтому до 8‑го такта информационный сигнал загружается только на младший регистр. После восьмого такта состояния обоих триггеров меняется на противоположные, и информационный сигнал загружается только на старший регистр.

Похожие работы

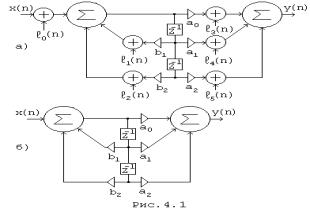

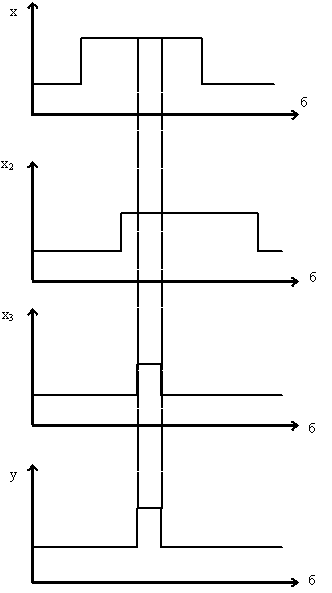

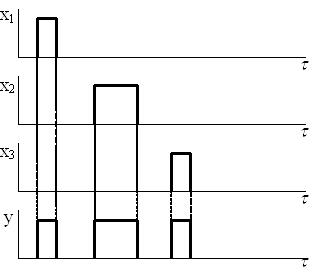

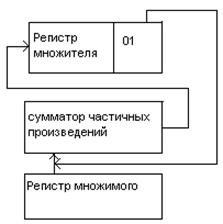

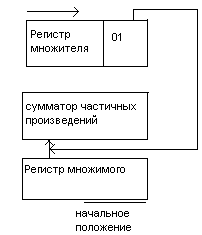

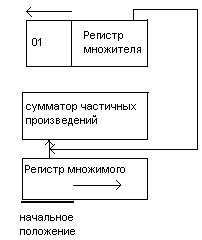

... которая помимо полного сумматора включает два регистра сдвига (А и В) и регистр суммы. Регистры сдвига А и В связаны со входами А и В полного сумматора. Рис. 15.17. Принцип работы суммирующего устройства последовательного действия Процесс последовательного суммирования состоит из нескольких шагов, которые отображены на рис. 15.17. На первом шаге регистры А и В загружаются двоичными числами ...

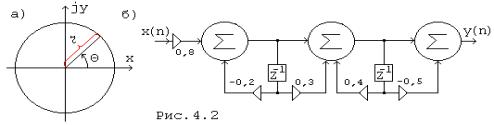

... - разряд необходим для округления. Окончательный результат: А(2) = 0,01010010 - после округления; А(2) = 0,01010001 - после усечения. Оценим погрешность полученных чисел конечной разрядности. При округлении А(10) 0*2-1 + 0*2-3 + 1*2-4 + 0*2-5 + 0*2-6 + 1*2-7 + 0*2-8 = 0,3203125 Отсюда, относительная погрешность представления исходного числа кодовым словом конечной разрядности равной 8 составляет ...

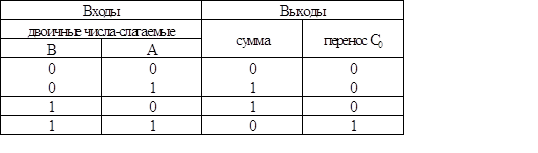

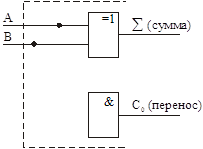

... чертеж или схема выполняются в САПР AutoCAD, поэтому наиболее часто используемой вспомогательной программой является конвертор из формата P-CAD в AutoCAD. 1. Основы математического аппарата анализа и синтеза комбинационных логических устройств Все устройства, оперирующие с двоичной информацией, подразделяются на два класса: - комбинационные (дискретные автоматы без памяти). - ...

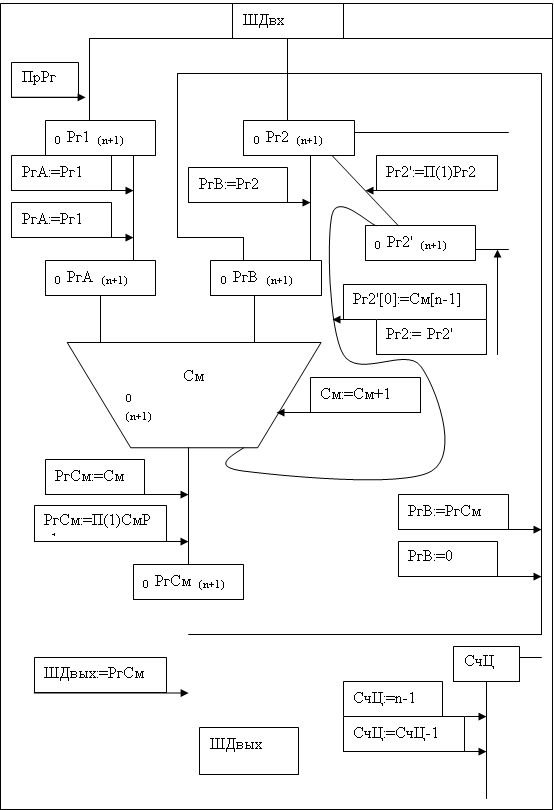

... этого логическая схема Пр формируется признаками результатов выполнения операции n1 n2 0 0 0 1 z=0 1 0 z<0 1 1 z>0 Указанные условия проверяются соответствующими логическими схемами, которые обеспечивают формирование сигналов n1 и n2 поступающих на устройство управления. Операция умножения – последовательность операций сложения и ...

0 комментариев