Навигация

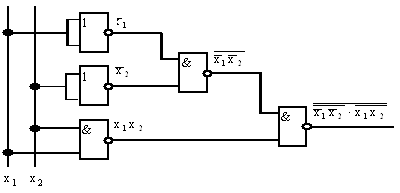

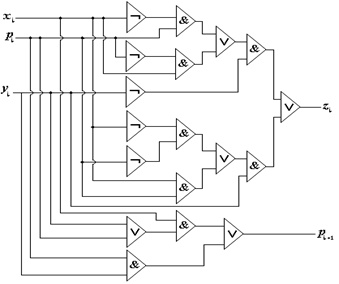

Функциональная схема для функции, представленной в СКНФ, в базисе И, ИЛИ, НЕ (рис.3.3)

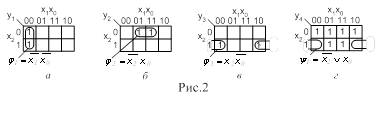

6. Функциональная схема для функции, представленной в СКНФ, в базисе И, ИЛИ, НЕ (рис.3.3).

|

|

Рис. 3.3 Функциональная схема устройства в базисе И, ИЛИ, НЕ

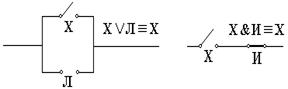

7. Для использования базиса И-НЕ, ИЛИ-НЕ преобразовывают далее полученные логические функции. Применяют закон двойной инверсии:

![]()

![]()

В соответствии с законами Де Моргана (инверсии; принципа дуальности, двойственности):

![]() ;

;

![]() .

.

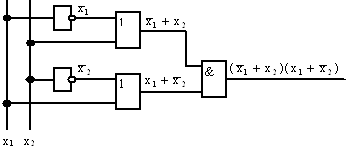

8. Функциональная схема для реализации функции f1 (рис.3.4).

Рис.3.4 Функциональная схема для реализации функции f1

9. Функциональная схема для реализации функции f2 (рис.3.5).

Рис.3.5 Функциональная схема для реализации функции f2

Пример 3.2. Синтезировать в базисе И, ИЛИ, НЕ и в базисе И-НЕ, ИЛИ-НЕ устройство, сигнал на выходе которого равен 1, только в том случае, когда на его двух входах (х1, х2) действуют одинаковые сигналы (узел равнозначности).

Решение. 1. Таблица истинности в соответствии со словесным описанием работы устройства:

| х1 | х2 | f |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

2. Определяют минтермы mi и макстермы Mi:

| х1 | х2 | mi | Mi | f |

| 0 | 0 |

|

| 1 |

| 0 | 1 |

|

| 0 |

| 1 | 0 |

|

| 0 |

| 1 | 1 |

|

| 1 |

3. СДНФ функции:

![]() .

.

Применив закон Де Моргана, получают:

![]() .

.

4. СКНФ функции:

![]() .

.

В соответствии с законом Де Моргана:

![]() .

.

5. Функциональная схема для f1 (рис.3.6).

Рис.3.6 Функциональная схема для f1

6. Функциональная схема для ![]() (рис.3.7).

(рис.3.7).

Рис. 3.7 Функциональная схема для ![]()

7. Функциональная схема для f2 (рис.3.8).

Рис. 3.8 Функциональная схема для f2

8. Функциональная схема для ![]() (рис.3.9).

(рис.3.9).

Рис.3.9 Функциональная схема для ![]()

Все четыре функциональные схемы логически равноценны.

Пример 3.3. Устройство с четырьмя входами должно работать так, чтобы на выходе появился сигнал 1, когда не менее чем на трех входах будут одновременно сигналы 1. Синтезировать устройство на элементах И, ИЛИ, НЕ.

Решение. 1. Таблица истинности в соответствии со словесным описанием работы устройства:

Таблица 3.1

Таблица истинности

| Номер набора | х1 | х2 | х3 | х4 | f |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 2 | 0 | 0 | 1 | 0 | 0 |

| 3 | 0 | 0 | 1 | 1 | 0 |

| 4 | 0 | 1 | 0 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 0 |

| 6 | 0 | 1 | 1 | 0 | 0 |

| 7 | 0 | 1 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 0 |

| 10 | 1 | 0 | 1 | 0 | 0 |

| 11 | 1 | 0 | 1 | 1 | 1 |

| 12 | 1 | 1 | 0 | 0 | 0 |

| 13 | 1 | 1 | 0 | 1 | 1 |

| 14 | 1 | 1 | 1 | 0 | 1 |

| 15 | 1 | 1 | 1 | 1 | 1 |

2. Запишем СДНФ функции на основе ее единичных наборов:

![]() .

.

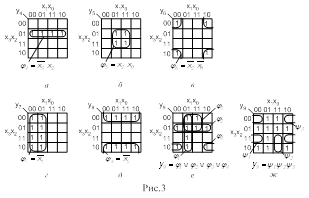

3.Для минимизации функции применим карту Карно (рис.3.10).

| х1х2 х3х4 | 00 | 01 | 11 | 10 |

| 00 | 0 | 0 | 0 | 0 |

| 01 | 0 | 0 |

| 0 |

| 11 | 0 |

| 1 | 1 |

| 10 | 0 | 0 | 1 | 0 |

Рис. 3.10 Карта Карно

4. МНДФ функции:

![]() .

.

5. Функциональная схема устройства (рис.3.11).

Рис.3.11 Функциональная схема устройства

Пример 3.4. Синтезировать мажоритарный элемент на три входа в базисе ИЛИ-НЕ. У такого элемента значение выходного сигнала совпадает с значением большинства входных.

Решение. 1. Таблица истинности в соответствии со словесным описанием работы элемента:

| x1 | x2 | х3 | у |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

2. СДНФ функции на основе ее единичных наборов:

![]() .

.

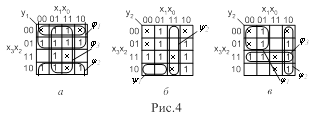

3. Для минимизации функции применим карту Карно (рис.3.12).

| х1х2 х3 | 00 | 01 | 11 | 10 |

|

|

| 0 |

|

|

| 1 | 0 |

| 1 | 1 |

Рис.3.12 Карта Карно

4. МДНФ функции:

![]() .

.

5. МКНФ функции:

![]() .

.

6. Для реализации функции в базисе И-НЕ и в базисе ИЛИ-НЕ преобразуем функцию в соответствии с законом Де Моргана:

![]() ;

; ![]() .

.

7. Функциональная схема для функции f1 в базисе И-НЕ (рис.3.13).

Рис.3.13 Функциональная схема для функции f1 в базисе И-НЕ

8. Функциональная схема для функции f2 в базисе ИЛИ-НЕ (рис.3.14).

Рис.3.14 Функциональная схема для функции f2 в базисе ИЛИ-НЕ

4. Особенности синтеза схем с запрещенными комбинациями

Иногда применяют устройства, закон функционирования которых определен неполностью. В таких устройствах некоторые комбинации сигналов на входы никогда не подаются (запрещены).

Работа устройств с запрещенными комбинациями входных сигналов описывается неполностью определенными логическими функциями, значения которых определены не на всех наборах аргументов.

Нормальная работа устройства с неполностью определенным законом функционирования не нарушится, если произвольно задать значения функции для запрещенных комбинаций аргументов.

Обычно логической функции на запрещенных наборах придают такие значения, при которых она приобретает наиболее простой вид.

При минимизации логической функции безразличные наборы входных переменных в соответствующих клетках карты Карно обозначают знаком Х. В объединения включают те клетки, отмеченные Х, которые дают расширение объединений и уменьшение их количества.

5. Типовые комбинационные схемы

Серии микросхем, выпускаемые промышленностью, содержат широкую номенклатуру элементов, выполняющих не только простейшие логические функции (И, ИЛИ, НЕ, ИЛИ-НЕ, И-НЕ), но и более сложные операции, например, выполняемые мультиплексорами и демультиплексорами, шифраторами и дешифраторами, преобразователями кодов, сумматорами и т.д.

Поэтому не может быть речи о синтезе комбинационных схем только в базисах И, ИЛИ, НЕ, или ИЛИ-НЕ, а также И-НЕ, а следует наиболее полно использовать функциональные возможности всех логических элементов.

Для успешного синтеза цифровых узлов следует знать функционирование типовых комбинационных схем, выпускаемых промышленностью в виде интегральных микросхем, и которые синтезированы, как правило, в логических базисах И, ИЛИ, НЕ, или ИЛИ-НЕ, а также И-НЕ.

5.1 Мультиплексоры

Мультиплексор (коммутатор) - комбинационное многовходовое устройство с одним выходом.

Входы подразделяются на:

1) информационные х1, х2, х3,..., хn;

2) управляющие (адресные) v1, v2, v3,..., vm;

где n - число информационных входов,

m - число управляющих (адресных) входов.

Обычно n=2m.

Код (адрес), поступающий на управляющие входы, определяет один из информационных входов, значение переменной которого передается на выход у.

Адреса представляют в двоичном коде и им присваивают номер j. Каждому адресу с номером j соответствует свой информационный вход xj, сигнал с которого при данном адресе проходит на выход.

Основным назначением мультиплексора является коммутация n=2m входных сигналов на один выход.

В соответствии с назначением составим таблицу истинности для мультиплексора, содержащего, например, четыре информационных входа: х1, х2, х3, х4, которые могут коммутироваться двумя управляющими (адресными) входами (табл.5.1).

Таблица 5.1Таблица истинности мультиплексора

| Адресные переменные | Информационные Переменные | Выход у | ||||

| v1 | v2 | x1 | x2 | x3 | X4 | y |

| 0 | 0 | 1 | 1 | |||

| 0 | 1 | 1 | 1 | |||

| 1 | 0 | 1 | 1 | |||

| 1 | 1 | 1 | 1 | |||

| 0 | 0 | 0 | 0 | |||

| 0 | 1 | 0 | 0 | |||

| 1 | 0 | 0 | 0 | |||

| 1 | 1 | 0 | 0 | |||

Незаполненные клетки соответствуют значениям информационных переменных, не влияющих на значение выходного сигнала у. Так как каждому адресу соответствует свой информационный вход, то таблицу истинности можно представить в виде (табл.5.2).

Таблица 5.2

Преобразованная таблица истинности мультиплексора

| Адресные переменные | Информационные переменные | Выход у | ||||

| v1 | v2 | x1 | x2 | x3 | x4 | y |

| 0 | 0 | х1 | х1 | |||

| 0 | 1 | х2 | х2 | |||

| 1 | 0 | х3 | х3 | |||

| 1 | 1 | х4 | х4 | |||

Работа мультиплексора описывается при этом логической функцией:

![]() ,

,

а его функциональная схема дана на (рис.5.1).

Рис. 5.1. Функциональная схема мультиплексора.

Функция, реализуемая мультиплексором, в общем виде может быть представлена в виде СДНФ:

![]() .

.

Кроме основного назначения (коммутация сигналов) мультиплексоры используют для построения постоянных запоминающих устройств (ПЗУ) объемом 2m+1 бит и для синтеза комбинационных логических схем. При этом можно синтезировать ![]() различных логических функций от (m+1) логических переменных. Например, на мультиплексоре с n=4 и m=2 входами реализуется любая логическая функция от трех переменных, т.к. для трех переменных существует

различных логических функций от (m+1) логических переменных. Например, на мультиплексоре с n=4 и m=2 входами реализуется любая логическая функция от трех переменных, т.к. для трех переменных существует ![]() различных функций.

различных функций.

При построении ПЗУ на информационные входы мультиплексора подают не изменяющиеся во времени сигналы 0 и 1. Считывание данных сигналов производится подачей соответствующих сигналов на адресные (управляющие) входы.

В этом случае мультиплексор реализует некоторую наперед заданную функцию, представленную в совершенной дизъюктивной нормальной форме (СДНФ), как следует из представленной выше логической функции мультиплексора.

Основной задачей при синтезе комбинационных логических схем на мультиплексорах является оптимальный выбор переменных, подаваемых на его управляющие (адресные) входы.

Критерием оптимальности выбора адресных переменных может служить количество сигналов 0 и 1, подаваемых при этом на информационные входы.

Правило выбора адресных переменных рассмотрим для двух случаев.

Пусть логическая функция задана табл.5.3

Таблица 5.3

Таблица истинности

| х1 | х2 | х3 | f |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Выделим из логических переменных переменную х3. Одинаковые комбинации оставшихся переменных х1 х2 представим в виде групп (отделены в таблице истинности двойными горизонтальными линиями).

Выберем в качестве адресных (управляющих) переменных переменные х1 и х2. При коде v1v2=x1x2=00 на выход мультиплексора коммутируется вход Х1. Если на вход Х1 подать переменную х3, то на выходе получим значение логической функции при х1х2=00. Это удобно отразить в табл.5.4

Таблица 5.4Таблица истинности

Адресные переменные | Информационные переменные | Выход | ||||

| v1 x1 | v2 x2 | X1 | X2 | X3 | X4 | f |

| 0 | 0 | x3 | x3 | |||

| 0 | 1 |

|

| |||

| 1 | 0 | 0 | 0 | |||

| 1 | 1 | 1 | 1 | |||

При коде v1v2=x1x2=01 на выход коммутируется вход Х2. В соответствии с таблицей истинности логической функции, на этот вход следует подать ![]() .

.

При коде v1v2=x1x2=10 на выход коммутируется вход x3. В соответствии с таблицей истинности логической функции, на этот вход следует подать "0".

При коде v1v2=x1x2=11 на выход коммутируется вход x4. В соответствии с таблицей истинности логической функции, на этот вход следует подать "1" (рис. 5.2).

|

|

Рис. 5.2 Пример синтеза комбинационной схемы на мультиплексоре.

На мультиплексорах можно реализовывать совместно две функции. При этом отыскивают те переменные, которые суммарно входят в МДНФ функций наибольшее число раз. Например, заданы МДНФ двух функций:

![]()

![]() .

.

Таблица истинности для них выглядит следующим образом:

| x1 | x2 | x3 | x4 | f1 | f2 |

| 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 |

Если в качестве таких переменных выбрать х3 и х2, то получим следующие таблицы истинности для заданных функций.

Для f1:

| v1 x3 | v2 x2 | X1 | X2 | X3 | X4 | f1 |

| 0 | 0 |

|

| |||

| 0 | 1 |

|

| |||

| 1 | 0 |

|

| |||

| 1 | 1 |

|

|

Для f2:

| v1 x3 | v2 x2 | Y1 | Y2 | Y3 | Y4 | f2 |

| 0 | 0 |

|

| |||

| 0 | 1 | 0 | 0 | |||

| 1 | 0 |

|

| |||

| 1 | 1 |

|

|

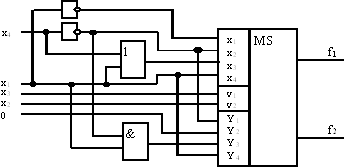

Функциональная схема устройства на сдвоенном четырехканальном мультиплексоре имеет вид рис.5.3.

Рис. 5.3 Применение мультиплексора для реализации совместно двух логических функций.

Пример 5.1. Синтезировать мультиплексор с восемью информационными входами и одним выходом на элементах И, ИЛИ, НЕ.

Решение. 1. Восемь информационных входов могут коммутироваться на один выход с помощью трех адресных входов (n=2m, для n=8, m=3) 2. Таблица истинности для логической функции мультиплексора (табл. 5.5).

Таблица 5.5

Таблица истинности

| Адрес | Выход y | ||

| v1 | v2 | v3 | |

| 0 | 0 | 0 | x1 |

| 0 | 0 | 1 | x2 |

| 0 | 1 | 0 | x3 |

| 0 | 1 | 1 | x4 |

| 1 | 0 | 0 | x5 |

| 1 | 0 | 1 | x6 |

| 1 | 1 | 0 | x7 |

| 1 | 1 | 1 | x8 |

3. Логическая функция в соответствии с таблицей истинности:

![]()

4. Функциональная схема мультиплексора рис.5.4.

Рис 5.4 Функциональная схема мультиплексора с восемью информационными входами.

5.3 Демультиплексоры

Демультиплексор - комбинационное устройство с одним информационным входом х1, с m управляющими входами (v1...vm) и с n информационными выходами (y1...yn), при этом n=2m.

Основное назначение демультиплексора - распределение сигнала с линии по нескольким каналам (обратное мультиплексору).

Таблица истинности для n=8 и m=3 (табл.5.6)

Таблица 5.6Таблица истинности для n=8 и m=3

| v3 | v2 | v1 | y1 | y2 | y3 | y4 | y5 | y6 | y7 | y8 |

| 0 | 0 | 0 | x | |||||||

| 0 | 0 | 1 | x | |||||||

| 0 | 1 | 0 | x | |||||||

| 0 | 1 | 1 | x | |||||||

| 1 | 0 | 0 | x | |||||||

| 1 | 0 | 1 | x | |||||||

| 1 | 1 | 0 | x | |||||||

| 1 | 1 | 1 | x |

где х принимает значение 0 или 1.

Работа демультиплексора описывается уравнениями:

![]()

![]()

Функциональная схема демультиплексора, построенного по этим уравнениям для n=4, m=2 (рис.5.5).

|

|

Рис 5.5 Функциональная схема демультиплексора с четырьмя выходами.

5.4 Дешифраторы

Полным дешифратором называют комбинационную схему, имеющую n входов и 2n выходов и реализующую на каждом выходе функцию, представляющую собой минтерм n переменных.

Дешифраторы являются преобразователями кодов, выполняющих преобразование двоичного и двоично-десятичного кодов в унитарный код. Унитарный код двоичного n-разрядного числа представляется 2n разрядами, только один из разрядов которого равен 1 [6].

Поэтому в полном дешифраторе каждой комбинации значений входных сигналов х1,..., хnсоответствует сигнал, равный 1, только на одном выходе, на остальных выходах сохраняются сигналы 0. На выходах вырабатываются 1 при минтермах соответственно:

![]()

![]()

Такой системе уравнений, например, для n=2 соответствует табл.5.7.

Таблица 5.7. Таблица истинности| х2 | х1 | f0 | f1 | f2 | f3 |

| 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

Пример 5.2. Синтезировать преобразователь кода прямого замещения в двоично-десятичный код 2421.

Решение 1. Код прямого замещения представляет собой обычное представление одноразрядного десятичного числа в двоичной системе счисления, т.е.

![]()

Похожие работы

... D=1- W3W4(W1W5W6+ W7+ W1W8+ W2W6 W7+ W2W7+2W2W8+ 1)+ W5W6(W3W4(W7+ W1W5W6+ W2W7+ W2W8+1)-1) Для x1 Для x4 Для y Для х13 Задание 2. Синтез комбинационных схем. 2.1 Определение поставленной задачи Устройство, работа которого может быть представлена на языке алгебры высказываний, принято называть логическим. Пусть такое устройство имеет n ...

... порядка рис.7,б, которая хуже схемы рис.7,а по характеристикам быстродействия и сложности. Ухудшение характеристик оправдывается только возможностью реализации схемы на заданных стандартных элементах. 8. Комбинационные схемы Логическая схема (рис.8) с n входами и k выходами реализует систему переключательных функций y0 ...yk-1. Каждая функция yi(x0 ...xk-1) однозначно соответствует ...

... одно состояние из множества А, каждой строке – один входной сигнал из множества Z. На пересечении строки и столбца в таблице переходов, записывается состояние as, в которое должен перейти автомат из состояния am, под действием входного сигнала zf, т.е. as = σ(am, zf). На пересечении строки и столбца в таблице выходов записывается выходной сигнал wg, выдаваемый автоматом в состоянии am при ...

... к утверждению выводимости формулы Применение логики высказываний к анализу математических доказательств Ни у кого не возникает сомнения в том, что математические доказательства являются примерами строгих логических рассуждений. Аппарат логики высказываний позволяет нам прояснить структуру доказательств многих математических утверждений. Рассмотрим с точки зрения логики высказываний ...

0 комментариев