Навигация

Вкажіть типи буферних схем, використаних в УУМС-2. Їх призначення та особливості роботи

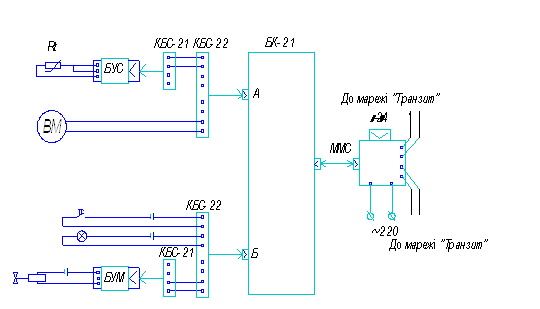

11. Вкажіть типи буферних схем, використаних в УУМС-2. Їх призначення та особливості роботи.

12. Дайте визначення адресного простору мікропроцесорної системи та розпишіть його розподіл в УУМС-2.

Адресний простір УУМС складається з областей, состав яких показаний у табл.2. Варто звернути увагу, що внутрішні адресні області основного й периферійного мікроконтролерів мають типову схему адресації відповідно до архітектури кожного з них. Так, внутрішня пам'ять програм основного мікроконтролера AT89S8252 займає діапазон адрес 0000 - 1FFFh (8Кбайт). У цій області розташована системна керуюча програма MONITOR. Внутрішня пам'ять програм периферійного мікроконтролера ATmega16 є самостійним адресним простором і займає діапазон адрес 0000 - 3FFFh (16 Кбайт). Докладніше про структуру внутрішніх адресних областей мікроконтролерів можна прочитати в.

Всі пристрої системи, зовнішні стосовно основного мікроконтролера, взаємодіють із ним через шину даних. При цьому сигнали вибірки кристала для кожного пристрою генеруються відповідно до апаратної адреси цього пристрою, представленим у табл.4.

Таблиця 4 - Структура адресного простору УУМС-2

| Діапазон адрес | Пристрій | Фізична реалізація або буфер | Сигнали вибору кристала |

| 2000h – 3FFFh | Пам'ять програм користувача ( 8 Кбайт ) – тільки читання. | ОЗУ КР537РУ17 (DD9) | CS1 |

| 4000h – 7FFFh | Пам'ять даних користувача ( 16 Кбайт ) | ОЗУ КР537РУ17 (DD11, DD12) | CS2, CS3 |

| FFF0h | 10-позиційний жидкокристаллический дисплей | Регістр DD17 | CS_LCD |

| FFF1h | Лінійка светодиодов | Регістр DD16 | CS_LED |

| FFF2h | Лінійка перемикачів (ручне уведення дискретних сигналів) | Регістр DD18 | CS_BTN |

| FFF3h | Дискретні входи, дискретні виходи | Два 4-бітових регістри в DD19 | CS_DIDO |

| FFF4h | Периферійний мікроконтролер ATmega16 (убудовані АЦП, ШИМ, таймери й ін.) | Регістр прийому й регістр передачі із загальною адресою; DD26 й DD25 | CS_AVR |

| FFF5h, FFF6h | Цифро-аналоговий перетворювач (ЦАП) | Регістри DD30, DD31 | CS_DAC_LOW CS_DAC_HI |

| FFF7h – FFFAh | Блок семисегментных індикаторів (4 ССИ) | Регістри DD34, DD36–DD38 | CS_SSI 0, CS_SSI1, CS_SSI2, CS_SSI3 |

| FFFBh | Вільна адреса | – | – |

| FFFCh – FFFFh | Паралельний програмувальний інтерфейс – ППИ (три 8-розрядних порти вводу-виводу з рівнями ТТЛ і регістр керування) | КР580ВВ55 (DD24) | CS_PPIA, CS_PPIB, CS_PPIC, CS_PPIU; об'єднані в загальний сигнал CS_PPI елементом DD29-1 |

13. Вкажіть функції адресного селектора та особливості його розподілу в лабораторному стенді.

Адресний селектор (дешифратор адреси) у складі УУМС призначений для формування сигналів дозволу роботи пам'яті й всіх периферійних блоків системи. Ці сигнали формуються на основі інформації, видаваної мікроконтролером на шину адреси. Адресний селектор складається із двох частин:

- адресний селектор зовнішньої пам'яті;

- адресний селектор периферійних пристроїв системи.

Адресний селектор пам'яті реалізований на одному з дешифраторів у складі мікросхеми КР1533ИД14 (DD10-1). На підставі адресних сигналів А13-А15 він формує сигнали вибору кристала CS1 для пам'яті програм або сигнали CS2, CS3 для мікросхем пам'яті даних.

Адресний селектор периферійних пристроїв є двухкаскадным. Перший каскад реалізований на іншому дешифраторі з мікросхеми КР1533ИД14 (DD10-2). На підставі адресних сигналів А14, А15, що надходять на дешифратор, і сигналів А12 й А13 (об'єднаних по И-НІ на елементі DD8-1), що дозволяють його роботу, він формує сигнал керування для другого каскаду адресного селектора. Активний рівень "0" цього сигналу буде отриманий тільки при комбінації А12 = А13 = А14 = А15 = 1. Додатковий сигнал керування для другого каскаду формується 8-входовым елементом И-НІ мікросхеми DD7 на основі адресних сигналів А4-А11, причому активний рівень "0" також виходить тільки при рівності "1" всіх сигналів А4-А11 одночасно (адреса FFF_h).

Другий каскад адресного селектора периферійних пристроїв побудований на дешифраторі КР1533ИД3 (DD6) з організацією 4?16. На підставі сигналів керування (коли обоє рівні "0") і адресних сигналів А0-А3 цей дешифратор формує сигнали дозволу роботи (вибору кристала) периферійних пристроїв.

14. Які типи символів можуть виводитись на індикацію, використаного в лабораторному стенді знакосинтезуючого індикатора. Як здійснюється управління цим процесом.

15. Вкажіть призначення та особливості реалізації блоку уводу-виводу дискоетних сигналів з гальванічною розв'язкою.

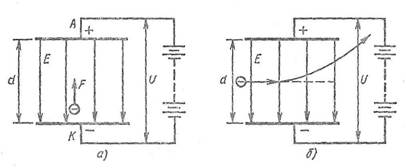

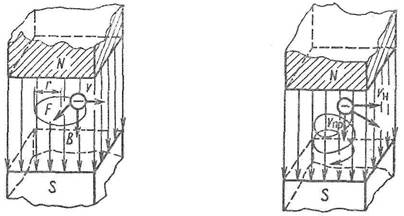

Дискретні сигнали з гальванічною розв'язкою можуть передаватися на вилучене встаткування або на пристрої, рівні сигналів у які відрізняються від рівнів ТТЛ.

У системі УУМС-2 реалізовані схеми прийому чотирьох вхідних дискретних сигналів з гальванічною розв'язкою на оптоэлектронных ключах ДО293ЛП1А (DA1-DA4). Кожна лінія прийому дискретного сигналу з боку схемного рознімання J7 DINPUTS є двухпроводной (анодна (DIn_+) і катодна (DIn_-) ланцюга светоизлучателя в оптоэлектронном ключі). Струм спрацьовування оптоэлектронного ключа становить 15 м, а граничний струм - 40 ма. Таким чином, можна формувати вхідний сигнал, комутируючи на вхід оптоэлектронного ключа лінію живлення +5У через резистор опором близько 300 Ом.

Важливо помітити, що застосовані оптоэлектронные ключі є інверторами сигналу, тобто при наявності струму 15-20ма через вхідний светодиод на виході ключа присутній сигнал балка. "0", а при відсутності струму - сигнал балка. "1".

На стороні схеми оптоэлектронными ключами формуються сигнали ТТЛ DINPUT0–DINPUT3. Ці сигнали надходять на шину даних через один з 4-бітових регістрів мікросхеми КР1533ИР34 (DD19-2).

Інформація може бути прочитана з регістра DD19-2 по сигналі (CS_DIDO + RD), що подається на вхід дозволу видачі #OE регістра DD19-2 і відкриває його вихідні буферы. На вхід Із синхронізації запису в регістр поданий рівень "1", що забезпечує постійну фіксацію в регістрі поточних сигналів з оптоэлектронных ключів DA1-DA4.

Схеми видачі чотирьох вихідних дискретних сигналів DOut1-DOut4 забезпечують стандарт "струмова петля", тобто логічному рівню "0" відповідає струм 0 ма, а логічному рівню "1" - струм 20 ма. Такі значення струмів забезпечуються резисторами R40-R43, включеними в колекторні ланцюги транзисторів VT1-VT4. на приймаючій стороні інтерфейсу "струмова петля" повинен бути включений оптоэлектронный ключ (светодиод), причому його анод підключається до ланцюга VCC джерела сигналу, а катодний ланцюг - до резистора колекторного ланцюга джерела сигналу. Таким чином, светодиод оптоэлектронного ключа схеми-приймача є частиною колекторного ланцюга вихідного транзистора схеми-джерела.

Вихідні транзистори VT1-VT4 підключені до шини дані системи через інший 4-бітовий регістр у мікросхемі КР1533ИР34 (DD19-1). Інформація записується в регістр DD16 по сигналі not(CS_DIDO + WR). Вихідні буферы регістра DD19-1 увесь час відкриті, що забезпечує підтримку рівнів сигналів, записаних у регістр, на ланцюзі бази транзисторів VT1-VT4.

Хоча групи вхідних і вихідних сигналів підключаються до шини даних через окремі 4-бітові регістри, однак обидва регістри мають той самий системну адресу FFF3h. Прийом і видача даних виробляються шляхом читання або запису байта за адресою FFF3h, причому при читанні й записі використаються ті самі молодші розряди D0-D3 шини даних.

16. З якою метою в де-яких блоках мікропроцесорної системи застосовується елементи гальванічної розв'язки.

17. Наведіть усі відомі вам типи елементів гальванічної розв'язки та поясніть їх принцип роботи. Покажіть на схемі УУМС-2 ці елементи та поясніть їх функції.

18. Які функції покладено на периферійний МК стенду УУМС-2.

Інтерфейс між периферійним мікроконтролером і системною шиною даних реалізований на основі двох зустрічно включених регістрів КР1533ИР22, що мають однакову системну адресу FFF4h.

Таким чином, передача даних від основного контролера на периферійний виконується шляхом запису байта в зовнішній регістр за адресою FFF4h. Периферійний контролер може прочитати байт із цього регістра, видавши низький рівень по лінії AVR_RD. Для передачі даних основному контролеру периферійний повинен видати бать даних на свій порт PC і сформувати високий рівень по лінії AVR_WR. При цьому дані фіксуються в регістрі, і можуть бути прочитані основним контролером за адресою FFF4h.

Для пересилання даних від основного контролера до периферійного використаний регістр DD25. Входи цього регістра підключені до шини даних D0–D7, а виходи – лініями AVR_D0 – AVR_D7 до порту PC (лінії PC0–PC7) периферійного мікроконтролера. Запис у регістр DD25 по шині даних тактируется сигналом not(CS_AVR + WR), що подається на вхід С. Читання із цього регістра в периферійний мікроконтролер виробляється по низькому рівні сигналу AVR_RD, що подається на вхід дозволу видачі #OE. Сигнал AVR_RD повинен програмно формуватися периферійним мікроконтролером на лінії PD0 порту PD.

Для пересилання даних від периферійного мікроконтролера до основного використаний регістр DD26. Входи цього регістра підключені лініями AVR_D0 – AVR_D7 до порту PC (лінії PC0–PC7) периферійного мікроконтролера, а виходи – до шини даних D0–D7. Запис у регістр DD26 від периферійного мікроконтролера тактируется високим рівнем сигналу AVR_WR, що подається на вхід С. Сигнал AVR_WR повинен програмно формуватися периферійним мікроконтролером на лінії PD1 порту PD. Читання з регістра DD26 по шині даних в основний мікроконтролер виробляється по сигналі not(CS_AVR + RD), що подається на вхід дозволу видачі #OE.

Для запиту даних і підтвердження читання основний і периферійний контролери можуть обмінюватися сигналами PRRQ (запит даних) і PRANS (підтвердження). Рекомендується використати активний низький рівень цих сигналів. Крім того, периферійний контролер може генерувати запит на переривання основного контролера (лінія #INT1_AVR), при цьому основний контролер одержує переривання по лінії #INT1 (низький рівень або зріз сигналу).

Таким чином, наявне апаратне з'єднання дозволяє реалізувати різні види протоколів обміну між основним і периферійним мікроконтролерами (синхронний, асинхронний по запиті, командний і т.п.).

Похожие работы

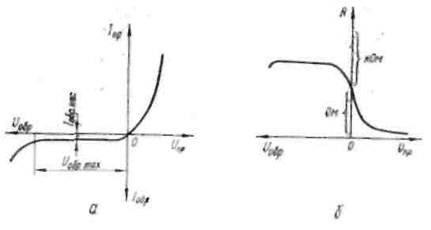

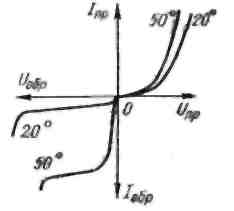

... 4. Як графічно позначаються польові транзистори? Інструкційна картка №9 для самостійного опрацювання навчального матеріалу з дисципліни «Основи електроніки та мікропроцесорної техніки» І. Тема: 2 Електронні прилади 2.4 Електровакуумні та іонні прилади Мета: Формування потреби безперервного, самостійного поповнення знань; розвиток творчих здібностей та активізації розумово ...

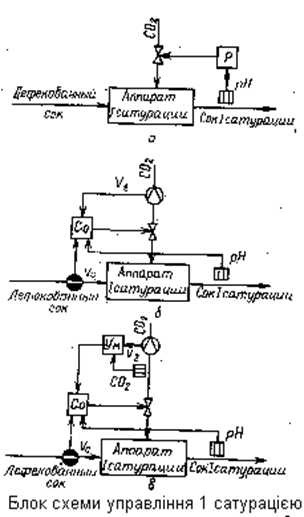

... ії контурів управління Автоматична система управління дозування формаліна передбачає контролювання таких параметрів як Fстр. кількості постачаємої стружки в дифузійний апарат, є головним чинником який впливає на час подачі формаліна в дифузійну установку, рН дифузійного соку та Т температура середовища протікання процесу, ці показники відображають розвиток мікрофлори в дифузійному апараті та є ...

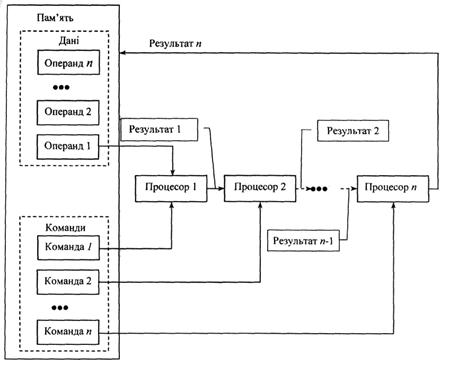

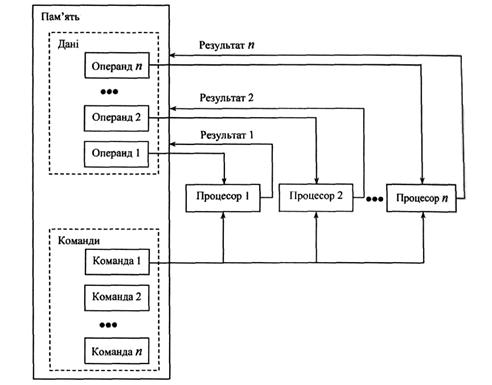

... для розв'язання особливо складних науково-технічних задач, оброблення великих обсягів даних у реальному масштабі часу, моделювання складних систем, автоматизованого проектування складних об'єктів, а також у системах керування (промислових і військових). Макет найпотужнішого суперкомп'ютера ES (Earth Simulator) Центра моделювання Землі (Earth Simulator Center) у Йокогамі (Японія) показаний рис. ...

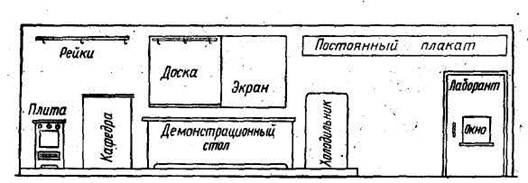

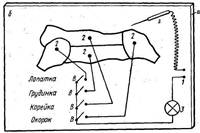

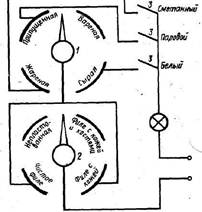

... дзеркала над демонстраційною плитою протягом багатьох років з успіхом використовуються в кулінарних училищах. 2.2 Експериментальна перевірка ефективності застосування технічних засобів навчання у навчально-виховному процесі при вивченні дисципліни «Кулінарія» Для перевірки результативності засвоєння знань студентами Чернігівського комерційного технікуму з використанням на заняттях технічних ...

0 комментариев