Навигация

3. Система команд

Система команд ОМЭВМ семейства MCS-51 имеет 111 команд и позволяет реализовать обработку данных, обеспечить выполнение логических, арифметических операций, а также управление в режиме реального времени. Реализованы побитовая, потетрадная (4 бита), побайтовая (8 бит) и 16-разрядная обработка данных.

Полное описание команд и примеры их выполнения приведены в приложении Б.

В машинном коде команда занимает один, два или три байта и выполняется за один, два или четыре (умножение и деление) машинных цикла. При частоте тактового генератора, равной 12 МГц, одноцикловые команды выполняются за 1 мкс, двухцикловые – за 2 мкс и т.д. Из 111 типов команд 64 выполняются за 1 мкс (12 тактов), 45 команд – за 2 мкс (24 такта) и две команды – умножение и деление (MUL, DIV) выполняются за 4 мкс (48 тактов).

Все команды условных переходов осуществляются относительно содержимого счетчика команд с адресом перехода, вычисляемым ЦПУ во время выполнения команды.

Трехбайтовые команды перехода и вызова LCALL, LJMP (с 16-разрядным адресом) позволяют осуществлять переход и обращение по любому адресу адресного пространства памяти программ емкостью 64 Кбайт. Если необходим переход в пределах области памяти программ 2 К, то можно использовать команды перехода и вызова с 11-разрядным адресом (ACALL, AJMP). Переход внутри участка памяти, определяемый 8-разрядной величиной смещения, осуществляется по команде SJMP. В табл. 2 приведены обозначения и символы, используемые в системе команд.

Систему команд ОМЭВМ условно можно разбить на пять групп: арифметические команды; логические команды с байтовыми переменными; команды передачи данных; команды битового процессора; команды ветвления программ и передачи управления.

Арифметические команды. В наборе команд ОМЭВМ имеются следующие арифметические операции: сложение, сложение с учетом флага переноса, вычитание с заёмом, инкрементирование, декрементирование, сравнение, десятичная коррекция, умножение и деление.

Таблица 2 – Обозначение символов в наборе команд

| Обозначение, символ | Назначение |

| 1 | 2 |

| А | Аккумулятор |

| Rr | Регистры текущего выбранного банка регистров |

| r | Номер загружаемого регистра, указанного в команде |

| direct | Прямо адресуемый 8-битовый внутренний адрес ячейки данных, который может быть ячейкой внутреннего ОЗУ данных (0-127) или SFR (128-255) |

| @Rr | Косвенно адресуемая 8-битовая ячейка внутреннего ОЗУ данных |

| data 8 | 8-битовое непосредственное данное, входящее в код операции (КОП) |

| Data 16 | 16-битовое непосредственное данное, входящее КОП |

| Data Н | Старшие биты (15-8) непосредственных 16-битовых данных |

| Data L | Младшие биты (7-0) непосредственных 16-битовых данных |

| Addr 11 | 11-битовый адрес назначения |

| Addr 16 | 16-битовый адрес назначения |

| Addr L | Младшие биты адреса назначения |

| disp 8 | 8-битовый байт смещения со знаком |

| bit | Бит с прямой адресацией, адрес которого содержит КОП, находящийся во внутреннем ОЗУ данных или SFR |

| al5,al4...a0 | Биты адреса назначения |

| (X) | Содержимое элемента Х |

| ((X)) (X) [M] | Содержимое по адресу, хранящемуся в элементе Х Разряд М элемента Х |

| (X)[MI-M2] | Группа разрядов М1-М2 элемента Х |

| + - * / AND OR XOR /X | Операции: сложения вычитания умножения деления логического умножения (операция И) логического сложения (операция ИЛИ) сложения по модулю 2 (операция "Исключающее ИЛИ") инверсия элемента Х |

В АЛУ производятся действия над целыми числами без знака. В двухоперандных операциях: сложение (ADD), сложение с переносом (ADDC) и вычитание с заёмом (SUBB) аккумулятор является первым операндом и принимает результат операции. Вторым операндом может быть рабочий регистр выбранного банка рабочих регистров, регистр внутренней памяти данных с косвенно-регистровой и прямой адресацией или байт непосредственных данных. Указанные операции влияют на флаги: переполнения, переноса, промежуточного переноса и флаг четности в слове состояния процессора (PSW).

Использование разряда переноса позволяет многократно повысить точность при операциях сложения (ADDC) и вычитания (SUBB).

Выполнение операций сложения и вычитания с учетом знака может быть осуществлено с помощью программного управления флагом переполнения (OV) регистра PSW. Флаг промежуточного переноса (АС) обеспечивает выполнение арифметических операций в двоично-десятичном коде.

Операции инкрементирования и декрементирования на флаги не влияют.

Операции сравнения не влияют ни на операнд назначения, ни на операнд источника, но они влияют на флаг переноса.

Существуют три арифметические операции, которые выполняются только на аккумуляторе: две команды проверки содержимого аккумулятора A (JZ, JNZ), и команда десятичной коррекции при сложении двоично-десятичных кодов.

При операции умножения содержимое аккумулятора А умножается на содержимое регистра В и результат размещается следующим образом: младший байт в регистре A, старший – в регистре B.

В случае выполнения операции деления целое от деления помещается в аккумулятор А, остаток от деления – в регистр В.

Логические команды с байтовыми переменными. Система команд ОМЭВМ позволяет реализовать логические операции: "И", "ИЛИ", "ИСКЛЮЧАЮЩЕЕ ИЛИ" на регистре-аккумуляторе (А) и байте-источнике. Вторым операндом (байтом-источником) при этом может быть рабочий регистр в выбранном банке рабочих регистров; регистр внутреннего ОЗУ, адресуемый с помощью косвенно-регистровой адресации; прямо адресуемые ячейки внутреннего ОЗУ и регистры специальных функций; непосредственная величина.

Указанные логические операции могут быть реализованы на любом прямо адресуемом регистре внутреннего ОЗУ или регистре специальных функций с использованием в качестве второго операнда содержимого аккумулятора А или непосредственных данных.

Существуют логические операции, которые выполняются только на аккумуляторе: сброс и инвертирование всех восьми разрядов А; циклический сдвиг влево и вправо; циклический сдвиг влево и вправо с учетом флага переноса; обмен местами старшей и младшей тетрад внутри аккумулятора.

Команды передачи данных. Таблицы символов (кодов), зашитые в ПЗУ программы, могут быть выбраны с помощью команд передачи данных с использованием косвенной адресации. Байт константы может быть передан в аккумулятор из ячейки памяти программ, адресуемой суммой базового регистра (PC или DPTR) и индексного регистра (содержимого А). Это обеспечивает, например, удобное средство реализации алгоритма преобразования кода ASCII в семисегментный код.

Любая ячейка 256-байтового блока внешнего ОЗУ данных может быть выбрана с использованием косвенно-регистровой адресации через регистры указатели R0 или R1 (выбранного банка рабочих регистров).

Ячейка внутри адресного пространства 64 Кбайт внешнего ОЗУ также может быть выбрана с использованием косвенно-регистровой адресации через регистр-указатель данных DPTR.

Команды передачи между прямо адресуемыми регистрами позволяют заносить величину из порта в ячейку внутреннего ОЗУ без использования рабочих регистров или аккумулятора.

В логическом процессоре любой прямо адресуемый бит может быть помещен в бит переноса и наоборот.

Содержимое аккумулятора может быть обменено с содержимым рабочих регистров (выбранного банка) и с содержимым адресуемых с помощью косвенно-регистровой адресации ячеек внутреннего ОЗУ, а также с содержимым прямо адресуемых ячеек внутреннего ОЗУ и с содержимым регистров специального назначения.

Младшая тетрада (разряды 3-0) содержимого аккумулятора может быть обменяна с младшей тетрадой содержимого ячеек внутреннего ОЗУ, выбираемых с помощью косвенно-регистровой адресации.

Команды ветвления и передачи управления. Адресное пространство памяти программ ОМЭВМ не имеет страничной организации, что позволяет свободно перемещать фрагменты программы внутри адресного пространства, при этом не требуется перезасылка (изменение) номера страницы.

Перемещение отдельных фрагментов программы обеспечивает возможность использования перемещаемых программных модулей различными программами.

Команды 16-разрядных переходов и вызовов подпрограмм позволяют осуществлять переход в любую точку адресного пространства памяти программ объёмом 64 Кбайт.

Команды 11-разрядных переходов и вызовов подпрограмм обеспечивают переходы внутри программного модуля емкостью 2 Кбайт. В системе команд имеются команды условных и безусловных переходов относительно начального адреса следующей команды в пределах от (РС)-128 до (РС)+127. Команды проверки отдельных разрядов позволяют осуществлять условные переходы по состоянию "0" или "1" прямо адресуемых битов. Команды проверки содержимого аккумулятора (на ноль/не ноль) позволяют осуществлять условные переходы по содержимому А.

Косвенно-регистровые переходы в системе команд ОМЭВМ обеспечивают ветвление относительно базового регистра (содержимого DPTR или PC) со смещением, находящимся в аккумуляторе А.

Команды битового процессора. Битовый процессор является частью архитектуры ОМЭВМ семейства MCS-51 и его можно рассматривать как независимый процессор побитовой обработки. Битовый процессор выполняет свой набор команд, имеет свое побитово адресуемое ОЗУ и свой ввод-вывод.

Команды, оперирующие с битами, обеспечивают прямую адресацию 128 битов (0–127) в шестнадцати ячейках внутреннего ОЗУ (ячейки с адресами 20Н–2FH) и прямую побитовую адресацию регистров специального назначения, адреса которых кратны восьми:

Р0(80Н), TCON(88H), Р1(90Н), SCON(98H), Р2(А0Н), IЕ(А8Н), РЗ(В0Н), IР(В8Н), PSW(D0H), А(Е0Н), B(F0H).

Каждый из отдельно адресуемых битов может быть установлен в "1", сброшен в "0", инвертирован, проверен. Могут быть реализованы переходы: если бит установлен; если бит не установлен; переход, если бит установлен, со сбросом этого бита; бит может быть перезаписан в (из) разряда переноса. Между любым прямо адресуемым битом и флагом переноса могут быть произведены логические операции "И", "ИЛИ", где результат заносится в разряд флага переноса. Команды побитовой обработки обеспечивают реализацию сложных функций комбинаторной логики и оптимизацию программ пользователя.

Похожие работы

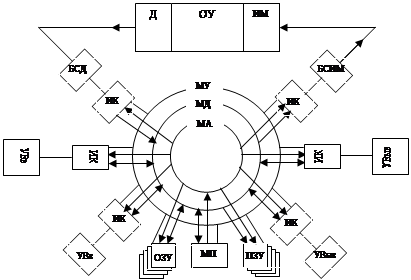

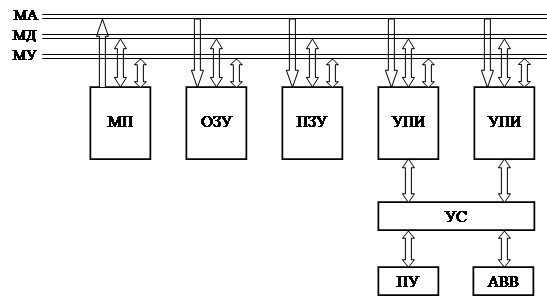

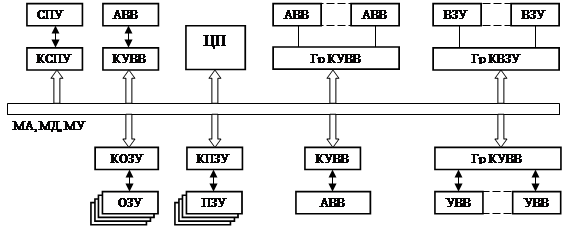

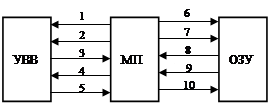

... ввести распределенную обработку во всех подсистемах вычислительной системы, что определяет новые способы организации вычислительных процессов в системах с децентрализованными управлением и обработкой информации. 2. Интерфейс микропроцессоров Для включения микропроцессора в любую микропроцессорную систему необходимо установить единые принципы и средства его сопряжения с остальными устройствами ...

... 0,1098 4.4 Выбор сторожевого таймера. Т.к. работа системы происходит в автономном режиме и не предусматривает работу оператора с ней, то для случая зависания микро-ЭВМ в схему системы сбора данных добавляется интегральная микросхема MAX690AMJA – сторожевой таймер. Выполняющая две основные функции: выведение МП из состояния зависания и сброс МП при включении питания. Основные характеристики ...

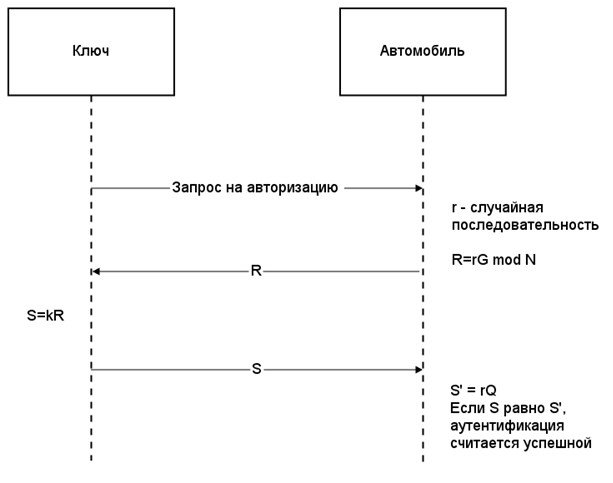

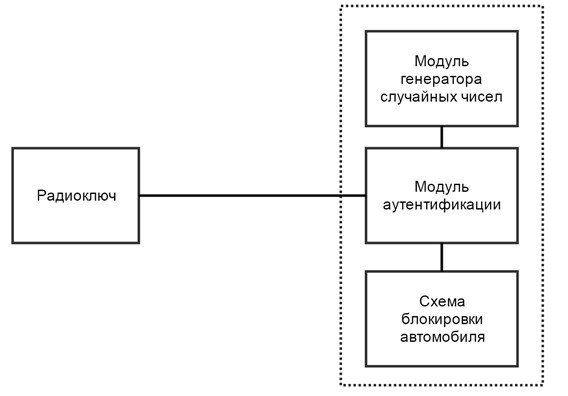

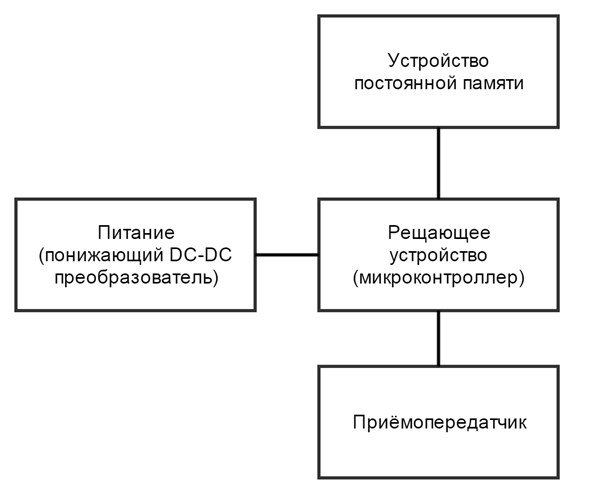

... является допустимым для устройства подобного рода. 5.3 Вывод В результате анализа параметров энергосбережения было выявлено то, что при реализации системы аутентификации пользователя транспортного средства нельзя обойтись без анализа энергопотребления системы и поиска путей уменьшения этого параметра. Изначально спроектированная система вызывала бы дискомфорт у пользователя за счёт излишне малого ...

... ввод ложного сообщения (даже ранее записанного с того же голоса) легко обнаруживается по изменению содержания. Технические требования предъявляемые к системе взаимодействия периферийных устройств при обработке данных в стандарте DES. Система взаимодействия с периферийными устройствами должна работать в режиме открытой и закрытой передачи. В открытом режиме на передаче информация не шифруется, ...

0 комментариев