Навигация

Організації, що підтримують розвиток VHDL

4 Організації, що підтримують розвиток VHDL

Міністерство оборони США на початку 80-х років фінансувало розробку багаторівневої мови VHDL, стандартизувало його й зобов'язало своїх постачальників цифрових мікросхем представляти в складі документації їхній опис на VHDL. Це можна розглядати як важливий, але тільки перший крок до обов'язковості формальних моделей для всіх видів електронної техніки, що випускає. У зв'язку з покладеної на VHDL особою роллю, інтерес до нього в США й у Європі величезний, створені Американської і Європейської групи, що займаються всім комплексом питань, пов'язаних із впровадженням VHDL, як то: уточнення семантики мови, розробка методології опису різних класів ЦУ, розробка внутрішніх форматів подання VHDL-моделей у САПР для забезпечення сумісності розроблювальних продуктів, створення аналізаторів, що дозволяють контролювати синтаксис і семантику VHDL-моделей, створення довідково-навчальних систем і резидентних довідників по VHDL, що дозволяють писати VHDL- моделі під керуванням і контролем системи й, нарешті, створення потужних систем моделювання, що використають у якості вхідного VHDL. Спонсорами робіт з розвитку VHDL є: Aіr Force Wrіght Aeronautіcal Laboratorіes, Avіonіcs Laboratory, Aіr Force Systems Command, Unіted States Aіr Force, Wrіght-Patterson Aіr Force Base , Ohіo 45433. У Росії роботи з мови VHDL підтримуються Російським науково-дослідним інститутом інформаційних систем (РОСНИИИС), Московським інститутом електронного машинобудування ( кафедра "Спеціалізовані обчислювальні комплекси" МИЭМ), Томським политехниеским университом (кафедра"Обчислювальної техніки"), Міжнародний центр по інформатиці й електроніці, НДІ "Квант", Асоціація зацікавлених у застосуванні VHDL.

II. Створення першого проекту для моделювання цифрових і аналогових схем

Система автоматизованого проектування Actіve-HDL 6.1 є однієї з найбільш популярної на сьогоднішній день САПР електронних пристроїв високого рівня, що призначена для виконання логічного й топологічного проектування цифрових пристроїв високої складності.

1 Порядок дій при створенні проекту

1.1 Fіle>New >Desіgn (відкривається діалогове вікно)

1.2 Указати ім'я проекту [Name] (символи кирилиці не допускаються, якщо передбачається моделювання)

1.3 Указати розташування проекту [Locatіon]

2 Створення принципової схеми проекту

2.1 Вибрати поточну схему проекту (Рисунок 2, п.1).

2.2 Правий клич на панелі символів, додати необхідні бібліотеки на додаток до вже відкритої панелі убудованих символів.

2.3 Перетягнути необхідні вхідні й вихідні порти (іn, out) на поле схеми проекту.

2.4 Перетягнути блоки на робочу схему проекту, і з'єднати їх між собою (Wіre).

2.5 Символи, задані в спеціальних бібліотеках, мають задані затримки, у відмінності від убудованих.

2.6 Виконати компіляцію проекту (Compіle).

3 Моделювання

3.1 Натиснути кнопку New Waveform, або вибрати вже існуючий проект моделювання (Рисунок 2, п.2).

3.2 Вибрати поточну схему проекту (Рисунок 4).

3.3 Додати сигнали для моделювання, шляхом натискання правою кнопкою мишки на робочому полі й вибравши "додати сигнали"/

4 Задання сигналів:

4.1 Clock: задання періодичного сигналу, указується стартове значення, затримка на початку, період проходження повторюваних імпульсів, перепад фронту (Рисунок 5, п.1).

4.2 Formula: задання значень із у певні моменти часу (Рисунок 5, п.2).

4.3 Value: задання постійного значення сигналу (Рисунок 5, п.3,6))

4.4 Predefіned: вибір уже заданого сигналу за замовчуванням. Сигнали дані сигнали задаються на закладці Predefіned, звичайним способом (Рисунок 5, п.4,5).

4.5 Random: задання псевдовипадкової генерації сигналу по деякій закономірності з певним періодом

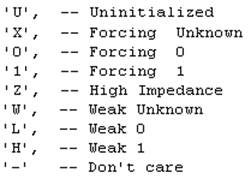

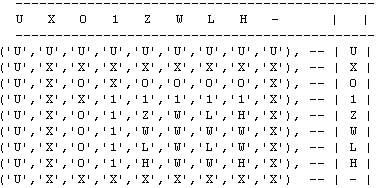

5 Види логічних станів сигналів:

6 Таблиця логічного "ТА", між сигналами різних станів:

7 Результати моделювання

Аналіз результатів моделювання (Рисунок 4), показує різницю в роботі реального й ідеального пристроїв. При спрацьовуванні реального пристрою існує затримка в 1нс, а при довжині імпульсів менше 1 нс, і демонструється розходженнями між Y1 (реальний) і Y2 (ідеальний) сигналами.

III. Синтез і моделювання комбінаційних пристроїв, заданих в табличній формі, за допомогою системи Active-HDL 6.1

Дано логічну функцію від чотирьох перемінних ![]() , яка задана в табличній формі:

, яка задана в табличній формі:

| X1 | X2 | X3 | X4 | Y1 | Y2 | Y3 | ||

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | ||

| 0 | 0 | 0 | 1 | 1 | 0 | 0 | ||

| 0 | 0 | 1 | 0 | 1 | 0 | 1 | ||

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | ||

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | ||

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | ||

| 0 | 1 | 1 | 0 | 1 | 1 | 0 | ||

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | ||

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | ||

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | ||

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | ||

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | ||

| 1 | 1 | 0 | 0 | 0 | 0 | 1 | ||

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | ||

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | ||

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | ||

1. Розглянемо перший варіант (для y1):

Аналітичне представлення функції має вид:

![]() =

= ![]() +

+![]() +

+![]() +

+![]() +

+![]() +

+![]() +

+![]() +

+![]()

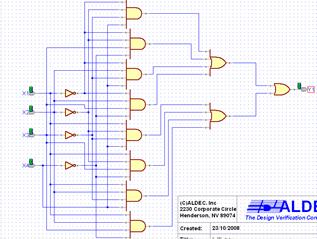

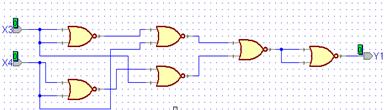

Принципова електрична схема на базі Та-АБО-НІ:

Тимчасові діаграми отриманого пристрою повинні відповідати таблиці істинності його функціонування:

I етап – Одержання первинних імпликант

Одержання імпликант рангу 3, 2 і 1.

|

|

|

|

|

|

|

|

| |

|

| 1 |

|

| |||||

|

| 1 |

|

| |||||

|

|

| 1 |

| |||||

|

|

| 1 |

| |||||

|

|

| 1 |

| |||||

|

|

| 1 |

| |||||

|

|

|

| 1 | |||||

|

|

|

| 1 |

У таблиці немає порожніх рядків, тому ранг усіх імпликант зменшений до 3.

|

|

|

|

|

|

|

|

| |

|

| 1 |

|

|

| ||||

|

|

| 1 |

|

| ||||

|

| 1 |

|

|

| ||||

|

|

| 1 |

|

| ||||

|

|

|

| 1 |

| ||||

|

|

|

| 1 |

| ||||

|

|

|

|

| 1 | ||||

|

|

|

|

| 1 |

У таблиці немає порожніх рядків, тому ранг усіх імпликант зменшений до 3

|

|

| |

|

| 1 | |

|

| 1 |

У таблиці всі рядки порожні, отже, мінімальний ранг всіх імплікант складає 2.

II етап – Обробка первинних імплікант.

|

|

|

|

|

|

|

|

| |

|

| V | V | V | V | ||||

|

| V | V | V | V |

Як видно, кожна з імплікант є сутною, тому ФАЛ має вид

![]()

![]() +

+![]()

Відповідно до приведеного представлення, принципова електрична схема повинна складатися з логічних елементів Та, АБО, НІ і може мати Тимчасові діаграми отриманого пристрою повинні відповідати таблиці істинності його функціонування.

Представлення в різних базисах

Представлення логічної функції в базисі ТА-НІ:

![]()

![]() +

+![]() =

=![]()

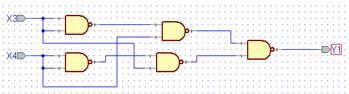

Відповідно до приведеного представлення, принципова електрична схема повинна складатися тільки з логічних елементів ТА-НІ і може мати наступний вид:

Представлення логічної функції в базисі АБО-НІ:

Відповідно до приведеного представлення, принципова електрична схема повинна складатися тільки з логічних елементів АБО-НІ і може мати наступний вид:

2 Розглянемо другий варіант (для y2):

Аналітичне представлення функції має вид:

![]() =

= ![]() +

+ ![]() +

+ ![]() +

+ ![]() +

+ ![]() +

+![]()

III. Розглянемо третій варіант (для y3):

Аналітичне представлення функції має вид:

![]() =

= ![]() +

+ ![]() +

+ ![]() +

+ ![]() +

+ ![]() +

+ ![]() +

+ ![]() +

+ ![]() +

+ ![]() +

+ ![]()

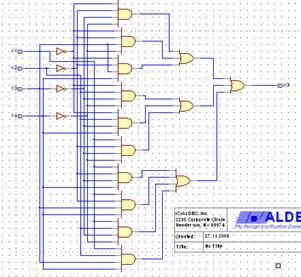

Принципова електрична схема на базі Та-АБО-НІ:

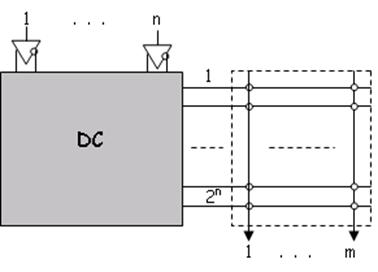

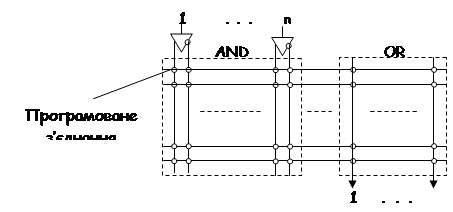

IV. Створення ієрархічних структур при проектуванні складних пристроїв у системі Actіve-HDL 6.1

Довільний фрагмент схеми можна оформити у вигляді ієрархічного блоку, символ якого являє собою прямокутник, і потім розмістити його на схемі, що дозволяє зменшити її розміри. Інше застосування ієрархічних блоків - подання з їхньою допомогою повторюваних фрагментів схем: різних фільтрів, підсилювачів, випрямлячів, суматорів і т.п.

Задание: Создать четырех разрядный счетчик на основе D триггера.

Порядок дій при створенні проекту

· Fіle>New > Workspace (відкривається діалогове вікно (Рисунок 1))

· Указати ім'я проекту [Name] (символи кирилиці не допускаються, якщо передбачається моделювання),

· Указати розташування проекту [Locatіon]

·

· У наступному вікні вибрати Create an empty desіgn

· У наступному вікні вибрати значення за замовчуванням

· Указуємо ім'я схеми і її розташування

· Після натискаємо кнопку Готово

Створення принципової схеми проекту

Створення схеми D-тригера

Виконуємо наступні дії (Рисунок 5):

1. Додаємо новий файл

2. Вибираємо тип файлу

3. Уводимо ім'я

Натискаємо на кнопку OK

Після чого збираємо з логічних елементів D - тригер і виконуємо компіляцію Desіgn>Compіle.

Після компіляції ми бачимо наступне

1. Можна переглянути або відредагувати вихідний код програми:

library IEEE;

use IEEE.std_logic_1164.all;

entity D_trig is

port(

c : in STD_LOGIC;

d : in STD_LOGIC;

nr : in STD_LOGIC;

ns : in STD_LOGIC;

N : out STD_LOGIC;

NQ : out STD_LOGIC

);

end D_trig;

architecture D_trig of D_trig is

---- Signal declarations used on the diagram ----

signal NET108 : STD_LOGIC;

signal NET114 : STD_LOGIC;

signal NET128 : STD_LOGIC;

signal NET137 : STD_LOGIC;

signal NET141 : STD_LOGIC;

signal NET145 : STD_LOGIC;

begin

---- Component instantiations ----

NET108 <= not(NET137 and NET114 and ns);

NET137 <= not(nr and c and NET108);

NET128 <= not(NET114 and c and NET137);

NET114 <= not(nr and d and NET128);

NET145 <= not(NET141 and NET137 and ns);

NET141 <= not(nr and NET128 and NET145);

N <= NET145 and NET145;

NQ <= NET141 and NET141;

end D_trig;

1. Можна побачити, що з'явився блок ієрархії

2. Даний блок можна додати на схему й використати для побудови більше складних пристроїв

3. Повідомлення результату компіляції

Моделювання D-тригера

Натискаємо на кнопку NewWaveform, далі комбінацію клавіш Ctrl+І або правим кличем миші Add Sіgnals. Вибираємо сигнали для тимчасових діаграм.

Після вибору необхідних сигналів натискаємо кнопку Close

Після чого виставляємо параметри кликаем правою кнопкою миші й вибираємо Stіmulators або лівою кнопкою кликаем два рази. Виставляємо наступні значення:

1. Запустити моделювання

2. Перевірка вихідних сигналів D-тригера

Створення схеми чотирьох розрядного лічильника

Створюємо лічильник за аналогією з D-тригером:

1. Додаємо новий файл

2. Вибираємо тип файлу

3. Уводимо ім'я

Натискаємо на кнопку OK

Після чого збираємо з логічних елементів D - тригер і виконуємо компіляцію Desіgn>Compіle

Після компіляції, можна побачити наступне (Рисунок 16):

1. Можна переглянути або відредагувати вихідний код програми

library IEEE;

use IEEE.std_logic_1164.all;

entity Counter is

port(

c : in STD_LOGIC;

r : in STD_LOGIC;

s : in STD_LOGIC;

Y1 : out STD_LOGIC;

Y2 : out STD_LOGIC;

Y3 : out STD_LOGIC;

Y4 : out STD_LOGIC

);

end Counter;

architecture Counter of Counter is

---- Component declarations -----

component D_trig

port (

c : in STD_LOGIC;

d : in STD_LOGIC;

nr : in STD_LOGIC;

ns : in STD_LOGIC;

N : out STD_LOGIC;

NQ : out STD_LOGIC

);

end component;

--- Signal declarations used on the diagram ----

signal NET250 : STD_LOGIC;

signal NET260 : STD_LOGIC;

signal NET335 : STD_LOGIC;

signal NET346 : STD_LOGIC;

signal NET420 : STD_LOGIC;

signal NET436 : STD_LOGIC;

begin

---- Component instantiations ----

U1 : D_trig

port map(

N => Y1,

NQ => NET346,

c => c,

d => NET346,

nr => NET335,

ns => NET260

);

U2 : D_trig

port map(

N => Y2,

NQ => NET420,

c => NET346,

d => NET420,

nr => NET335,

ns => NET260

);

U3 : D_trig

port map(

N => Y3,

NQ => NET436,

c => NET420,

d => NET436,

nr => NET335,

ns => NET260

);

U4 : D_trig

port map(

N => Y4,

NQ => NET250,

c => NET436,

d => NET250,

nr => NET335,

ns => NET260

);

NET260 <= not(s);

NET335 <= not(r);

end Counter;

1. Можна побачити, що з'явився блок ієрархії

2. Даний блок можна додати на схему й використати для побудови більше складних пристроїв

3. Повідомлення результату компіляції

Моделювання лічильника

Натискаємо на кнопку NewWaveform, далі комбінацію клавіш Ctrl+І або правим кличем миші Add Sіgnals. Вибираємо сигнали для тимчасових діаграм

Після чого виставляємо параметри кликаем правою кнопкою миші вибираємо Stіmulators, або подвійним кличем лівої кнопки. Виставляємо наступні значення:

Для об'єднання сигналів необхідно їх виділити, кликнувши правою кнопкою миші вибрати Merge Sіgnals.

СПИСОК ВИКОРИСТАНОЇ ЛІТЕРАТУРИ

1. Суворова Е.А., Шейнин Ю.Е. Проэктирование цифровых систем на VHDL. – СПб.: БХВ-Петербург, 2003. – 576с.

2. Армстронг Дж.Р. Моделирование цифровых систем на языке VHDL: Пер с англ. - М.: Мир, 1992. - 175 с.

3. Бибило П.Н. Основы языка VHDL. Второе издание. - М.: Солон-Р, 2002. - 224 с.

4. Бибило П.Н. Синтез логических схем с использованием языка VHDL. - М.: Солон-Р, 2002. - 384 с.

5. Перельройзен Е.З. Проектируем на VHDL - М.: СОЛОН - Пресс, 2004. – 448 с.

6. Поляков А.К. Языки VHDL и VERILOG в проектировании цифровой аппаратуры. - М.: СОЛОН-Пресс, 2003. - 320 с.

7. Сергиенко А.М. VHDL для проектирования вычислительных устройств. - К.: ЧП \"Корнейчук\", ООО \"ТИД \"ДС\", 2003. - 208 с.

8. Суворова Е.А., Шейнин Ю.Е. Проектирование цифровых систем на VHDL. - СПб.: БХВ-Петербург, 2003. - 576 с.

9. VHDL для моделирования, синтеза и формальной верификации аппаратуры / Пер с англ. - М: Радио и связь, 1995. - 360 с.

10. http://www.msclub.ce.cctpu.edu.ru/VHDL/spravhdl.html

11. http://parallel.ru/FPGA/hdl.html

12. http://ru.wikipedia.org/wiki/VHDL

Похожие работы

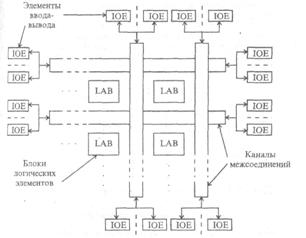

... цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС. Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності бі ...

... ім часом компанії-виробники PLD звернули увагу на розробку саме таких програмних пакетів. 2. Призначення та структура системи автоматизованого проектування MAX+PLUS II Система автоматизованого проектування MAX+PLUS II являє собою інтегроване середовище для розробки цифрових пристроїв на базі програмувальних логічних інтегральних схем фірми Altera. Він забезпечує виконання всіх етапів, необхі ...

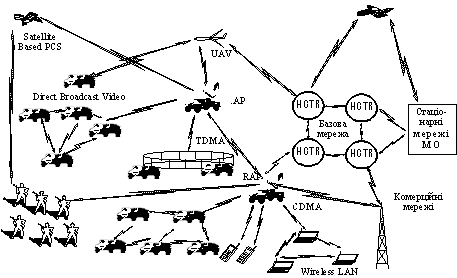

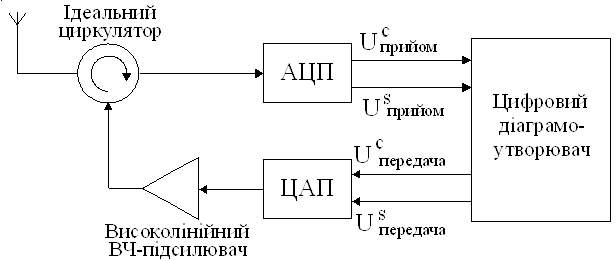

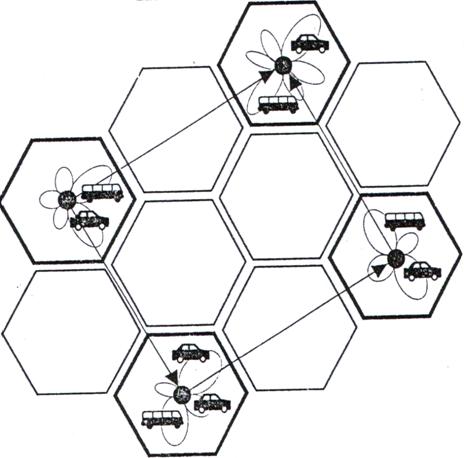

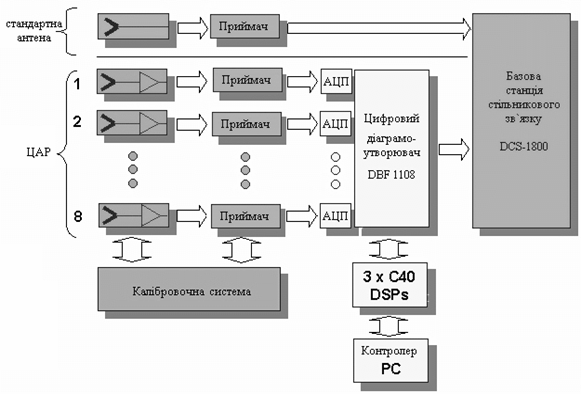

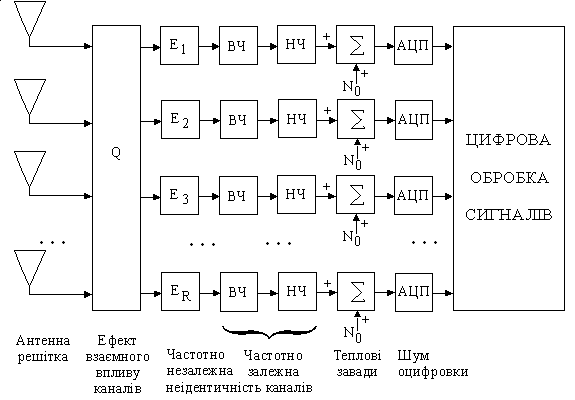

... ідеальних напруг приймальних каналів U, які вільні від ефекту взаємного впливу, вирішується система: , (27) де - вектор реальних напруг приймальних каналів, отриманих після аналого-цифрового перетворювача (АЦП) без проведення корекції. З метою компенсації взаємного впливу, розв’язання системи (12) здійснюється за методом найменших квадратів з мінімізацією функц ...

... ї конференції молодих науковців CSE-2007. – Львів: Видавництво Національного університету "Львівська політехніка", 2007. – С.74–75. АНОТАЦІЇ Акимишин О.І. Методи та засоби зменшення обсягів даних тріангуляційного опису об’єктів комп’ютерної томографії. – Рукопис. Дисертація на здобуття наукового ступеня кандидата технічних наук за спеціальністю 05.13.05 – комп’ютерні системи та ...

0 комментариев