Навигация

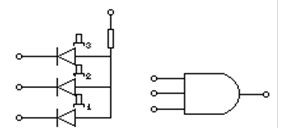

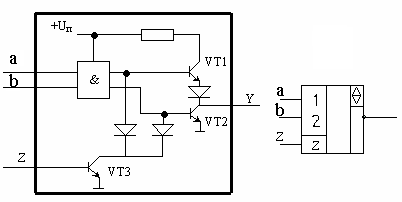

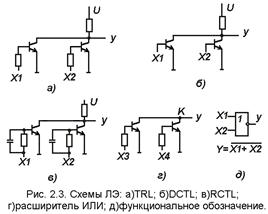

Упростить схему проектируемого устройства за счет исключения дополнительных элементов, реализующих операцию И;

1. Упростить схему проектируемого устройства за счет исключения дополнительных элементов, реализующих операцию И;

2. Обеспечить работу нескольких выходов на общую шину, т.е. реализовать режим работы с разделением информации по времени.

Базовые логические элементы эмиторно-связной логикиПричиной появления БЛЭ ЭСЛ явилось желание повысить быстродействие цифровых устройств. Это желание привело к использованию в них совершенно отличного от ТТЛ схемотехнического решения. Как было показано выше, основными причинами инерционности ключей, выполненных на биполярных транзисторах, являются время рассасывания неосновных носителей из его базовой области и постоянная времени перезарядки выходной емкости. Если время рассасывания транзистора при работе последнего в активной области может быть полностью исключено, то от влияния постоянной времени перезаряда выходной емкости транзистора полностью избавиться не представляется возможным. Это влияние можно лишь уменьшить путем увеличения коллекторного тока транзистора, как это было сделано в БЛЭ ТТЛ серии 513. При неизменном постоянном токе перезарядка выходной емкости транзистора, длительность его перехода из состояния, классифицируемого как логического 0, в состояние, классифицируемого как логической 1 и обратно может быть уменьшено только за счет уменьшения логического перепада. Такое решение позволяет повысить быстродействие. Однако дается оно за счет снижения помехоустойчивости БЛЭ, что требует создания схем при прочих равных условиях менее подверженных действию помех. Этот принцип и использован при построении БЛЭ ЭСЛ.

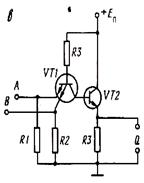

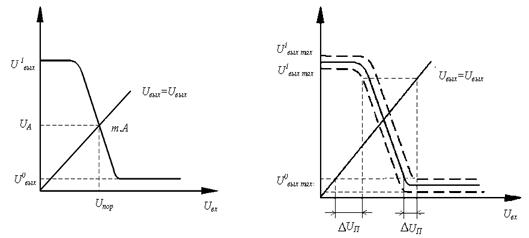

Основой БЛЭ ЭСЛ является токовый ключ, выполненный на двух транзисторах, в соответствии с рисунком 6. На базу одного из них, например VT2, подано некоторое постоянное опорное напряжение Uоп. Изменение напряжения подаваемого на вход х0 ниже или выше Uоп приводит к перераспределению постоянного тока Iэ, заданного токостабилизирующим резистором Rэ, между транзисторами VT1 и VT2. При этом транзисторы не попадают в режим насыщения и, следовательно, в ключе принципиально отсутствует интервал рассасывания их неосновных носителей. Таким образом, особенностью БЛЭ ЭСЛ является постоянство потребляемого тока независимо от выходного сигнала ключа.

Эта особенность выгодно отличает БЛЭ ЭСЛ от БЛЭ ТТЛ, в котором момент переключения ток, потребляемый элементом, резко возрастет, создавая внутренние помехи, ухудшающие помехозащищенность цифрового устройства.

Не трудно заметить, что общей шиной является шина +Uп, в результате чего потенциалы точек схемы отрицательны относительно общей шины. Однако в схеме токового ключа так же, как и в схемах ТТЛ, реализован принцип положительной логики, при котором большему выходному напряжению соответствует сигнал логической 1, а меньшему – сигнал логического 0.

Не трудно заметить, что общей шиной является шина +Uп, в результате чего потенциалы точек схемы отрицательны относительно общей шины. Однако в схеме токового ключа так же, как и в схемах ТТЛ, реализован принцип положительной логики, при котором большему выходному напряжению соответствует сигнал логической 1, а меньшему – сигнал логического 0.

Быстродействие такого ключа весьма велико, так как, во-первых, транзисторы принципиально не заходят в область насыщения, и, во-вторых, мал логический перепад напряжений между значениями логического нуля и логической единицы. Последнее реализовано выбором малых сопротивлений резисторов Rк1 и Rк2 схемы, что крайне полезно с точки зрения уменьшения постоянной времени перезаряда выходной емкости транзистора.

С токового ключа снимаются одновременно два сигнала – прямой и инверсный, связанные с сигналом х0 на входе схемы соотношениями:

y1 = x0

y0 = ![]()

Следует отметить, что схемотехнически токовый ключ, в соответствии с рисунком 6, повторяет схему дифференциального усилителя постоянного тока.

Выходное напряжение, снимаемое с выходов y1 и у0 всегда больше Uоп, так как транзисторы VT1 и VT2 всегда работают в ненасыщенном режиме. Поэтому непосредственное последовательное включение нескольких таких ключей невозможно. Для этого необходим согласующий каскад. В качестве такого согласующего каскада используются схемы эммитерных повторителей включенных между выходами токового ключа и выходами элемента.

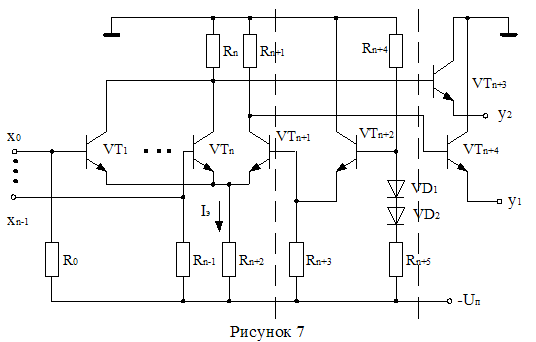

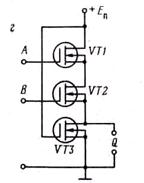

Полная схема БЛЭ, выполненного на основе токового ключа, приведена в соответствии с рисунком 7. Базовый элемент получен путем замены входного транзистора VT1 токового ключа группой параллельно включе6нных транзисторов VT1 – VTn.

Функционально схему БЛЭ можно разбить на три узла:

1. Токовый ключ на транзисторах VT1 – VTn+1 и резисторе Rn+2;

2. Источник эталонного напряжения, включающий параметрический стабилизатор на элементах Rn+4, VD1, VD2, Rn+5 и эммиторный повторитель на VTn+2 и Rn+3;

3. Выходные эммиторные повторители на транзисторах VTn+3 и VTn+4.

Цепь нагрузок транзисторов VTn+3 и VTn+4 вынесена из ИС БЛЭ, что способствует снижению рассеиваемой в ней мощности и расширению функциональных возможностей.

Диоды VD1, VD2 в задающей цепи источника эталонного напряжения служат для термокомпенсации напряжения Uоп.

Принцип действия и функциональные возможности БЛЭ ЭСЛ.Предположим, что на все входы схемы, в соответствии с рисунком 7, х0, ..., хn-1 подано напряжение, близкое к –Uп. Тогда транзисторы VT1 - VTn будут заперты. Весь ток резистора Rn+2 протекает через транзистор VTn+1, к выводу базы которого приложено напряжение Uоп. Этот транзистор поддерживается в активном режиме работы за счет действия глубокой последовательной отрицательной обратной связи по току. Если не учитывать обратные токи коллекторных переходов транзисторов VT1 - VTn, через резистор Rn протекает только базовый ток транзистора VTn+3 выходного эммиторного повторителя. Следовательно, напряжение на выходе близко к нулевому

Uy2 = -Iб VTn+3 · Rn – Uбэ VTn+3

Численно напряжение Uy2 примерно равно –0,9 В.

Через резистор Rn+1 кроме базового тока транзистора VTn+4 протекает ток Iк VTn+1, примерно равный Iэ. Эти токи создают на резисторе Rn+1 падение напряжения, равное:

URn+1 = (Iк n+1 + Iб n+4)Rn+1 = [(Iэ·h21э)/(h21э + 1)+ Iб n+4] ≈ Iэ · Rn+1

Это напряжение преобразуется выходным эммиторным повторителем на транзисторе VTn+4 в выходное напряжение Uy1, определяемое выражением:

Uy1 ≈ -Uбэ VTn+4 – IЭ · Rn+1

Численно напряжение Uy1 примерно равно –1,7 В.

Если хотя бы на один из входов схемы х0, ..., хn-1 подано напряжение, превышающее по уровню Uоп (-1,3 В), соответствующий транзистор VT перейдет в активный режим работы. Его ток будет равен току Iэ, что приведет к смене уровней выходного напряжения:

Uy2 ≈ -Uбэ VTn+3 – IЭ · Rn

Uy1 = -Iб VTn+4 · Rn+1 – Uбэ VTn+4

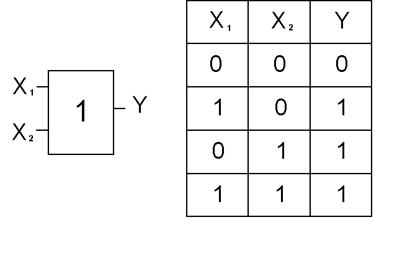

Из сказанного следует, что рассмотренная схема реализует по входу y2 операцию ИЛИ-НЕ, а по выходу у1 – операцию ИЛИ

у1 = (х0 + х1 + ... + хn-1)

у1 = ![]()

Резисторы R0 – Rn-1, включенные между базами транзисторов VT1 – VTn и выходом –Un, обеспечивает запертое состояние этих транзисторов при отсутствии входного сигнала. Это позволяет не беспокоиться о подключении неиспользуемых входов ИС выводом источника питания.

Особенностью схемотехнического построения элементов ЭСЛ является использования для подключения общей шины собственно такого переключателя и выходных эммиторных повторителей различных выводов ИС. Потребляемый ток, протекающий в этих цепях, имеет качественно различный характер. Как было отмечено ранее, в принципе работы токового ключа заложено потребление принципиально постоянного тока, так как его работа связана с перераспределением тока эммиторного резистор Rэ. Эммитерные же повторители потребляют импульсный ток. К тому же для улучшения частотных свойств сопротивления резисторов, подключаемых к выводам U1 и U2 ИС, выбираются весьма малыми (Rвнешн = 75 ... 100 Ом). Поэтому совместное питание этих цепей из-за малой величены логического перепада может приводить к ложному срабатыванию соседних элементов, т.е. появлению сбоев при обработке информации (внутренних помех). Разделение цепей питания позволяет устранить этот недостаток.

Раздельное питание токовых ключей и выходных эммиторных повторителей позволяет дополнительно решать задачу снижения мощности, рассеиваемой в реальной аппаратуре. Так как выходное напряжение элемента лежит диапазоне –0,9 ... – 1,7 В, то для питания внешних резисторов может быть использовано напряжение, не превышающее 2 В. Такое решение при малых сопротивлениях Rвнешн позволяет значительно уменьшить бесполезные потери мощности.

Рассмотренные функциональные возможности БЛЭ ЭСЛ простыми схемотехническими приемами могут быть существенно расширены. Для этого, как правило, используется два приема:

Похожие работы

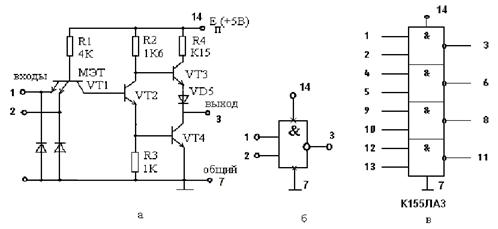

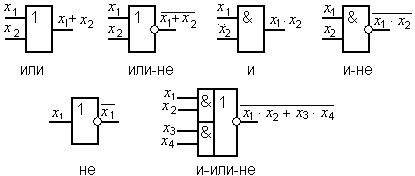

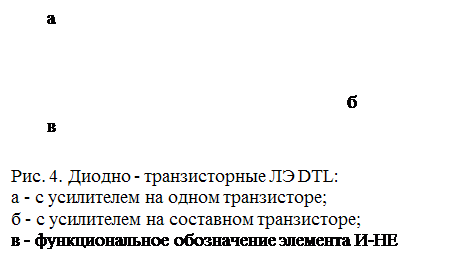

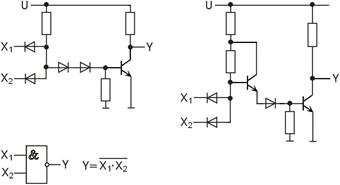

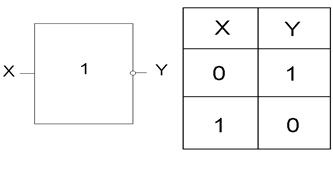

... 7. Логический элемент НЕ, выполненный на обычном биполярном транзисторе (а); многоэмиттерном транзисторе с дополнительным усилителем (б); Транзистор Шоттки и его условное графическое изображение в электронных схемах (в). Рис. 8. Логический элемент НЕ, выполненный на МОП-транзисторах с n-каналом (а), комплиментарной паре МОП-транзисторов с n- и р-каналами (б). Логический элемент И – ...

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

... первой логической ступени выполняется на транзисторах, увеличение параметра m требует значительного увеличения числа компонентов ЛЭ и роста площади кристалла ИМС. В существующих сериях интегральных микросхем основные логические элементы выполняются, как правило, с небольшим числом входов . Увеличение числа входов m обеспечивается за счет введения в серию ЛЭ специального расширителя, подключение ...

... V ~“ должна находиться в нажатом, а кнопка “ВСВ ВНК” в поле надписи “КВУ” - в отжатом состоянии. 4. Методические рекомендации к выполнению работы 4.1. Исследование особенностей функционирования логических элементов ДД1 ¸ ДД4 и определение их функционального назначения. 4.1.1. Задавая различные комбинации входных логических сигналов, определить значение выходного сигнала и по результатам ...

0 комментариев