Навигация

ВЫБОР ВАРИАНТА ТЕХНИЧЕСКОГО РЕШЕНИЯ

2. ВЫБОР ВАРИАНТА ТЕХНИЧЕСКОГО РЕШЕНИЯ

Мир современных технологий наполнен разнообразием микропроцессорных устройств. Десятки крупнейших фирм производителей конкурируют между собой, предлагая каждый день новую более совершенную продукцию. В курсовом проекте используется цифровая обработка сигналов. Для цифровой обработки сигналов используются так называемые сигнальные микропроцессоры. Рассмотрим некоторые микроконтроллеры, выпускаемые современной промышленностью, наиболее подходящие для реализации курсовой работы.

2.1 МИКРОПРОЦЕССОРЫ КОМПАНИИ ANLOG DEVICES.

Микропроцессоры компании Analog Devices образуют два семейства: ADSP21xx и ADSP210xx.

Семейство ADSP21xx – набор однокристальных 16-разрядных микропроцессоров с общей базовой архитектурой, оптимизированной для выполнения алгоритмов цифровой обработки сигналов и других приложений, требующих высокоскоростных вычислений с фиксированной точкой.

Второе семейство микропроцессоров ADSP210xx объединяет 32-х разрядные микропроцессоры, ориентированные на сигнальные алгоритмы, требующие вычислений с плавающей точкой.

В рамках каждого семейства микропроцессоров обеспечивается совместимость снизу вверх по системе команд. Старшие представители семейства обладают большими функциональными возможностями и содержат на кристалле дополнительные функциональные блоки.

Рассмотрим подробнее микропроцессоры первого семейства, так как их возможности наиболее подходят для реализации проекта.

Микропроцессоры семейства ADSP21xx успешно конкурируют с аналогичной продукцией других компаний производителей сигнальных процессоров благодаря сравнимой производительности при более низкой цене, а также развитой системе технических и программных средств разработки прикладных систем. Основными конкурентами данного семейства являются микропроцессоры DSP56xxx (Motorola) и TMS320C1x, TMS320C2xx, TMS320C5x (Texas Instruments).

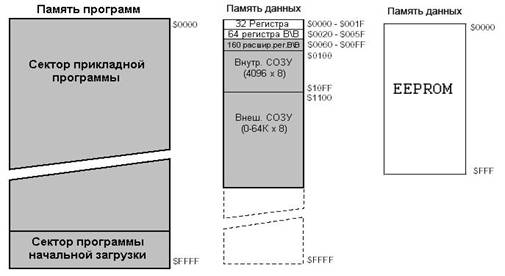

Высокая производительность процессоров на сигнальных алгоритмах достигается благодаря многофункциональной и гибкой системе команд, аппаратной реализации большинства типичных для данных приложений операций, высокой степени параллелизма процессов в микропроцессоре, сокращения командного такта. Микропроцессоры ADSP21xx имеют модифицированную Гарвардскую архитектуру, в рамках которой предусматривается возможность доступа в память команд, при ее физическом разделении с памятью данных.

Каждый микропроцессор семейства содержит три независимых полнофункциональных устройства: АЛУ, МАС – умножитель с накоплением, устройство барабанного сдвига. Каждое устройство непосредственно оперирует с 16-ти разрядными данными и обеспечивает аппаратную поддержку вычислений с различной точностью.

Микропроцессор содержит генератор адресов команд и два генератора адресов данных, обеспечивающие адресацию к данным и командам, расположенным как во внутренней, так и во внешней памяти. Параллельное функционирование генераторов сокращает длительность выполнения команды, позволяя за один такт выбирать из памяти команду и два операнда.

Таймер/счетчик микропроцессора обеспечивает периодическую генерацию прерываний.

Последовательные порты (SPORTs) обеспечивают последовательный интерфейс с большинством стандартных последовательных устройств, а также с аппаратными средствами сжатия-восстановления данных, использующими A- и m- законы компандирования.

Порт интерфейса с хост-процессором позволяет без дополнительных интерфейсных схем взаимодействовать с главным микропроцессором системы, в качестве которого может использоваться как процессор данного семейства, так и другой микропроцессор, например Motorola 68000 или Intel 8051.

Микропроцессор ADSP – 21msp5x отличается наличием аналогового интерфейса, позволяющего совмещать аналоговую и цифровую обработку. В состав интерфейсных средств входят АЦП, ЦАП, цифровой и аналоговый фильтры, параллельный интерфейс к процессорному ядру.

Система команд микропроцессоров семейства оптимизирована для алгоритмов цифровой обработки сигналов. По системе команд все микропроцессоры совместимы снизу вверх. Совершенствование данного семейства идет в направлении повышения тактовой частоты, снижения энергопотребления и расширения коммуникационных возможностей процессора.

2.2 МИКРОПРОЦЕССОРЫ КОМПАНИИ MOTOROLA

Сигнальные микропроцессоры компании Motorola. Подразделяются на семейства 16- и 24-разрядных микропроцессоров с фиксированной точкой – DSP – 560xx, - 561xx, - 563xx, -566xx, 568xx и микропроцессоры с плавающей точкой – DSP – 960xx.

Рассмотрим 24-х разрядные микропроцессоры с фиксированной точкой семейства DSP 560xx. Эти микропроцессоры являются первыми представителями сигнальных микропроцессоров компании Motorola. Архитектура микропроцессоров ориентирована на максимизацию пропускной способности в приложениях DSP с интенсивным обменом данными. Это обеспечивается благодаря расширяемой архитектуре со сложной встроенной периферией и универсальной подсистеме ввода/вывода. Данные свойства, а также низкое энергопотребление минимизируют сложность, стоимость и сроки разработки прикладных систем на базе микропроцессоров DSP56000/DSP56001.

Микропроцессоры работают на частоте 33МГц и обеспечивают производительность около 16 MIPS, что позволяет выполнять быстрое преобразование Фурье по 1024 отсчетам за 3,23мс.

Дальнейшее развитие семейства микропроцессоров осуществляется в рамках концепции процессорного ядра, общего для всех представителей семейства, в состав которого входят 24-разрядные микропроцессоры с фиксированной точкой.

Процессоры данного семейства характеризуются высокой пропускной способностью, расширенной разрядностью, обеспечивающей высокую точность вычисления и широким динамическим диапазоном обрабатываемых данных, поддержкой энергосберегающего режима работы. Представители семейства отличаются друг от друга конфигурациями памяти и периферийными устройствами.

Похожие работы

... 8-канальный АЦП и аналоговый компаратор; - последовательные интерфейсы UART0, UART0, TWI и SPI; - блоки прерывания и управления (включая сторожевой таймер). Архитектура ядра. Ядро микроконтроллера выполнено по усовершенствованной RISC-архитектуре. Арифметико-логическое устройство, выполняющее все вычисления, подключено непосредственно к 32 регистрам общего назначения. Благодаря этому АЛУ ...

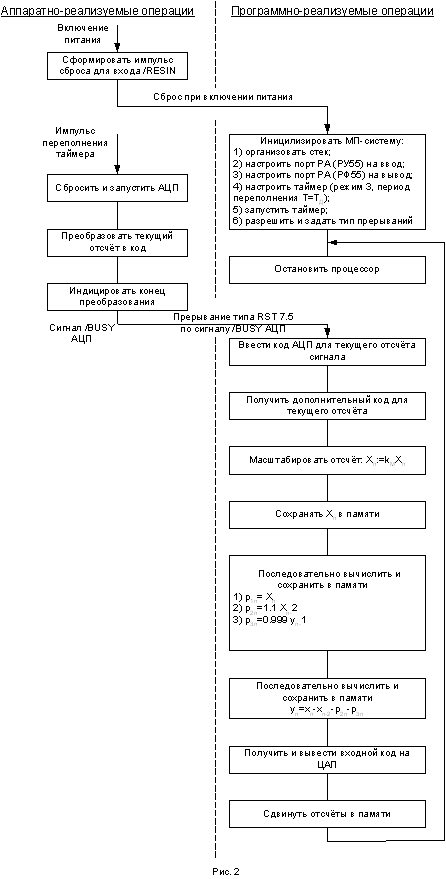

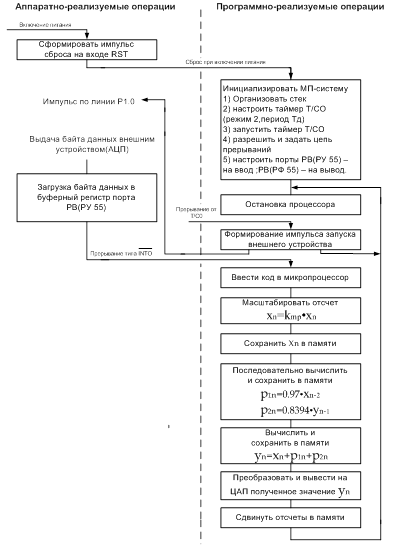

... данных в режиме простого обмена данными; q таймер (РУ55) останавливается; q содержимое ячеек ОЗУ и буферных регистров портов (РУ55) сохраняется. 3. Разработка общего алгоритма функционирования фильтра Общий алгоритм функционирования фильтра строится на основе выводов и определений, сделанных при анализе задачи, и включает в себя все функции устройства, реализуемые аппаратно и реализуемые ...

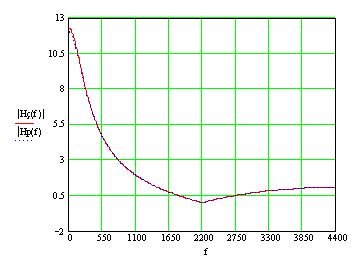

... , b2i , a2i определяют характеристики фильтра. При значениях коэффициентов фильтр имеет АЧХ фильтра верхних частот b 20 = 1;b 21 = 0;b 22 = 1.1; a 21 = 0.999;a 22 = 0.000 Разностное уравнение задает во временной области порядок получения выходной последовательности отсчетов из входной. В z-плоскости свойства цифрового фильтра описывает передаточная функция H(z), которая при двухкаскадной ...

... ; MOV X1, X ; MOV Y1, Y ; RETI ;возврат из подпрограммы обслуживания прерывания по входу END Исходные определения и ручной расчёт результатов работы программы: "Цифровой фильтр (нижних частот)". Разностное уравнение имеет вид: Представим уравнение в виде: , где , 1)Реализуемый коэффициент масштабирования (число без знака) при 8-разрядном формате беззнаковых коэффициентов: ;, ...

0 комментариев