Навигация

Оборудование для контроля и отладки проектных плат

2.5 Оборудование для контроля и отладки проектных плат

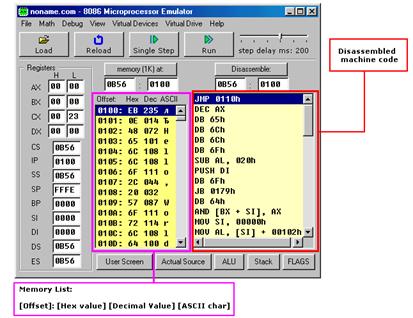

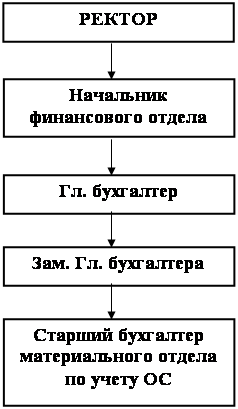

Оборудование для контроля и отладки проектных плат с интерфейсом по стандарту ISA или PCI представляют собой платы-удлинители для соответствующих интерфейсных плат, у которых каждая линия интерфейса имеет соединение с контролирующей БИС PLD.

Рис. 4 Оборудование для контроля и отладки проектных плат

Если ИС проектируемой платы поддерживают граничное сканирование (BST) через JTAG интерфейс, то разработанное на кафедре ПО позволит с помощью платы отладчика до установки разрабатываемой платы в ПК найти ошибки как в межсоединениях этих ИС между собой, так и в их соединениях с разъемом компьютера. Та же плата отладчика с другим вариантом ПО позволяет имитировать поведение любой мыслимой и немыслимой комбинации управляющих сигналов интерфейсной шины.

Плата отладчика может оказать существенную помощь разработчику аппаратуры и в тех случаях, когда штатная работа платы расширения нарушается трудно обнаруживаемыми сбоями. Встраивание в схемы PLD фрагментов таких отладочных средств, как следовые ОЗУ, логические анализаторы, разнообразные аппаратные ловушки позволяет разработчику облегчить задачу нахождения причины возникающих сбоев или перемежающихся.

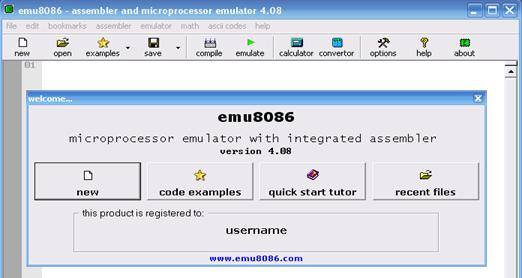

2.6 Комплекс средств тестирования методом граничного сканирования JTools

Функциональные возможности комплекса базируются на интерфейсе JTAG и технологии граничного сканирования (Boundary Scan Testing), которые широко поддерживаются ведущими производителями БИС (Intel, Motorola, Altera, Xilinx, Atmel, TI, и другими).

Функциональные возможности комплекса базируются на интерфейсе JTAG и технологии граничного сканирования (Boundary Scan Testing), которые широко поддерживаются ведущими производителями БИС (Intel, Motorola, Altera, Xilinx, Atmel, TI, и другими).

Состав комплекса:

универсальный загрузочный кабель; резидентная программа управления кабелем BitMaster; программа тестирования и отладки JTools.· CD, содержащий базу BSD-файлов, документацию и учебно-методи-ческие материалы, связанные с JTAG интерфейсом и методом граничного сканирования.

Комплекс реализует следующие функции:

· Эмуляция загрузочных кабелей фирм Altera (ByteBlaster MV), Xilinx (HW-DWNCBL-PC1), Atmel (ATDH2225);

· Контроль сигналов на внешних выводах БИС отлаживаемой системы;

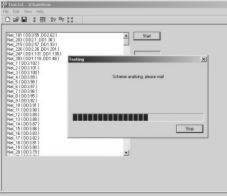

· Автоматический анализ реальной схемы устройства;

· Фиксирование состояния всех контактов по возникновению заданной комбинации сигналов.

· Режим полуавтоматической отладки БИС и JTAG цепочки.

2.7 Комплекс средств тестирования методом граничного сканирования (дополнительно)

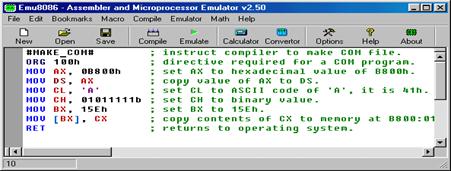

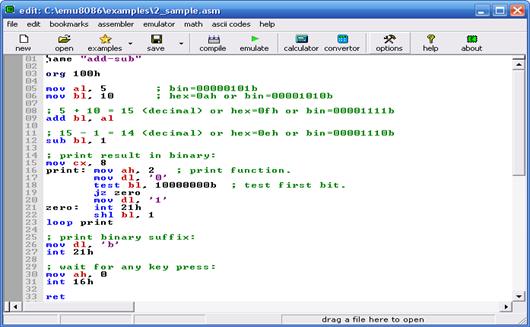

Эмуляция загрузочных кабелей Аппаратную основу комплекса образует универсальный кабель, используемый для тестирования методом граничного сканирования. Отличительной особенностью кабеля является наличие программно управляемого режима эмуляции загрузочных кабелей различных фирм производителей PLD.

Кабель поддерживает режимы внутрисхемной эмуляции и внутрикристальной отладки, для чего он имеет до 25 выводов управляющих сигналов и щупов для захвата событий.

Контроль сигналов Программно-аппаратный комплекс позволяет контролировать поведение проектов пользователя в реальных системах путем вывода на экран ПЭВМ состояния внешних контактов БИС, входящих в состав цепочки. Наблюдение не оказывает влияния на работу самой БИС. Более того, в режиме тестирования возможно выборочное управление состоянием выводов отдельных БИС (устанавливать уровень, отключать контакт от шины, генерировать меандр), обеспечивая совмещение рабочих и тестовых режимов отлаживаемой системы.

Автоматический анализ схемы Программное обеспечение позволяет произвести автоматический анализ схемы. Результат этого анализа - составление списка межсоединений, выделение контактов, на которых находиться константное значение, выделение контактов, значение на которых противоречит ожидаемому.

Режим полуавтоматической отладки БИС и JTAG цепочки Этот режим работы предназначен для анализа целостности JTAG цепочки и работоспособности БИС, входящих в цепочку. Проверки соответствия между реальной цепочкой и описанием, заданным пользователем. Предоставляться средства отладки соединения между компьютером и платой тестируемого цифрового устройства, а также JTAG цепочки на самой плате.

Фиксирование состояния всех контактов по возникновению заданной комбинации сигналов Этот режим требует подключения дополнительных щупов универсального кабеля к контрольным точкам. При возникновении на контрольных точках указанной комбинации сигналов будет сделан мгновенный "снимок" состояния всех контактов БИС, входящих в JTAG цепочку. После снимка программное обеспечение забирает в ПЭВМ полученную информацию и предоставляет её для анализа пользователю.

Заключение

В ходе работы было представлено описание отладочных средств для МК семейства НС05, которое демонстрирует широкий диапазон их функциональных возможностей и характеристик. Даже самые простые и доступные по цене МК позволяют создать законченную разработку очень эффективную в работе.

Также в реферате были рассмотрены средства отладки БИС на основе прототипных плат схем программируемой логики с интерфейсами ISA, PCI позволяющими отлаживать широкий спектр пользовательских проектов, ориентированных на различные виды БИС.

Используемая литература:

1. Микроконтроллер по цене транзистора // Chip News — 1998. — № 11-12. — С. 16–19.

2. Т. Ремизевич. Микроконтроллеры семейства НС05 фирмы Motorola // Chip News. — 1998. — № 11-12. — С. 22–26.

3. Шагурин И.И. Архитектура и функционирование микроконтроллеров семейства 68HC705 // Chip News. — 1999. — № 3. — С. 2–10.

4. Кобахидзе Ш. Нужны ли профессионалу инструментальные средства? // Инженерная микроэлектроника. — 1998. — № 1. — С. 2–10.

5. Буданов А. Средства разработки и отладки программного обеспечения промышленных контроллеров на базе 8/16-разрядных микропроцессоров фирмы MOTOROLA // Инженерная микроэлектроника. — № 1. — С. 32–35.

Похожие работы

аучного цикла является отсутствие возможности реальной постановки учебного, и лабораторного эксперимента. Хотя в настоящее время имеются разработки виртуальных лабораторных практикумов, однако окончательно решение проблемы требует пристального внимания специалистов различных профилей, в том числе и психолого-педагогического. 1.2 Роль технологии виртуальных приборов обучения в техническом вузе ...

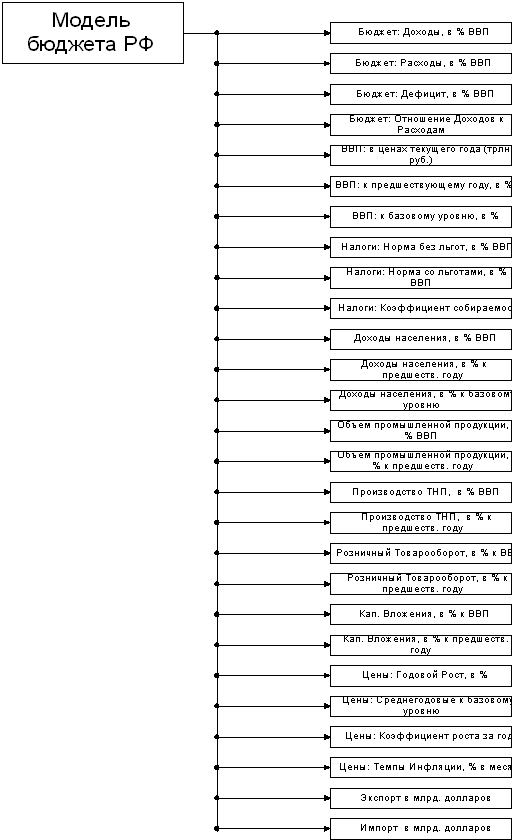

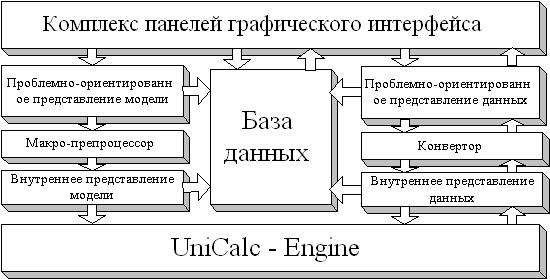

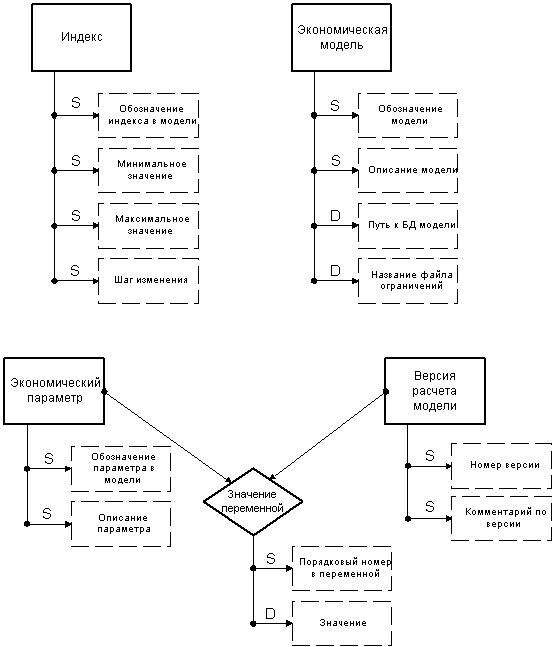

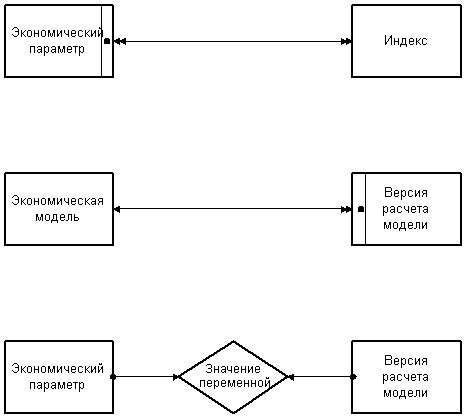

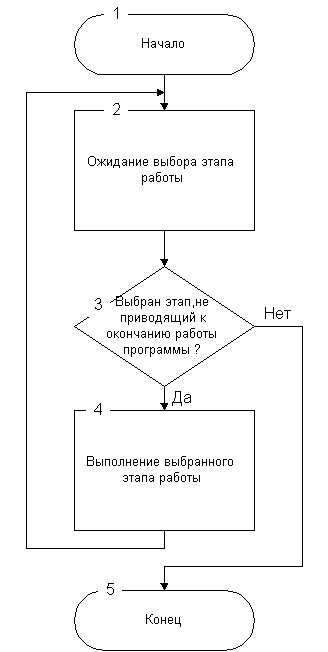

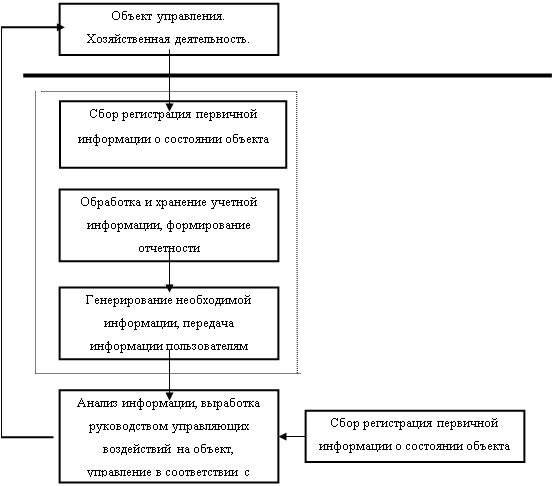

логическую среду для разработки больших экономических моделей. Система должна работать под управлением Windows95, реализована в среде разработки Borland Delphi 3 и должна состоять из двух компонентов - вычислительного ядра системы (engine) и оболочки над ним. Оболочка включает в себя: · Набор интерфейсов для всех типов процессов · База данных (БД), структура которой предполагает ...

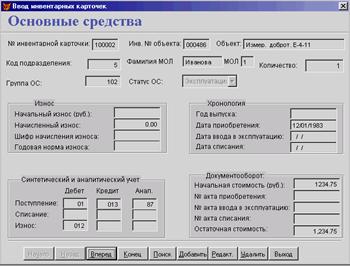

... достаточно нажать кнопку <Выход>. При входе в пункт меню «Просмотр» / «Основные фонды» на экране появляется реестр основных средств, выводится наиболее полный перечень полей базы данных OSl.dbf. Причем данные предоставлены только для просмотра. Для модификации данных служит пункт меню «Коррекция» / «Основные фонды». Чтобы отредактировать запись курсор подводят к нужной строке списка и ...

... ? 8. Какими программами можно воспользоваться для устранения проблем и ошибок, обнаруженных программой Sandra? Раздел 3. Автономная и комплексная проверка функционирования и диагностика СВТ, АПС и АПК Некоторые из достаточно интеллектуальных средств вычислительной техники, такие как принтеры, плоттеры, могут иметь режимы автономного тестировании. Так, автономный тест принтера запускается без ...

0 комментариев