Навигация

Используемые цифровые микросхемы и их параметры

4.2 Используемые цифровые микросхемы и их параметры

4.2.1 1533ИР34 - два четырехразрядных буферных регистра с третьем Z - состоянием. Каждый из регистров имеет четыре входа и четыре выхода, вход сброса R и выход разрешения вывода ЕО. Когда на вход разрешения записи РЕ подано напряжение высокого уровня, то данные со входов D проходят на выход Q, если на выводе действует низкий уровень напряжения, а на входе - высокий.

Таблица состояний

| Входы | Выход | |||

| РЕ | D | Q | ||

| 1 | х | х | x | Z |

| 0 | 0 | х | х | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | x | Q0 |

| 24 - питание 12 - общий Технические параметры: Рпот =150мВт t1.0зд.р. не более 22 нс t0.1зд.р. не более 15 нс |

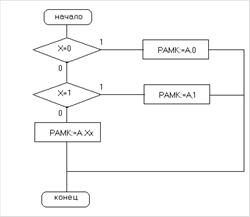

4.2.2 КР531ИД14 - два дешифратора-демультиплексора. Имеется два адресных входа А0 и А1. Если дешифратор работает в режиме демультиплексора, то вход разрешения ЕО принимает данные.

Таблица состояний

| Входы | Выходы | |||||

| А0 | А1 | |||||

| 0 | 0 | 0 | 0 | |||

| 1 | 0 | 0 | 1 | |||

| 0 | 1 | 0 | 0 | |||

| 1 | 1 | 0 | 1 | |||

| 0 | 0 | 1 | 0 | |||

| 1 | 0 | 1 | 1 | |||

| 0 | 1 | 1 | 0 | |||

| 1 | 1 | 1 | 1 | |||

| 16 - питание 8 - общий Технические параметры: Рпот =450мВт t1.0зд.р. не более 12 нс t0.1зд.р. не более 15 нс |

4.2.3 533ИМ6 - четырехразрядный полный двоичный сумматор с ускоренным переносом. Сумматор принимает два четырехразрядных слова по входам А0…А3 и В0…В3, а по входу Сn сигнал входного переноса. Сумма разрядов входных слов появляется на выходах S0…S1. На выходе Сn+1 выделяется сигнал выходного переноса. В состав сумматора входит схема ускоренного переноса.

| 16 - питание 8 - общий Технические параметры: Рпот =170мВт t1.0зд.р. не более 24 нс t0.1зд.р. не более 24 нс |

4.2.4 КР531КП11 - четыре одинаковых двухвходовых мультиплексора MSa…MSd, имеют вход - разрешение выходным данным. Каждый из четырех мультиплексоров имеет по два входа данных I1 и I2. Для их выбора служит вход адреса данных.

Таблица состояний

| Входы | Выход | |||

| S | I1 | I2 | Y | |

| 1 | x | x | x | Z |

| 0 | 0 | 0 | x | 0 |

| 0 | 0 | 1 | х | 1 |

| 0 | 1 | x | 0 | 0 |

| 0 | 1 | x | 1 | 1 |

| 16 - питание 8 - общий Технические параметры: Рпот =400мВт t1.0зд.р. не более 22 нс t0.1зд.р. не более 15 нс |

4.2.5 КР531КП2 - двойной четырехвходовый мультиплексор, имеющий общие адресные входы выбора S0 и S1. Имеются два входа разрешения и для каждого мультиплексора с активным низким уровнем напряжения.

Таблица состояний

| Входы | Выход | ||||||

| S0 | S1 | I1 | I2 | I3 | I4 | Y | |

| х | х | 1 | х | х | х | х | 0 |

| 0 | 0 | 0 | 0 | х | х | х | 0 |

| 0 | 0 | 0 | 0 | х | х | х | 1 |

| 1 | 0 | 0 | х | 0 | х | х | 0 |

| 1 | 0 | 0 | х | 1 | х | х | 1 |

| 0 | 1 | 0 | х | х | 0 | х | 0 |

| 0 | 1 | 0 | х | х | 1 | х | 1 |

| 1 | 1 | 0 | х | х | х | 0 | 0 |

| 1 | 1 | 0 | х | х | х | 1 | 1 |

| 16 - питание 8 - общий Технические параметры: Рпот =350мВт t1.0зд.р. не более 30 нс t0.1зд.р. не более 31 нс |

4.2.6 1533ИЕ7 - четырехразрядный реверсивный счетчик с предварительной записью. Установка счетчика в нулевое состояние осуществляется подачей на вход сброса R высокого уровня напряжения. Вход разрешения параллельной загрузки . Тактовые входы: для счета на увеличение CU и на уменьшение CD.

Таблица состояний

| Режим | Входы | Выходы | ||||||||||||

| R | CU | CD | D0 | D1 | D3 | D4 | Q1 | Q2 | Q3 | Q4 | ||||

| Сброс | 1 | х | х | 0 | х | х | х | х | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | х | х | 1 | х | х | х | х | 0 | 0 | 0 | 0 | 1 | 1 | |

| Парал. загрузка | 0 | 0 | х | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | х | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | |

| 0 | 0 | 0 | х | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 0 | 0 | 1 | х | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| Счет на увелич. | 0 | 1 | | 1 | х | х | х | х | Счет на увеличение | 1 | 1 | |||

| Счет на уменьш. | 0 | 1 | 1 | | х | х | х | х | Счет на уменьшение | 1 | 1 | |||

| 16 - питание 8 - общий Технические параметры: Рпот =120мВт t1.0зд.р. не более 42 нс t0.1зд.р. не более 38 нс |

4.2.7 КР531ИД7 - двоично-десятичный дешифратор-демультиплексор, преобразующий трехразрядный код А0…А7 в напряжение низкого уровня, появляющееся на одном из восьми выходов …. Дешифрация происходит тогда, когда на входах и действует напряжение низкого уровня, а на входе Е3 - высокого.

Таблица состояний

| Входы | Выходы | ||||||||||||

| Е3 | А0 | А1 | А2 | ||||||||||

| 0 | х | х | х | х | х | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| х | 1 | х | х | х | х | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| х | х | 0 | х | х | х | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 16 - питание 8 - общий Технические параметры: Рпот =370мВт t1.0зд.р. не более 12,5 нс t0.1зд.р. не более 9 нс |

4.2.8 К531КП7П - восьмиканальный мультиплексор. Имеет вход разрешения - активный уровень низкий, и три адресных входа, их активный уровень высокий.

Таблица состояний

| Входы | Выходы | ||||

| Выбор | Y | ||||

| S2 | S1 | S0 | |||

| x | x | x | 1 | 0 | 1 |

| 0 | 0 | 0 | 0 | I1 | |

| 0 | 0 | 1 | 0 | I2 | |

| 0 | 1 | 0 | 0 | I3 | |

| 0 | 1 | 1 | 0 | I4 | |

| 1 | 0 | 0 | 0 | I5 | |

| 1 | 0 | 1 | 0 | I6 | |

| 1 | 1 | 0 | 0 | I7 | |

| 1 | 1 | 1 | 0 | I8 | |

| 16 - питание 8 - общий Технические параметры: Рпот =350мВт t1.0зд.р. не более 18 нс t0.1зд.р. не более 18 нс |

4.2.9 К531ТМ2П - два независимых D-триггера, имеющих общую цепь питания. У каждого триггера имеется один информационный вход D, вход синхронизации С и два дополнительных инверсных входа S и R независимой асинхронной установки триггера в единичное и нулевое состояние.

Таблица состояний

| Режим работы | Входы | Выходы | ||||

| D | C | Q | ||||

| Асинхронная установка | 0 | 1 | х | х | 1 | 0 |

| Асинхронный сброс | 1 | 0 | х | х | 0 | 1 |

| Неопределенность | 0 | 0 | х | х | 1 | 1 |

| Загрузка 1 (установка) | 1 | 1 | 1 | | 1 | 0 |

| Загрузка 0 (сброс) | 1 | 1 | 0 | | 0 | 1 |

| 14 - питание 7 - общий Технические параметры: Рпот =250мВт t1.0зд.р. не более 12 нс (С) 6 нс (R,S) t0.1зд.р. не более 13.5 нс (С) 8 нс (R,S) |

4.2.10 КР1531ЛИ3 - три микросхемы И, каждая на три входа.

| 14 - питание 7 - общий Технические параметры: Рпот =13мВт t1.0зд.р. не более 5 нс t0.1зд.р. не более 5.5 нс |

4.2.11 КР1531ЛН1 - шесть инверторов.

| 14 - питание 7 - общий Технические параметры: Рпот =7,5мВт t1.0зд.р. не более 3,5 нс t0.1зд.р. не более 3,8 нс |

4.3 Техническое описание принципиальной электрической схемы РОН

Принципиальная схема определяет полный состав элементов и связей между ними и дает детальное представление о принципе работы РОН. Принципиальная схема построена на основе функциональной электрической схемы.

Микросхемы DD11-DD14, DD21-DD24, DD32-DD35, DD42-DD45, DD58-DD60, DD68-DD71, DD86-DD89, DD95-DD98 представляют собой регистры 1533ИР34 по два в корпусе. На их основе построены 8 32-х разрядных регистров общего назначения. Каждая из микросхем имеет вход обнуления, вход разрешения записи и вход разрешения выдачи на который всегда подан управляющий низкий уровень.

Микросхема DD1 представляет собой дешифратор КР531ИД7 с помощью которого выбирается один из РОН, а так как он имеет инверсные выходы, то к нему подключены инверторы - микросхемы DD2 и DD3, по шесть инверторов в одном корпусе (причем в DD3 используются только два).

С помощью микросхем DD25 и DD78 происходит управление записью в РОН. Эти микросхемы являются логическими элементами И на три входа по три в корпусе, причем в DD78 используются только два.

Записывается информация в РОН только по ШД0.

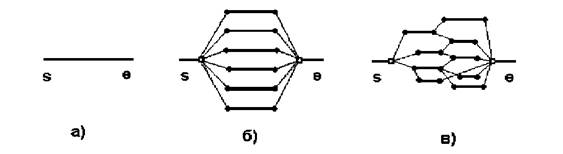

Вывод информации на шины ШД0 и ШД1 осуществляется с помощью мультиплексоров К531КП7. На ШД0 данные выводятся с помощью микросхем DD5-DD7, DD15-DD17, DD26-DD28, DD36-DD38, DD46-DD48, DD52-DD54, DD62-DD64, DD72-DD74, DD79-DD81, DD90-DD92, DD99-DD100. На ШД1 данные выводятся с помощью микросхем DD8-DD10, DD18-DD20, DD29-DD31, DD39-DD41, DD49-DD51, DD55-DD57, DD65-DD67, DD75-DD77, DD82-DD85, DD93-DD94, DD101-DD102. Инверсный выход данных микросхем не используется.

Схема питается напряжением 5В, которое подается на 14 выводы микросхем DD2-DD4, DD25, DD78, на 16 вывод микросхем DD1, DD5-DD10, DD15-DD20, DD26-DD31, DD36-DD41, DD46-DD57, DD62-DD67, DD72-DD77, DD79-DD85, DD90-DD94, DD99-DD102 и на 24 вывод микросхем DD11-DD14, DD21-DD24, DD32-DD35, DD42-DD45, DD58-DD61, DD68-DD71, DD86-DD89, DD95-DD98. Общий провод для микросхем DD2-DD4, DD25, DD78 является7, 8 вывод микросхем DD1, DD5-DD10, DD15-DD20, DD26-DD31, DD36-DD41, DD46-DD57, DD62-DD67, DD72-DD77, DD79-DD85, DD90-DD94, DD99-DD102 и 12 вывод микросхем DD11-DD14, DD21-DD24, DD32-DD35, DD42-DD45, DD58-DD61, DD68-DD71, DD86-DD89, DD95-DD98.

Первоначально все регистры устанавливаются в нулевое состояние. Данные выставленные на ШД0 для записи в регистры ждут появления не только прихода синхроимпульса, но и прихода сигнала РЕ, а также прихода сигнала от дешифратора выбора определенного регистра. Для вывода данных на ШД0 мультиплексоры, работающие с этой шиной ждут управления адресными входами, для выбора определенного регистра, а также управляющего сигнала на вход , разрешающего вывод информации на шину данных. Аналогичным образом происходит выдача на ШД1.

На принципиальной схеме присутствуют конденсаторы, предназначенные для подавления помех по цепи питания.

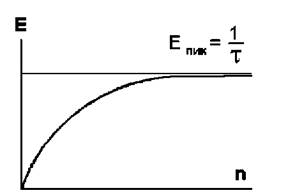

Эффективным средством защиты интегральных схем от помех по цепи питания является включение конденсаторов развязки между шинами питания и общей. Обычно конденсаторы развязки устанавливаются отдельно для блокирования низкочастотных и высокочастотных помех.

Низкочастотные помехи, проникающие в систему по цепи питания, должны блокироваться с помощью электролитического конденсатора C1-С10 емкостью 1мкФ. Взят конденсатор К50-6-120%.

Для исключения высокочастотных помех развязывающие емкости взяты номиналом 0,015мкФ на одну микросхему. Следовательно для нашего случая взяты десять емкостей С11 - С20. Взят конденсатор КМ-5-Н90-0,01520%.

Для данной схемы приведен перечень элементов.

Похожие работы

... плавающей запятой за два обращения к регистровой памяти, а конвейерный способ связи с ней позволил производить это считывание за три машинных такта. 1. Функциональная организация процессора Процессор должен выполнять следующие команды: И непосредственное Сложение с нормализацией Загрузка и проверка Загрузка PSW 1.1 Описание команды “И непосредственное " NI D1 (B1), I2 (SI) ...

... архитектурно-технические решения, используемые в настоящее время при создании микропроцессоров. Современные процессоры INTEL Компания Intel является одной из передовых в производстве современных микропроцессоров. Компанию основали Роберт Нойс и Гордон Мур в 1968 году Intel переводится с английского «интегральная электроника». Бизнес-план компании был распечатан на печатной машинке Робертом ...

... 1) той или иной модели системной платы зависит от производителя и определяется типом платформы ПК (типом центрального процессора), применяемым набором микросхем chipset и количеством и разрядностью периферийных устройств, подключаемых к данной системной плате. Максимальная пропускная способность часто используется в качестве критерия для сравнения возможностей шин различной архитектуры. Ее можно ...

... 5k управления ресурсами (программно-аппаратный комплекс) массивно-параллельного компьютера обязана обрабатывать подобные ситуации в обход катастрофического общего рестарта с потерей контекста исполняющихся в данный момент задач. 2.4.1 Массивно-параллельные суперкомпьютеры серии CRY T3 Основанная в 1972 году фирма Cry Research Inc. (сейчас Cry Inc.), прославившаяся разработкой векторного ...

0 комментариев