Навигация

2. Класс

D = B1 + B2 + B3

При этом

Объединим классы k3, k4, k5, k7 в класс k8. Для этого обобщенный оператор примет вид:

Класс :

D = B1 + B2

Класс :

D = B1

Построим структурные схемы узлов, реализующих обобщенные операторы:

Класс:

Класс :

Класс:

На основании полученных выше данных построим обобщенную схему операционного автомата. (Рис. 5).

Рис. 5. Обобщенная схема операционного автомата.

1.4 Разработка управляющих автоматов для процессорных элементов микро ЭВМ.

При синтезе управляющего автомата условимся о следующих допущениях – комбинаторный сумматор, использованный при синтезе операционного автомата формирует следующие признаки:

P – знак числа

Число больше нуля – P = “0”

Число меньше нуля – P = “1”

Z – признак нуля

Число равно нулю – Z = “1”

Число не равно нулю – Z = “0”

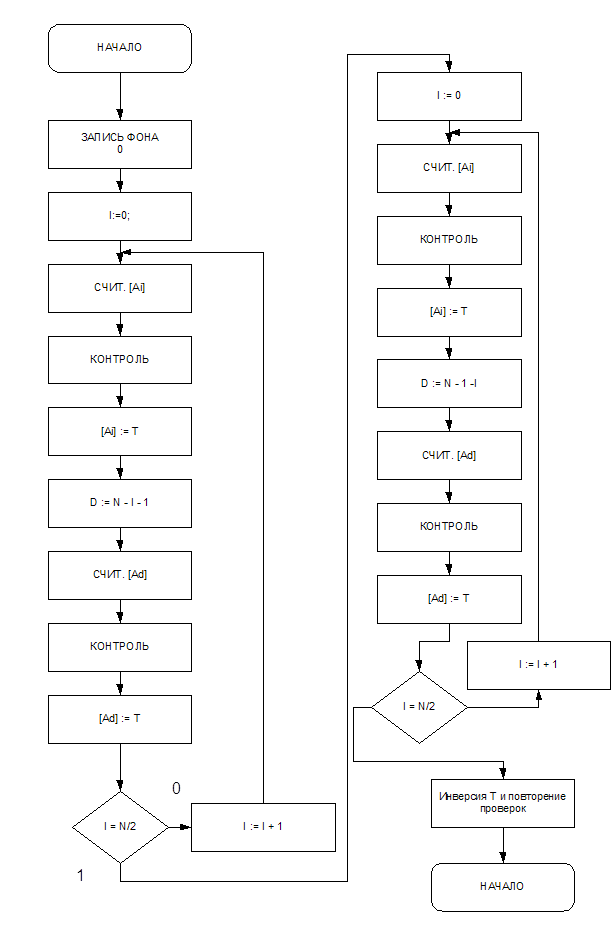

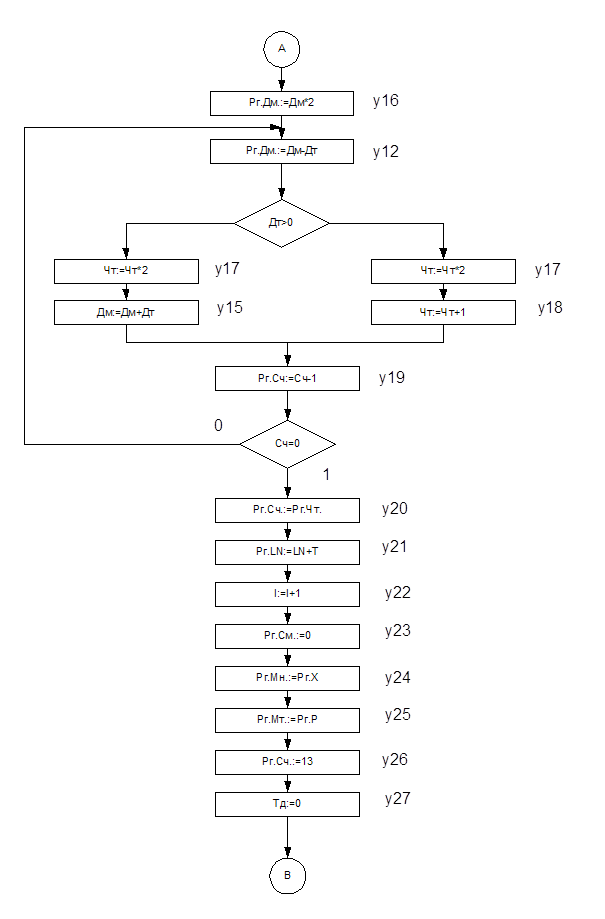

Для построения управляющего автомата произведем разметку ГСА (Рис. 6).

Рис. 6.1 Схема разметки ГСА.

Рис. 6.2 Схема разметки ГСА.

Рис. 6.3 Схема разметки ГСА.

| 000000 | 000001 | 1 | - | - | ||

| 000001 | 000010 | 1 | D5 | |||

| 000010 | 000011 | 1 | D5 D6 | |||

| 000011 | 000100 | 1 | D4 | |||

| 000100 | 000101 | 1 | D4 D6 | |||

| 000101 | 000110 | 1 | D4 D5 | |||

| 000110 | 000111 | 1 | D4 D5 D6 | |||

| 000111 | 001000 | 1 | D3 | |||

| 001000 | 001001 | 1 | D3 D6 | |||

| 001001 | 001010 | 1 | D3 D5 | |||

| 001010 | 001011 | 1 | D3 D5 D6 | |||

| 001011 | 001100 | 1 | D3 D4 | |||

| 001100 | 001101 | D3 D4 D6 | ||||

| 001110 | D3 D4 D5 | |||||

| 001101 | 001111 | 1 | D3 D4 D5 D6 | |||

| 001110 | 001111 | 1 | D3 D4 D5 D6 | |||

| 001111 | 010000 | 1 | D2 | |||

| 010000 | 010001 | 1 | D2 D6 | |||

| 010001 | 010011 | D2 D5 D6 | ||||

| 010010 | D2 D5 | |||||

| 010010 | 010100 | 1 | D2 D4 | |||

| 010011 | 010101 | 1 | D2 D4 D6 | |||

| 010100 | 010110 | 1 | D2 D4 D5 | |||

| 010101 | 010110 | 1 | D2 D4 D5 D6 | |||

| 010110 | 010111 | D2 | ||||

| 010000 | ||||||

| 010111 | 011000 | 1 | D2 D3 | |||

| 011000 | 011001 | 1 | D2 D3 D6 | |||

| 011001 | 011010 | 1 | D2 D3 D5 D6 | |||

| 011010 | 011011 | 1 | D2 D3 D4 | |||

| 011011 | 011100 | 1 | D2 D3 D4 D6 | |||

| 011100 | 011101 | 1 | D2 D3 D4 D5 | |||

| 011101 | 011110 | 1 | D2 D3 D4 D5 D6 | |||

| 011110 | 011111 | D1 | ||||

| 100000 | D1 D6 | |||||

| 100001 | D1 D5 D6 | |||||

| 100011 | D1 D5 | |||||

| 100010 | D1 D5 | |||||

| 011111 | 100010 | 1 | D1 D5 | |||

| 100000 | 100010 | 1 | D1 D5 | |||

| 100001 | 100011 | 1 | D1 D5 D6 | |||

| 100010 | 100110 | 1 | D1 D4 D5 | |||

| 100011 | 100110 | 1 | D1 D4 D5 | |||

| 100100 | 011110 | 1 | D2 D3 D4 D5 | |||

| 100101 | 100100 | 1 | D1 D4 | |||

| 100110 | 100101 | D1 D4 D6 | ||||

| 100111 | D1 D4 D5 D6 | |||||

| 100111 | 101000 | 1 | D1 D3 | |||

| 101000 | 101001 | 1 | D1 D3 D6 | |||

| 101001 | 000000 | - | ||||

| 001000 | D3 |

Обобщая полученные данные можно построить общую схему управляющего автомата (Рис. 7).

Рис. 7. Общая схема управляющего автомата.

2. Разработка структурной схемы микро ЭВМ. 2.1 Эмуляция ОА в микропроцессорной среде с разрядно-модульной организацией.

Для достижения требуемой разрядности при использовании микропроцессорной секции К1804ВС1 необходимо объединить между собой шесть микропроцессорных секций. Функциональная схема объединения МПС приведена на рис. 8.

При эмуляции ОА в микропроцессорной среде будем использовать следующие соглашения:

| Номер РОН | Регистр в ОА |

| 1 | Рг.I |

| 2 | Рг.T |

| 3 | Рг.К |

| 4 | Рг.Х |

| 5 | Рг.Р |

| 6 | Рг.Чт. |

| 7 | Рг.Дт. |

| 8 | Рг.Сч. |

| 9 | Рг.Мн. |

| 10 | Рг.Мт. |

| 11 | Рг.LN |

| 12 | Рг.DM |

| 13 | Рг.СМ. |

Рис.8 Функциональная схема объединения МПС.

Сигналы, поступающие на МПС:

А(4 разр.), В(4), I(9), D(24), (1)

Для реализации микроопераций ОА необходимо подать на МПС следующие наборы сигналов (в соответствии с форматом):

| : | 0000 | 0001 | 010 | 000111 | 00..00 | 1 |

| : | 0000 | 0010 | 010 | 000111 | 00..00 | 0 |

| : | 0000 | 1011 | 010 | 000111 | 00..00 | 0 |

| : | 0000 | 0011 | 010 | 000111 | 00..00 | 0 |

| : | 0000 | 0100 | 010 | 000111 | X | 0 |

| : | 0100 | 0100 | 010 | 001100 | 00..00 | 0 |

| : | 0100 | 0101 | 010 | 000100 | 00..00 | 0 |

| : | 0000 | 0110 | 010 | 000111 | 00..00 | 0 |

| : | 0001 | 0111 | 010 | 000100 | 00..00 | 0 |

| : | 0100 | 1100 | 010 | 000100 | 00..00 | 0 |

| : | 0000 | 1000 | 010 | 000111 | 00..0010111 | 0 |

| : | 0111 | 1100 | 010 | 001001 | 00..00 | 1 |

| : | 0000 | 1110 | 010 | 000111 | 00..00 | 1 |

| : | 0000 | 1110 | 010 | 000111 | 00..00 | 0 |

| : | 0111 | 1100 | 011 | 000001 | 00..00 | 0 |

| : | 0000 | 1100 | 110 | 000011 | 00..00 | 0 |

| : | 0000 | 0110 | 110 | 000011 | 00..00 | 0 |

| : | 0000 | 0110 | 010 | 000011 | 00..00 | 1 |

| : | 0000 | 1000 | 010 | 001011 | 00..00 | 0 |

| : | 0110 | 0010 | 010 | 000100 | 00..00 | 0 |

| : | 0010 | 1011 | 010 | 000001 | 00..00 | 0 |

| : | 0000 | 0001 | 010 | 000011 | 00..00 | 1 |

| : | 0000 | 1101 | 010 | 000111 | 00..00 | 0 |

| : | 0100 | 1001 | 010 | 000100 | 00..00 | 0 |

| : | 0101 | 1010 | 010 | 000100 | 00..00 | 0 |

| : | 0000 | 1000 | 010 | 000111 | 00..01101 | 0 |

| : | 0000 | 1111 | 010 | 000111 | 00..00 | 0 |

| : | 1001 | 1101 | 010 | 000001 | 00..00 | 0 |

| : | 1001 | 0000 | 110 | 000100 | 00..00 | 0 |

| 0000 | 1101 | 010 | 000001 | 00..00 | 0 | |

| : | 1001 | 1101 | 010 | 001001 | 00..00 | 1 |

| : | 0000 | 1111 | 010 | 000111 | 00..00 | 1 |

| : | 0000 | 1010 | 100 | 000011 | 00..00 | 0 |

| 0000 | 1010 | 100 | 000011 | 00..00 | 0 | |

| : | 0000 | 1001 | 110 | 000001 | 00..00 | 0 |

| : | 1101 | 0100 | 010 | 000100 | 00..00 | 0 |

| : | 0000 | 0100 | 010 | 010011 | 00..00 | 1 |

| : | 0000 | 0011 | 010 | 001011 | 00..00 | 0 |

В микро ЭВМ функции управляющего автомата реализует блок микропроцессорного управления. Структурная схема БМУ представлена на рис. 9.

Рис. 9. Структурная схема БМУ.

Принципом организации корректного функционирования микро ЭВМ является факт того, что при выполнении определенных команд, выполняется некоторая совокупность микроопераций в тело которым выходит весь набор управляющих сигналов для выполнения определенных действий.

Таким образом, для каждой команды (микрооперации) существует некоторый набор микроопераций, содержащих в своем теле все необходимые управляющие сигналы, последовательное выполнение которых приводит к выполнению команды в целом.

Данная система реализации команд получила название принципа микропрограммной реализации команд и достаточно широко используется при реализации конкретных вычислительных устройств благодаря своей гибкости и производительности.

2.3 Проектирование УУ микро ЭВМ. 2.3.1 Процесс взаимодействия центральной и периферийной ЭВМ.Очевидно, что разработанная микро ЭВМ является специализированной и не стоит на вершине цепочки управления, а потому необходимо иметь алгоритмы и средства, осуществляющие управление данной микро ЭВМ.

С учетом назначения разрабатываемого устройства (сбор и обработка информации), процесс взаимодействия центральной и периферийной ЭВМ можно обеспечить следующим образом: при поступлении запроса на прерывание от центральной ЭВМ, программа-обработчик данного прерывания производит опрос портов ввода-вывода данного прерывания и, в соответствии с алгоритмом вычисления заданной арифметической функции (ln x), производит обработку полученных данных. После этого периферийная ЭВМ инициирует запрос на прямой доступ к памяти и по каналу ПДП пересылает полученные в результате расчетов данные в ОЗУ центральной ЭВМ, после чего продолжает выполнение прерванной программы.

Таким образом, алгоритм взаимодействия ПЭВМ и ЦЭВМ можно отобразить следующей обобщенной блок-схемой, представленной на рис. 10.

Рис. 10. Алгоритм взаимодействия ПЭВМ и ЦЭВМ.

2.3.2 Устройство управления микро ЭВМ.При функционировании микро ЭВМ, в частности при выполнении определенной программы возникает вопрос о времени выполнения определенных микроопераций. Это связано с тем, что некоторые операции выполняются быстрее, другие – медленнее. Поэтому встает вопрос о методах синхронизации некоторых блоков микро ЭВМ для избежания сбоев и ложных срабатываний. Очевидным и наименее сложным является метод тактирования элементов ЭВМ тактами, длительность которых больше максимального времени выполнения микроопераций. Однако из-за неэффективности данного способа (возможно значительное время простоя микро ЭВМ) применение этого метода оказывается неэффективным.

Для построения более эффективных вычислительных устройств может использован следующий метод: предлагается ввести в состав схемы микро ЭВМ схему управления длительностью такта. Структурная схема такого решения может быть представлена как показано на рис. 11.

Рис.11. Структурная схема схемы управления длительностью такта.

В этом случае в Рг.Мк. выделяется определенное поле, которое и определяет время выполнения микрокоманды.

Чтобы избежать излишней громоздкости схемы управления длительностью такта при большом количестве команд с различным временем исполнения, имеет смысл разбить их на группы и применять к каждой группе первый алгоритм.

3. Проектирование структуры микро ЭВМ. 3.1 Проектирование памяти микро ЭВМ. 3.1.1 Проектирование локальной памяти процессорного элемента.

В локальной памяти процессорного элемента хранится микропрограммная интерпретация команд (микрокоманд) компьютера. Очевидно, что количество микросхем модулей памяти определяется двумя факторами:

- разрядностью ПЗУ;

- разрядностью регистра микрокоманд.

-

С учетом заданной микросхемы (556РТ14), функциональную схему локальной памяти процессорного элемента можно представить, как показано на рис. 12.

Адрес с выхода СУАМ поступает на адресные входы блока ПЗУ, и на выходных шинах микросхем появляется микрокоманда, поступающая в Рг.Мк.

Рис. 12. Функциональная схема локальной памяти процессорного элемента

3.1.2 Проектирование системы ПЗУ и ОЗУ.

Очевидно, что прикладные программы и другое служебное программное обеспечение находится в оперативном запоминающем устройстве, причем необходимо часть памяти организовать на ПЗУ. В этом случае в нем можно разместить наиболее часто используемые программы, например тест памяти и программу для расчета заданной арифметической операции. С учетом того, что данная микро ЭВМ является специализированной, в ПЗУ можно разместить и обработчики прерываний, которые могут произойти от внешних устройств (портов) центральной ЭВМ или устройства управления.

Обобщенную структурную схему ОЗУ можно представить как показано на рис. 13. Подробная принципиальная схема приведена в приложении 1.

3.1.3 Разработка системы адресации.В разрабатываемой микро ЭВМ поддерживаются следующие методы адресации:

- прямая;

- непосредственная;

- автоинкрементная;

- относительная.

Для поддержки перечисленных методов адресации в структуре микро ЭВМ предусмотрен ряд аппаратной поддержки (наличие дополнительных управляющих регистров).

Рассмотрим данные методы адресации и их аппаратную поддержку более подробно.

1. Прямая адресация.

При считывании команды из памяти в регистр команд вместе с кодом операции попадает адрес первого операнда в выполняемом действии, который может быть передан в блок обработки данных через регистр Рг.ADR. (при наличии соответствующих управляющих сигналов в Рг.Мк.), второй адрес операнда необходимо получить считав в регистр входных данных следующее слово команды из памяти.

2. Непосредственная.

При данном способе адресации в теле команды присутствует сам операнд. Таким образом в регистр команд попадает только код операции, а параметр считывается на следующем такте в регистр входных данных. При реализации данного метода адресации дополнительного аппаратного оборудования не требуется.

Похожие работы

... регистра вправо) shl Reg (сдвиг регистра влево) and Reg, операнд and Reg (Reg с аккумулятором) or Reg (аккумулятор с Reg) xor Reg (аккумулятор с Reg) 1.2 Разработка обобщённой структуры микро ЭВМ на основе алгоритмов решения задач. С учётом вышеизложенных алгоритмов обобщённую структуру микро ЭВМ можно представить следующим образом (рис. 3.). Рис. 3. Обобщённая структура микро ЭВМ. ...

... напряжения. У ЦАП с токовым выходом этот параметр в большой степени зависит от типа выходного ОУ. Виды ЦАП Существуют последовательные и параллельные ЦАП. Последовательные –- используются в микропроцессорных системах, если не требуется высокое быстродействие. Среди параллельных - наиболее просты ЦАП с суммированием весовых токов Большинство схем параллельных ЦАП основано на суммировании ...

0 комментариев