Навигация

Вариант практической реализации тестера – объект моделирования

2.3. Вариант практической реализации тестера – объект моделирования

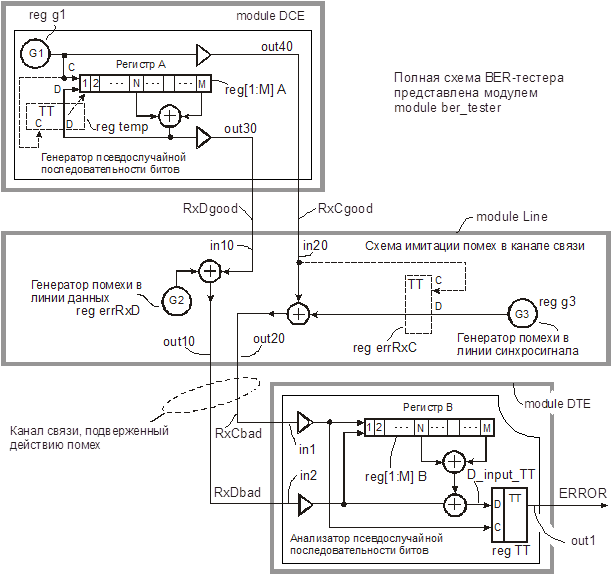

Как показано на рис. 2.3, для тестирования цепей передачи синхросигналов RxC и данных RхD

канала связи между устройствами DTE и DCE использованы генератор и анализатор псевдослучайных последовательностей битов. По существу, генератор и анализатор представляют собой рассмотренные ранее скремблер и дескремблер, причем скремблируется сигнал “Постоянный нуль”, т. е. последовательность нулевых битов

(SD = 0, см. рис. 2.2). В отсутствие ошибок передачи сигналов RxC и RxD сигнал на выходе триггера TT также должен быть нулевым.

Для имитации помех в канале связи использованы генераторы G2 и G3. Генератор G2 в определенном такте (тактах) формирует сигнал лог. 1. Этот сигнал воздействует на логический элемент Исключающее ИЛИ, в результате элемент временно переводится в режим инвертирования передаваемого через него бита (битов) данных. Таким образом, вместо истинного нулевого бита передается ложный единичный или наоборот. Для имитации канала связи без помех в линии передачи данных на выходе генератора G2 должен постоянно присутствовать сигнал лог. 0.

Аналогично имитируется сигнал помехи, действующей на линию передачи синхросигнала. В отсутствие помех на выходе генератора G3 постоянно присутствует сигнал лог. 0. Появление в некотором такте на выходе генератора G3 сигнала лог. 1 приводит к временному искажению синхросетки передаваемых данных, так как при этом теряется один синхроимпульс.

Рис. 2.3. Система контроля передачи данных и синхросигнала между устройствами типа DCE и DTE

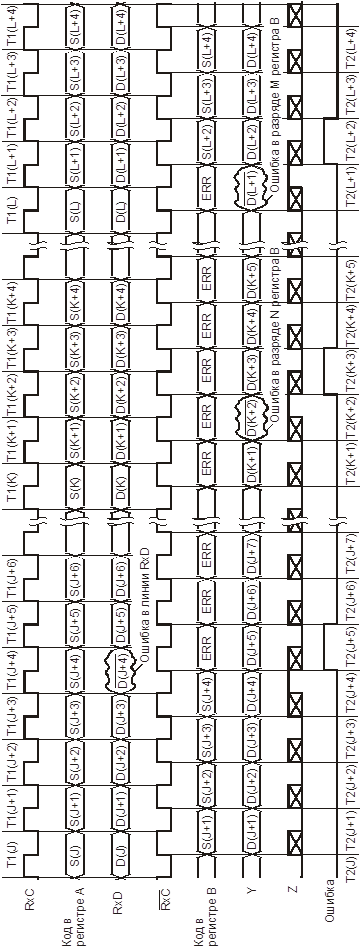

В отсутствие ошибок под управлением сигнала RxC с генератора G1 в линию данных RxD из регистра

А поступает псевдослучайная последовательность битов (см.

рис. 2.4). Положительные фронты сигнала RxC задают границы битовых интервалов сигнала RxD. Положительные фронты инвертированного сигнала RxC задают смещенную на половину такта синхросетку приема данных в регистр В и в D-триггер ТТ. Такты работы генератора псевдослучайной последовательности битов обозначены символами Т1 с соответствующими индексами в скобках (например Т1(L + 4)). Аналогично такты работы анализатора обозначены символами Т2.

В тактах T1(J) … T1(J + 3) состояние регистра А изменяется в такой последовательности: S(J), S(J + 1), S(J + 2), S(J + 3). Соответствующие биты выходных данных: D(J), D(J + 1), D(J + 2), D(J + 3). Как отмечалось при описании системы “скремблер – дескремблер”, в установившемся режиме при отсутствии ошибок содержимое передающего и приемного регистров (в данном случае, регистров А и В) одинаково. Поэтому, как показано на временных диаграммах, коды в регистре В совпадают с кодами в регистре А с учетом взаимного смещения синхросеток на половину такта.

| Рис. 2.4. Временные диаграммы передачи и приема тестовых битовых последовательностей |

Интересно отметить, что код в приемном регистре (В) формируется на половину такта раньше, чем тот же код в передающем регистре (А)! Такое поведение анализатора можно рассматривать как предсказание очередного правильного бита (0 или 1) в ожидании его поступления по линии RxD. Как следует из временных диаграмм, в отсутствие ошибок предсказания полностью оправдываются. Это проявляется в том, что сигнал Z на входе данных D-триггера принимает устойчивое нулевое значение в моменты записи, поэтому триггер остается в состоянии лог. 0.

Предположим, что в такте Т1(J + 4) в результате воздействия на линию RxD импульса помехи передаваемый бит исказился: вместо истинного лог. 0 передается ложная лог. 1 или наоборот. В этой ситуации во второй половине такта Т2(J + 4) обнаруживается несоответствие предсказанного и фактически принятого битов (сигнал Z принимает стабильное значение, равное лог. 1). Поэтому в следующем такте Т2(J + 5) триггер переходит в состояние лог. 1. Таким образом, первое проявление ошибки зафиксировано с задержкой в половину такта после ее возникновения в линии.

Начиная с такта Т1(J + 5) по линии RxD вновь передаются правильные биты. Сравнение предсказанных и фактически принятых битов вновь дают положительные результаты, но ранее принятый в регистр В ошибочный бит начинает продвижение к разряду N. Код в регистре В искажен (что отражено на диаграмме символами “ERR”), но искажения пока внешне не проявляются.

В такте Т2(К + 2) ошибочный бит попадает в разряд N. Вследствие этого происходит неправильное предсказание ожидаемого бита, т. е. во второй половине такта предсказанный бит Y противоположен правильному биту D(K + 2), полученному по линии RxD. Поэтому триггер повторно регистрирует ошибку. После этого ошибочный бит продолжает продвижение по регистру В в направлении разряда М. В такте T2(L + 1) ошибочный бит достигает разряда М. Неправильное предсказание повторяется, триггер в третий раз регистрирует ошибку. После этого ошибочный бит выталкивается из сдвигового регистра В и, следовательно, более не влияет на работу системы контроля. Таким образом, одиночная ошибка в линии приводит к формированию пачки из трех импульсов на выходе триггера.

3. Формулировка задания

3.1. Изучите работу схемы, приведенной на рис. 2.3.

3.2. Изучите предложенную Вам версию системы моделирования.

3.3. Разработайте модель схемы, приведенной на рис. 2.3. Параметры схемы определяются вариантом задания в соответствии с табл. 3.1. Моделирование выполняется на уровне gate level.

3.4. Протестируйте модель в условиях выключенных и включенных генераторов помех. Число и положение импульсов помех определяются вариантом задания в соответствии с табл. 3.1. Глубина тестирования – 1000 тактов. Начальное состояние регистра А – произвольное, но не нулевое.

3.5. Распечатайте временные диаграммы сигналов на начальном этапе работы системы передачи данных (в течение первых 20 – 40 тактов). Убедитесь в правильности этих диаграмм.

3.6. Распечатайте временные диаграммы сигналов на этапе обработки импульсов помех (вплоть до выхода ошибочного бита за пределы регистра В с запасом в несколько тактов). Убедитесь в правильности этих диаграмм.

3.7. Подготовьте пояснительную записку и файлы моделей в двух вариантах: электронном (помещается в архив локальной сети кафедры ТКС) и обычном – в виде распечатки.

В табл. 3.1. приняты следующие обозначения:

№ п/п – порядковый номер варианта курсового проекта;

М – разрядность регистра А(В), см. рис. 2.1;

N – номер разряда, к которому подключается цепь обратной связи, см. рис. 2.1;

T(DATA) – номера тактов, считая от нулевого, в которых генерируется помеха в линии передачи данных, см. рис. 2.3;

T(SYNC) – номера тактов, считая от нулевого, в которых генерируется помеха в линии передачи синхросигнала, см. рис. 2.3.

Таблица 3.1.

Параметры моделирования системы передачи данных

| № п/п | М | N | T(DATA) | T(SYNC) |

| 1 | 39 | 35 | 756, 759 | 759, 989 |

| 2 | 36 | 25 | 41, 126 | 41, 42, 43,44 |

| 3 | 35 | 33 | 88, 89, 90 | 860 –867 |

| 4 | 33 | 20 | 903–915 | 34, 44, 54 |

| 5 | 31 | 28 | 56, 65 – 69 | 68, 895 |

| 6 | 29 | 27 | 55, 57, 59, 67 | 757 – 763 |

| 7 | 28 | 25 | 85, 847 | 85, 88, 93 |

| 8 | 25 | 22 | 49 – 54 | 51 – 56, 129 |

| 9 | 7 | 6 | 47, 61 | 84, 99 – 105 |

| 10 | 9 | 5 | 55, 78, 88 | 80, 90 |

| 11 | 10 | 7 | 759, 989 | 55, 57, 59, 67 |

| 12 | 11 | 9 | 41, 42, 43,44 | 85, 847 |

| 13 | 15 | 14 | 860 –867 | 49 – 54 |

| 14 | 17 | 14 | 34, 44, 54 | 47, 61 |

| 15 | 18 | 11 | 68, 895 | 55, 78, 88 |

| 16 | 20 | 17 | 757 – 763 | 85, 847 |

| 17 | 21 | 19 | 759, 989 | 49 – 54 |

| 18 | 22 | 21 | 41, 42, 43,44 | 47, 61 |

| 19 | 23 | 18 | 860 –867 | 55, 78, 88 |

| 20 | 36 | 25 | 34, 44, 54 | 759, 989 |

| 21 | 35 | 33 | 68, 895 | 41, 42, 43,44 |

| 22 | 33 | 20 | 757 – 763 | 860 –867 |

| 23 | 31 | 28 | 85, 88, 93 | 34, 44, 54 |

| 24 | 21 | 19 | 51 – 56, 129 | 68, 895 |

| 25 | 22 | 21 | 41, 42, 43,44 | 757 – 763 |

| 26 | 23 | 18 | 860 –867 | 85, 88, 93 |

| 27 | 36 | 25 | 34, 44, 54 | 51 – 56, 129 |

| 28 | 35 | 33 | 759, 989 | 756, 759 |

| 29 | 31 | 28 | 41, 42, 43,44 | 41, 126 |

| 30 | 29 | 27 | 860 –867 | 88, 89, 90 |

| 31 | 28 | 25 | 34, 44, 54 | 903–915 |

| 32 | 25 | 22 | 68, 895 | 56, 65 – 69 |

| 33 | 7 | 6 | 757 – 763 | 55, 57, 59, 67 |

| 34 | 9 | 5 | 85, 88, 93 | 85, 847 |

| 35 | 10 | 7 | 51 – 56, 129 | 49 – 54 |

| 36 | 11 | 9 | 84, 99 – 105 | 47, 61 |

| 37 | 15 | 14 | 80, 90 | 55, 78, 88 |

| 38 | 25 | 22 | 55, 57, 59, 67 | 759, 989 |

| 39 | 7 | 6 | 85, 847 | 41, 42, 43,44 |

| 40 | 9 | 5 | 49 – 54 | 860 –867 |

| 41 | 10 | 7 | 47, 61 | 34, 44, 54 |

| 42 | 11 | 9 | 55, 78, 88 | 68, 895 |

| 43 | 15 | 14 | 85, 847 | 757 – 763 |

| 44 | 17 | 14 | 49 – 54 | 759, 989 |

| 45 | 18 | 11 | 47, 61 | 41, 42, 43,44 |

| 46 | 25 | 22 | 55, 78, 88 | 860 –867 |

| 47 | 7 | 6 | 759, 989 | 34, 44, 54 |

| 48 | 9 | 5 | 41, 42, 43,44 | 68, 895 |

| 49 | 10 | 7 | 860 –867 | 757 – 763 |

| 50 | 11 | 9 | 34, 44, 54 | 85, 88, 93 |

| 51 | 15 | 14 | 68, 895 | 51 – 56, 129 |

| 52 | 17 | 14 | 757 – 763 | 41, 42, 43,44 |

| 53 | 18 | 11 | 85, 88, 93 | 860 –867 |

| 54 | 28 | 25 | 51 – 56, 129 | 34, 44, 54 |

| 55 | 25 | 22 | 41, 42, 43,44 | 759, 989 |

| 56 | 7 | 6 | 860 –867 | 41, 42, 43,44 |

| 57 | 9 | 5 | 34, 44, 54 | 860 –867 |

| 58 | 10 | 7 | 68, 895 | 34, 44, 54 |

| 59 | 11 | 9 | 34, 44, 54 | 35, 46, 56 |

| 60 | 15 | 14 | 759, 989 | 68, 895 |

| 61 | 17 | 14 | 41, 42, 43,44 | 757 – 763 |

| 62 | 18 | 11 | 860 –867 | 85, 88, 93 |

| 63 | 20 | 17 | 34, 44, 54 | 51 – 56, 129 |

| 64 | 21 | 19 | 68, 895 | 41, 42, 43,44 |

| 65 | 22 | 21 | 757 – 763 | 860 –867 |

| 66 | 23 | 18 | 85, 88, 93 | 34, 44, 54 |

| 67 | 36 | 25 | 51 – 56, 129 | 759, 989 |

| 68 | 35 | 33 | 84, 99 – 105 | 34, 44, 54 |

| 69 | 33 | 20 | 80, 90 | 68, 895 |

| 70 | 31 | 28 | 55, 57, 59, 67 | 757 – 763 |

| 71 | 21 | 19 | 85, 847 | 85, 88, 93 |

| 72 | 22 | 21 | 49 – 54 | 51 – 56, 129 |

| 73 | 23 | 18 | 85, 88, 93 | 41, 42, 43,44 |

| 74 | 36 | 25 | 51 – 56, 129 | 860 –867 |

| 75 | 35 | 33 | 41, 42, 43,44 | 34, 44, 54 |

| 76 | 31 | 28 | 860 –867 | 68, 895 |

| 77 | 29 | 27 | 34, 44, 54 | 34, 44, 54 |

| 78 | 28 | 25 | 759, 989 | 759, 989 |

| 79 | 25 | 22 | 34, 44, 54 | 41, 42, 43,44 |

| 80 | 7 | 6 | 68, 895 | 860 –867 |

4. Рекомендации по построению модели

4.1. Подготовка схемы к моделированию

Прежде чем начать моделирование схемы, следует представить ее в терминах системы Verilog HDL. Для этого нужно выделить в схеме функционально-законченные модули

(module), обозначить регистры (reg), провода (wire), входы, выходы (input, output) и т. п.

На рис. 4.1 представлен результат подготовки рассмотренной ранее схемы (см.

рис. 2.3) к моделированию. Отметим, что для упрощения примера в явном виде моделируются не все элементы схемы, а только ее регистры. Это означает, что вместо требуемого в техническом задании gate-уровня проектирования применен более высокий RTL-уровень (Register Transfer Level). В результате, например, вместо обозначения в явном виде элементов Исключающее ИЛИ в модели использованы их “формульные” эквиваленты. Это несколько увеличивает дистанцию между моделью и ее реальным прототипом, так как формульный эквивалент не учитывает задержку срабатывания соответствующего логического элемента или группы элементов. В примере нет также явных моделей усилителей, инвертора, триггера. Поэтому в Вашем курсовом проекте следует разработать более подробную модель, в полной мере соответствующую gate-уровню.

Схема (рис. 4.1) представлена четырьмя модулями. Первый модуль (module ber_tester) описывает структуру устройства в целом. Остальные модули (module DCE, module Line, module DTE) описывают структуру соответствующих составных частей устройства. Для удобства составления модели введены два “фиктивных” D-триггера (показаны на рисунке штриховыми линиями), хотя возможны и иные решения.

Далее приведены примеры реализации четырех упомянутых модулей. Каждый из них традиционно оформлен в виде отдельного файла. При компоновке проекта эти файлы собираются в одну группу и “исполняются” после выполнения Вами цепи команд экранного меню: Project à New à <имя нового проекта> à Add (добавить в проект четыре файла – описания четырех модулей) à OK à GO (провести моделирование)). При успешном выполнении моделирования следует вывести на экран временные диаграммы, желательно в такой же последовательности, как на рис. 4.2, а именно:

timing – пронумерованная в десятичном виде последовательность тактов, т. е. перио дов сигнала от генератора G1 (рис. 4.1);

RxCgood – синхросигнал без ошибок;

RxDgood, – данные без ошибок;

A[1:M] – шестнадцатиричный код в М-разрядном регистре А;

errRxC – импульс (импульсы) ошибок сигнала RxC;

errRxD – импульс (импульсы) ошибок сигнала RxD;

RxCbad – синхросигнал с ошибкой (ошибками);

RxDbad – данные с ошибкой (ошибками);

B[1:M] – шестнадцатиричный код в М-разрядном регистре В;

D_input_TT – сигнал на входе D-триггера модуля DTE;

ERROR – выходной сигнал (Ошибка) BER-тестера.

Рис. 4.1. Схема BER-тестера с обозначениями в терминах системы Verilog HDL для моделирования на уровне RTL

4.2. Пример построения RTL-модели BER-тестера на языке системы Verilog HDL

4.2.1. Файл BER-main_module.v

//Главный модуль (верхний уровень иерархии модулей)

module ber_tester (ERROR); // ber_tester - наименование модуля,

// в скобках заключен перечень выходов

// и входов (входов нет, имеется один выход)

output ERROR; // дается определение ERROR как выхода (а не входа)

wire RxDgood, RxCgood, RxDbad, RxCbad; // список проводов главного модуля

DTE DTE1(ERROR, RxCbad, RxDbad); // Структурная модель BER-тестера

Line Line1 (RxCbad, RxDbad, RxCgood, RxDgood); // на основе трех модулей:

DCE DCE1(RxCgood, RxDgood); // DTE, Line и DCE (DTE1, Line1 и //DCE1)

endmodule // стандартное оформление конца модуля

0 комментариев