Навигация

1.2.6. Таймеры/счетчики

МК Z8 может иметь до двух таймеров/счетчиков, в зависимости от модели (см. табл.1.2). Каждый из 8-битных таймеров/счетчиков Т0 и Т1 снабжен 6-битным предделителем PRE0 и PRE1 (рис.1.20). Работа таймеров/счетчиков происходит независимо от работы процессора, что освобождает его от выполнения критичных временных операций, таких как счет событий, измерение временных интервалов, генерирование импульсов заданной длительности и т.п.

Рис. 1.20. Структурная схема таймеров/счетчиков

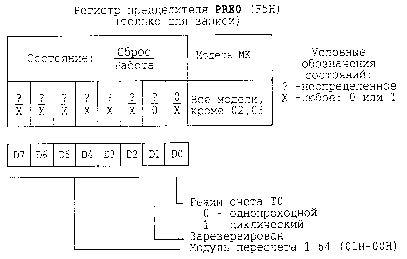

Каждый из таймеров/счетчиков может работать в однопроходном или циклическом режимах. В первом случае, при достижении таймером/счетчиком конца счета, счет прекращается, во втором —начальное значение перезагружается и счет продолжается. При управлении от внутренней синхронизации TCLK (TCLK = XTAL/2 в основном режиме работы генератора), ее частота дополнительно делится на 4. Этот делитель вместе с 6-битным предделителем и 8-битным таймером/счетчиком образуют синхронную 16-битную цепь. Таймер/счетчик T1 может также управляться с внешнего входа TIN, в качестве которого используется вывод Р31. Выходы таймеров/счетчиков и выход внутренней синхронизации могут быть с помощью программы скоммутированы на выход TOUT, в качестве которого используется вывод Р36. Управление работой таймеров/счетчиков осуществляется с помощью регистра режимов таймеров TMR. Регистры таймеров/счетчиков T0 и T1, предделителей PRE0 и PRE1, а также регистр TMR размещены в адресном пространстве СРФ, рабочая группа F ( см. рис.1.2). Поэтому для управления и контроля за работой таймеров/счетчиков никаких специальных команд не требуется. Каждый из предделителей PRE0 (F5H) и PRE1 (F3H) состоит из 8-битного регистра начального значения и 6-битного вычитающего счетчика (см. рис.1.20). Регистры предделителей предназначены только для записи, кроме начального значения содержат управляющие биты. Назначение разрядов этих регистров, их состояние после сброса и в процессе работы поясняется рис.1.21 и рис.1.22. Попытка чтения этих регистров дает результат FF. Начальное значение предделителей может быть в диапазоне от 1 до 64 ( 01H,...,3FH,00H ).

Каждый из таймеров/счетчиков (см. рис.1.20 ) T0 (F4H) иT1 (F2H) состоит из 8-битного вычитающего счетчика, регистра начального значения (только для записи) и регистра текущего значения (только для чтения). Начальное и текущее значения могут быть в диапазоне от 1 до 256 (01H,...,FFH,00H). После сброса состояние регистров T0 и T1 —неопределенное.

Рис. 1.21. Регистр предделителя PRE0

Рис. 1.22. Регистр предделителя PRE1

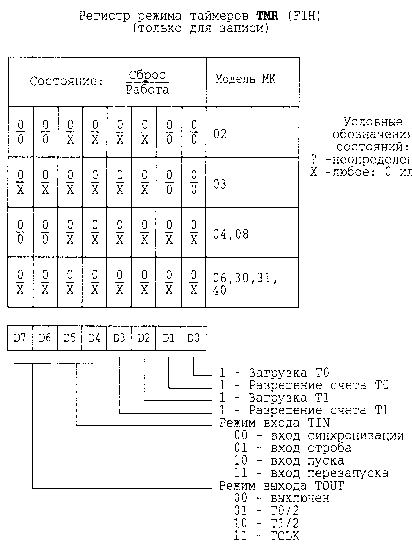

Регистр TMR содержит группы битов, управляющие загрузкой начальных значений, пуском/остановом таймеров, режимом входа TIN и режимом выхода TOUT. Назначение разрядов регистра TMR, состояние их после сброса и допустимые состояния в процессе работы для разных моделей МК показаны на рис.1.23.

Рис. 1.23. Регистр режимов таймеров TMR

Установка бита загрузки (D0 для T0 и D2 для T1) вызывает пересылку начального значения из регистров начального значения соответствующего предделителя и таймера в вычитающие счетчики. После загрузки эти управляющие биты сбрасываются. Новое значение может быть загружено в вычитающие счетчики в любое время. Если счетчики были запущены, то счет будет продолжаться с нового значения.

Таймеры/счетчики сохраняют свое состояние, пока бит разрешения счета (см. рис.1.23) равен 0. Для запуска таймеров/счетчиков соответствующий бит разрешения счета (D1 для T0 и D3 для T1) должен быть установлен в 1. Первый декремент будет иметь место через 4 периода внутренней синхронизации после установки программой бита разрешения счета или в следующем периоде внешней синхронизации (со входа TIN).

Биты загрузки и разрешения могут быть установлены одновременно. Например, с использованием команды

OR TMR,# 03H

можно загрузить и запустить таймер/счетчик T0.

1.2.7. Прерывания

МК Z8 поддерживают 6-уровневую схему приоритетных прерываний от различных источников. Набор внешних источников прерывания связан со входами порта Р3 и инициирует запросы прерывания IRQ0,...,IRQ3 (см.табл. на рис.1.14). К внутренним источникам относятся таймеры/счетчики T0, T1 и последовательный интерфейс SPI. Им соответствуют запросы прерывания IRQ4, IRQ5. Обобщенная структурная схема организации прерываний и таблица соответствия источников показаны на рис.1.24. Следует отметить, что кроме аппаратной установки любой из запросов может быть установлен программным путем.

Аппаратные источники прерываний

| Запрос прерывания | Модель МК | ||||||||

| 02 | 03 | 06 | 04, 08 | 30, 31, 40 | |||||

| IRQ0 | P32 f | P32 s | P32 s | P32 f | P32 s | ||||

| IRQ1 | P33 f | P33 f | P33 f | P33 f | P33 f | ||||

| IRQ2 | P31 f | P31 s | P31 s | P31 f | P31 s | ||||

| IRQ3 | P32 f | SPI | P32 r | P30 f | |||||

| IRQ4 | T0 | T0 | T0 | ||||||

| IRQ5 | T1 | T1 | T1 | T1 | T1 | ||||

Рис. 1.24. Структурная схема организации прерываний

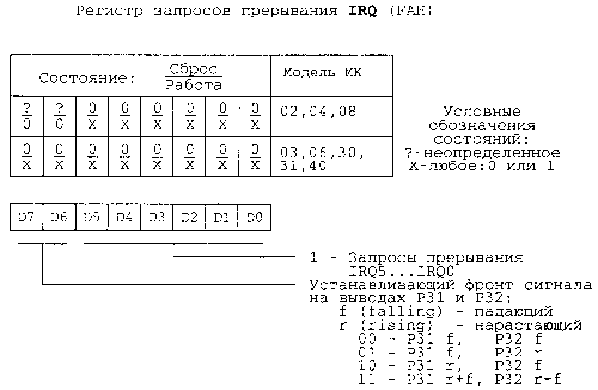

Схема управления прерываниями включает три управляющих регистра: регистр запросов прерывания IRQ, регистр маски прерывания IMR и регистр приоритетов прерывания IPR. Все регистры размещены в СРФ, рабочая группа F. Каждый внешний сигнал устанавливает в 1 соответствующий бит запроса в регистре IRQ (рис.1.25) при появлении фронта сигнала, указанного в таблице на рис.1.24. В моделях 03, 06, 30, 31 и 40 фронт сигнала, устанавливающий запросы IRQ0 и IRQ2, программируется путем записи информации в два старших бита регистра IRQ. Запросы прерываний от таймеров/счетчиков устанавливаются при достижении ими конца счета, а запрос от SPI —по завершении приема символа.

Рис. 1.25. Регистр запросов прерывания IRQ

Регистр маски прерываний IMR (рис.1.26) позволяет маскировать как каждое прерывание IRQ5 —IRQ0 отдельно (биты D5-D0), так и все прерывания глобально (бит D7). Последний бит устанавливается и сбрасывается особыми командами разрешения и запрещения прерываний EI и DI. Он автоматически сбрасывается при вызове подпрограммы обслуживания прерывания и автоматически устанавливается при выполнении команды возврата из подпрограммы обслуживания прерывания IRET. Следует отметить, что перед изменением содержимого IMR или IPR бит D7 регистра IMR должен быть сброшен.

Рис. 1.26. Регистр маски прерываний IMR

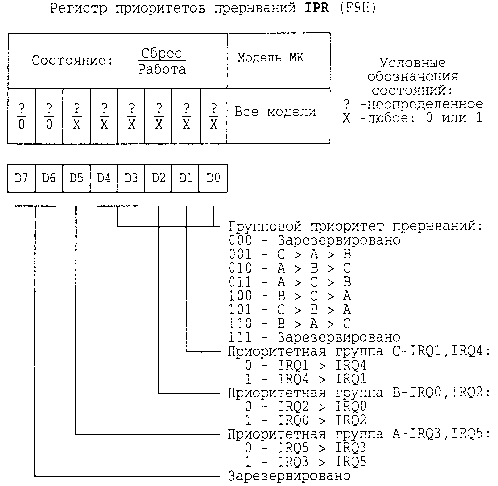

Регистр приоритета прерываний IPR (рис.1.27) позволяет устанавливать любое соотношение приоритетов как между группами прерываний А, В, С, так и между отдельными запросами прерываний внутри группы. В каждую группу включено по два запроса.

МК Z8 поддерживает как процесс векторных прерываний, так и процесс поллинга.

Рис. 1.27. Регистр приоритетов прерываний IMR

В случае векторного процесса каждый уровень прерывания имеет собственный вектор —адрес подпрограммы обслуживания этого уровня прерывания. Векторы прерываний размещены в начальной зоне ПЗУ (см. рис. 1.3). Инициализация процесса векторного прерывания происходит, если прерывания глобально разрешены и есть хотя бы один незамаскированный запрос прерывания. Если таких запросов несколько, то выбирается вектор прерывания с наивысшим приоритетом. Далее реализуется следующая последовательность действий:

— загружается в стек младший байт PC;

— загружается в стек старший байт PC;

—загружается в стек регистр флагов FLAGS;

— читается старший байт вектора;

— читается младший байт вектора;

—вектор загружается в PC.

Эта последовательность занимает 24 такта синхронизации TpC. Наихудшее время реакции на прерывание можно вычислить, прибавив к этому времени 2TpC для синхронизации внешнего запроса прерывания и время выполнения самой длинной команды в прерываемой программе.

0 комментариев