Навигация

Разработка структурной схемы микро ЭВМ

2. Разработка структурной схемы микро ЭВМ.

2.1 Эмуляция ОА в микропроцессорной среде с разрядно-модульной организацией.

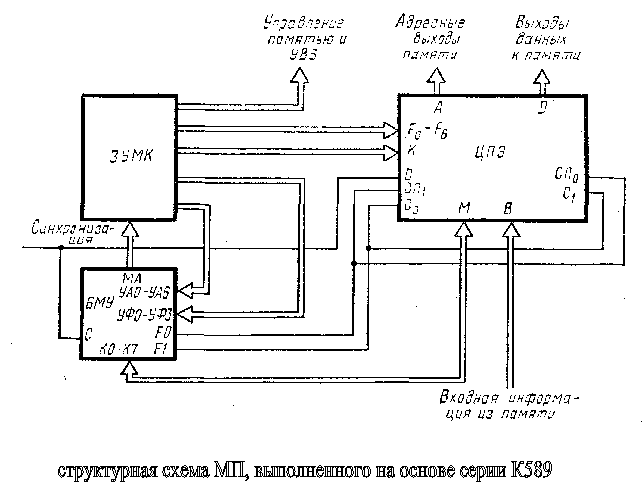

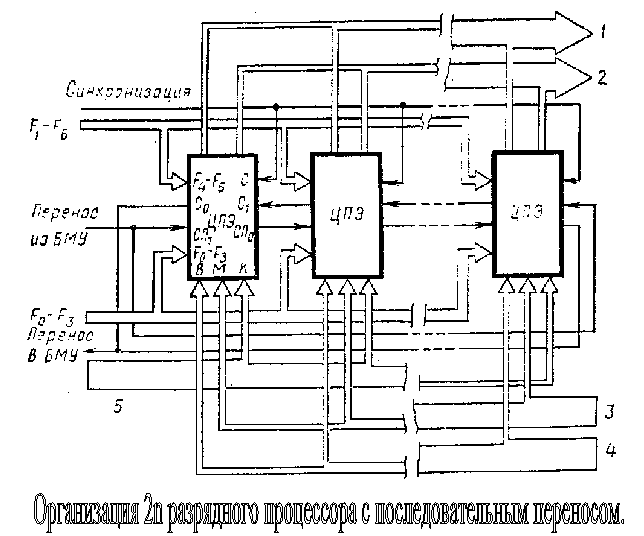

Для достижения требуемой разрядности при использовании микропроцессорной секции К1804ВС1 необходимо объединить между собой шесть микропроцессорных секций. Функциональная схема объединения МПС приведена на рис. 8.

При эмуляции ОА в микропроцессорной среде будем использовать следующие соглашения:

| Номер РОН | Регистр в ОА |

| 1 | Рг.I |

| 2 | Рг.T |

| 3 | Рг.К |

| 4 | Рг.Х |

| 5 | Рг.Р |

| 6 | Рг.Чт. |

| 7 | Рг.Дт. |

| 8 | Рг.Сч. |

| 9 | Рг.Мн. |

| 10 | Рг.Мт. |

| 11 | Рг.LN |

| 12 | Рг.DM |

| 13 | Рг.СМ. |

Рис.8 Функциональная схема объединения МПС.

Сигналы, поступающие на МПС:

А(4 разр.), В(4), I(9), D(24), ![]() (1)

(1)

Для реализации микроопераций ОА необходимо подать на МПС следующие наборы сигналов (в соответствии с форматом):

|

| 0000 | 0001 | 010 | 000111 | 00..00 | 1 |

|

| 0000 | 0010 | 010 | 000111 | 00..00 | 0 |

|

| 0000 | 1011 | 010 | 000111 | 00..00 | 0 |

|

| 0000 | 0011 | 010 | 000111 | 00..00 | 0 |

|

| 0000 | 0100 | 010 | 000111 | X | 0 |

|

| 0100 | 0100 | 010 | 001100 | 00..00 | 0 |

|

| 0100 | 0101 | 010 | 000100 | 00..00 | 0 |

|

| 0000 | 0110 | 010 | 000111 | 00..00 | 0 |

|

| 0001 | 0111 | 010 | 000100 | 00..00 | 0 |

|

| 0100 | 1100 | 010 | 000100 | 00..00 | 0 |

|

| 0000 | 1000 | 010 | 000111 | 00..0010111 | 0 |

|

| 0111 | 1100 | 010 | 001001 | 00..00 | 1 |

|

| 0000 | 1110 | 010 | 000111 | 00..00 | 1 |

|

| 0000 | 1110 | 010 | 000111 | 00..00 | 0 |

|

| 0111 | 1100 | 011 | 000001 | 00..00 | 0 |

|

| 0000 | 1100 | 110 | 000011 | 00..00 | 0 |

|

| 0000 | 0110 | 110 | 000011 | 00..00 | 0 |

|

| 0000 | 0110 | 010 | 000011 | 00..00 | 1 |

|

| 0000 | 1000 | 010 | 001011 | 00..00 | 0 |

|

| 0110 | 0010 | 010 | 000100 | 00..00 | 0 |

|

| 0010 | 1011 | 010 | 000001 | 00..00 | 0 |

|

| 0000 | 0001 | 010 | 000011 | 00..00 | 1 |

|

| 0000 | 1101 | 010 | 000111 | 00..00 | 0 |

|

| 0100 | 1001 | 010 | 000100 | 00..00 | 0 |

|

| 0101 | 1010 | 010 | 000100 | 00..00 | 0 |

|

| 0000 | 1000 | 010 | 000111 | 00..01101 | 0 |

|

| 0000 | 1111 | 010 | 000111 | 00..00 | 0 |

|

| 1001 | 1101 | 010 | 000001 | 00..00 | 0 |

|

| 1001 | 0000 | 110 | 000100 | 00..00 | 0 |

| 0000 | 1101 | 010 | 000001 | 00..00 | 0 | |

|

| 1001 | 1101 | 010 | 001001 | 00..00 | 1 |

|

| 0000 | 1111 | 010 | 000111 | 00..00 | 1 |

|

| 0000 | 1010 | 100 | 000011 | 00..00 | 0 |

| 0000 | 1010 | 100 | 000011 | 00..00 | 0 | |

|

| 0000 | 1001 | 110 | 000001 | 00..00 | 0 |

|

| 1101 | 0100 | 010 | 000100 | 00..00 | 0 |

|

| 0000 | 0100 | 010 | 010011 | 00..00 | 1 |

|

| 0000 | 0011 | 010 | 001011 | 00..00 | 0 |

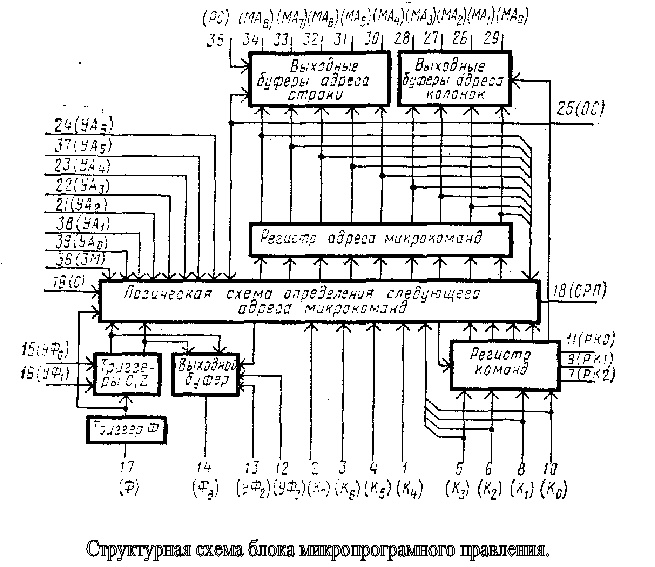

2.2 Эмуляция УА в микропроцессорной СУАМ.

Принципом организации корректного функционирования микро ЭВМ является факт того, что при выполнении определенных команд, выполняется некоторая совокупность микроопераций в тело которым выходит весь набор управляющих сигналов для выполнения определенных действий.

Таким образом, для каждой команды (микрооперации) существует некоторый набор микроопераций, содержащих в своем теле все необходимые управляющие сигналы, последовательное выполнение которых приводит к выполнению команды в целом.

Данная система реализации команд получила название принципа микропрограммной реализации команд и достаточно широко используется при реализации конкретных вычислительных устройств благодаря своей гибкости и производительности.

2.3 Проектирование УУ микро ЭВМ.

2.3.1 Процесс взаимодействия центральной и периферийной ЭВМ.

Очевидно, что разработанная микро ЭВМ является специализированной и не стоит на вершине цепочки управления, а потому необходимо иметь алгоритмы и средства, осуществляющие управление данной микро ЭВМ.

С учетом назначения разрабатываемого устройства (сбор и обработка информации), процесс взаимодействия центральной и периферийной ЭВМ можно обеспечить следующим образом: при поступлении запроса на прерывание от центральной ЭВМ, программа-обработчик данного прерывания производит опрос портов ввода-вывода данного прерывания и, в соответствии с алгоритмом вычисления заданной арифметической функции (ln x), производит обработку полученных данных. После этого периферийная ЭВМ инициирует запрос на прямой доступ к памяти и по каналу ПДП пересылает полученные в результате расчетов данные в ОЗУ центральной ЭВМ, после чего продолжает выполнение прерванной программы.

Похожие работы

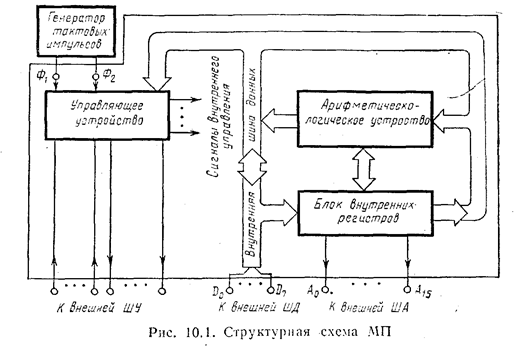

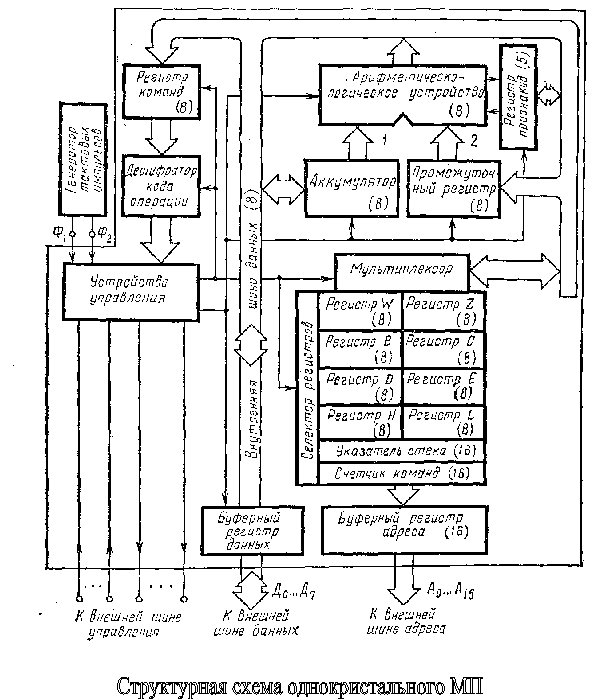

... БПП. Шинные формирователи. Блоки шинных формирователей предназначены для подключения модулей к магистрали. Типичная задержка на ШФ и ШФИ - 20нс, корпус схемы типа ДИП с 16 выводами. Описание структурной схемы микропроцессора. В состав МП (рис. 1) входят арифметическо-логическое устройство, устройство управление и блок внутренних регистров. Арифметическо-логическое устройство ...

0 комментариев