Навигация

3.3.2. ESDRAM.

Следующим оригинальным решением, увеличившим частоту работы SDRAM, явилось создание кэша SRAM на самом модуле динамического ОЗУ. Так появилась спецификация Enhanced SDRAM

(ESDRAM). Это позволило поднять частоту работы модуля до 200 МГц. Назначение кэша на модуле точно такое же, что и кэш второго уровн процессора —хранение наиболее часто используемых данных.

|

3.3.3. SDRAM II.

Рис. B.3.7. Модуль памяти DDR DRAM (SDRAM II)

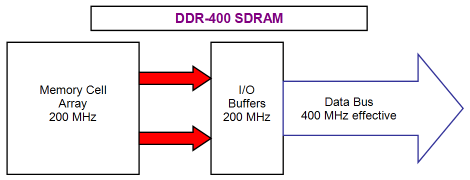

Спецификация SDRAM II (или DDR SDRAM) не имеет полной совместимости с SDRAM. Эта спецификаци позволяет увеличить частоту работы SDRAM за счет работы на обеих границах тактового сигнала, то есть на подъеме и спаде. Однако SDRAM

II использует тот же 168-ми контактный разъем DIMM.

3.3.4. SLDRAM.

Как и SDRAM II, эта спецификаци использует обе границы тактового сигнала и имеет в себе SRAM. Однако благодаря протоколу SynchLink Interface эта память способна работать на частоте до 400 МГц.

|

3.3.5. Память от Rambus (RDRAM, RIMM).

Рис. B.3.8. Модуль памяти RDRAM (RIMM)

RDRAM представляет собой спецификацию, созданную и запатентованную фирмой Rambus, Inc. За счет использования обоих границ сигнала достигается частота работы памяти в 800 МГц.

Подсистема памяти Direct Rambus включает в себя следующие компоненты [Евгений Калугин. Типы памяти.//”Подводная лодка”, январь 2000 г., стр. 166—.]:

8. Direct Rambus Controller.

9. Direct Rambus Channel.

10. Direct Rambus Connector.

11. Direct Rambus RIMM(tm).

12. Direct Rambus DRAMs.

Рассмотрим эти компоненты поподробнее:

1. Контроллер Direct Rambus —это главна шина подсистемы памяти. Он помещается на чипе логики, как и PC-чипсет, микропроцессор, графический контроллер. Физически можно поместить до четырех Direct Rambus —контроллеров на одном чипе логики. Контроллер —это интерфейс между чипом логики и памятью Rambus, и в его обязанности входит генерация запросов, управление потоком данных, и ряд других функций.

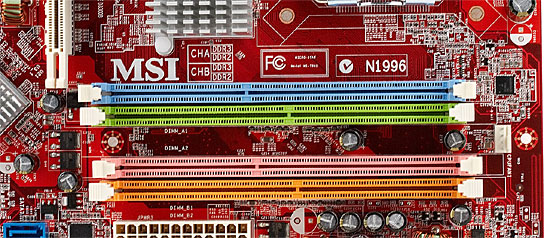

2. Direct Rambus Channel создает электрические соединения между Rambus Controller и чипами Direct RIMM. Работа канала основана на 30-ти сигналах, составляющих высокоскоростную шину. Эта шина работает на частоте 400 МГц и, за счет передачи данных на обеих границах тактового сигнала, позволяет передавать данные на 800 МГц. Два канала данных (шириной в байт каждый) позволяет получать пиковую пропускную способность в 1,6 Гбайт/с. Канал соответствует форм-фактору SDRAM.

3. Разъем Direct Rambus —это разъем со 168 контактами. Контакты расположены на двух сторонах модуля, по 84 с каждой стороны. Разъем представляет собой низкоиндуктивный интерфейс между каналом на модуле RIMM и каналом на материнской плате.

4. Модуль RIMM — это модуль памяти, который включает в

себя один или более чипов и организует непрерывность канала. По существу, RIMM образует непрерывный канал на пути от одного разъема к другому. Поэтому оставлять свободные разъемы недопустимо

Существуют специальные модули только с каналом, называемые continuity modules. Они не содержат чипов памяти и предназначены для заполнени свободных посадочных мест.

Модули RIMM имеют размеры, сходные с геометрическими размерами SDRAM DIMMs. Модули RIMM поддерживают SPD, которые используются на DIMM'ах SDRAM. В отличие от SDRAM DIMM, Direct Rambus может содержать любое целое число чипов Direct RDRAM (до максимально возможного).

Один канал Direct Rambus максимум может поддерживать 32 чипа DRDRAM. На материнской плате может использоваться до трех RIMM модулей. Используются 64 Мбит, 128 Мбит и 256 Мбит устройства.

Чтобы расширить память сверх 32-х устройств, могут использоваться два чипа повторителя. С одним повторителем канал может поддерживать 64 устройства с 6-ю RIMM модулями, а с двумя —128 устройств на 12 модулях.

5. Чипы DRDRAM. Чипы DRDRAM составляют часть подсистемы Rambus, запоминающие данные. Все устройства в системе электрически расположены в канале между контроллером и терминатором. Устройства Direct Rambus могут только отвечать на запросы контроллера, который делает их шину подчиненной или отвечающей. Устройства включают в себя статическое и динамическое ОЗУ.

4. Оперативная кэш-память.

Как уже отмечалось, для динамической оперативной памяти необходима периодическая ее регенерация. В компьютере это осуществляетс централизовано: организуется цикл прямого чтения/записи содержимого динамического ОЗУ. Эта операция осуществляется с помощью специальной микросхемы. В процессе регенерации микропроцессор переходит в режим ожидания, что снижает производительность системы не менее чем на 5%.

Минимальный цикл обращени микропроцессора к оперативной памяти состоит из двух состояний шины. Подсчитано, что около 70% всех обращений процессора к шине компьютера составляет чтение команд, 20% — чтение и запись данных, и только оставшиеся 10% составляют обращения к устройствам ввода-вывода. Поэтому введение даже одного состояния ожидания при обращении к памяти значительно снижает производительность компьютера. Таким образом, существенный рост быстродействия системы может быть достигнут только при сбалансированной работе подсистемы памяти.

|

Для старых персональных компьютеров (на основе микропроцессоров Intel i8088, i8086, i80286 и процессоре i80386/20 МГц) была характерна одноуровневая система организации памяти. По этой системе разработчики были вынуждены устанавливать дешевые DRAM с быстродействием 80 —120 нс, либо применять дорогостоящие SRAM с быстродействием 40 —60 нс. Для сокращени среднего времени ожидания при обращении к операционной системе использовались (и используются в настоящее время) методы интерливинга и страничной организации.

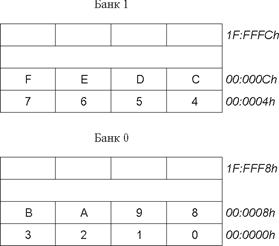

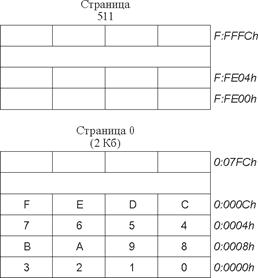

Рис. B.4.1. Система с интерливингом памяти.

В системе с интерливингом —расслоением адресов ячеек памяти —весь объем памяти делится на два или несколько банков. Двойные слова с последовательными адресами располагаются в разных банках. Во время считывания информации из оперативной памяти за один цикл можно организовать параллельное извлечение информации из разных блоков, что уменьшает количество циклов ожидания.

|

Преимущество систем с интерливингом проявляется при обращении к последовательным ячейкам и считывании сразу 32-х бит информации. В противном случае интерливинг не дает никаких преимуществ.

Рис. B.4.2. Система со страничной организации памяти.

В системах со страничной организацией памяти вся память делится на фиксированные по размеру зоны адресов —страницы. Обращение к памяти в пределах страницы происходит без ожидания, а при смене страницы —как обычно, с состояниями ожидания.

При страничной организации память делится на строки и столбцы. Адрес обращения к двойному слову содержит 9-ти разрядный номер строки и 9-ти разрядный номер столбца. При обращении к странице сигнал выбора номера строки поддерживается неизменным, а сигнал выбора столбца переставляется на столбец, откуда нужно прочитать данные.

Страничная организация памяти требует для своей реализации особые микросхемы. Они имеют специальный режим – страничный доступ со статической выборкой столбцов (static column decode).

Для полной реализации потенциальных скоростных возможностей микропроцессоров используется многоуровневая иерархическа память. Она включает в себя быстродействующую кэш-память – SRAM. Кэш-память состоит из памяти данных, построенная на микросхемах SRAM, и контроллера кэша. В кэш-памяти хранитс информация, копируемая из основной оперативной памяти. Каждый раз при обращении микропроцессора к памяти контроллер кэш-памяти проверяет наличие данных в кэше. Если эти данные в кэше есть (“попадание”), то микропроцессор получает данные из кэша. Если этих данных нет (“промах”), выполняется обычный цикл обращения к оперативной памяти DRAM.

Основным фактором, определяющим вероятность попадания, является емкость кэш-памяти. Как правило, при объеме кэша в 2 Кбайта вероятность попадания составляет от 50 до 60%. Поскольку размер кэш-памяти на современных компьютерах превышает 256 Кбайт, то вероятность попадания будет выше 90% (дл компьютеров с объемом памяти ~ 16 Мбайт.)

Для реализации кэш-памяти в настоящее время разработаны эффективные однокристальные контроллеры. Наиболее широкое распространени получили контроллеры i82385 фирмы Intel и A38152 фирмы Asustec Microsystems.

Контроллер i82385 поддерживает 32 Кбайта кэш-памяти, и может работать в двух конфигурациях:

Похожие работы

... подобные. Также интересно будет следить за борьбой Intel и AMD на рынке процессоров Изучение цен и спроса на оперативную память за последний год Исследование проводилось в городе Владивостоке. В качестве объектов исследования были выбраны модули оперативной памяти, имеющиеся в свободной продаже на рынке. Было определено пять основных типов RAM микросхем (SDRAM DIMM 32 MB <PC-100>, ...

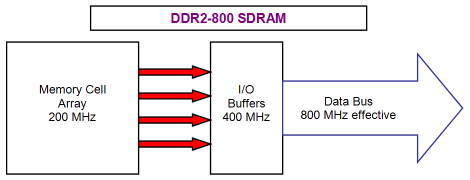

... тепловиділення вирішувалася, як правило, застосуванням звичайних тепловідводів. Коли подальше збільшення тактових частот пам'яті DDR виявилося практично неможливим, на ринку оперативної пам'яті з'явилося нове, друге покоління пам'яті DDR SDRAM - пам'ять DDR2, яка поступово почала доводити свою конкурентоспроможність і поволі, але впевнено витісняти «старе» покоління пам'яті DDR. Первинні варі ...

... доступа затрудняет измерение производительности микросхем памяти и сравнение их скоростных показателей друг с другом. EDO-DRAM (Extended Data Out) память с усовершенствованным выходом С увеличением тактовой частоты микропроцессоров, требовалось качественное новое решение оперативной памяти, а не оптимизация FPM DRAM памяти. И в 1996 году был придуман новый интерфейс оперативной памяти - EDO- ...

... компьютера или на диске. Эти блоки называются программами. Таким образом, входные данные, введенные в память компьютера пользователем, обрабатываются центральным процессором по заранее составленной программе. Результаты обработки сохраняются в памяти компьютера. ЦП контролирует и обслуживает системную шину и оперативную паять, а также, что более важно, выполняет объектный код программ. 3. ...

0 комментариев