Навигация

Блок узгодження з мікроконтролером

2.1.5 Блок узгодження з мікроконтролером

Блок узгодження з мікроконтролером необхідний для узгодження інтерфейсу мікроконтролера з усіма іншими функціональними вузлами. З керуючих сигналів мікроконтролера будуть формуватися сигнали читання й запису всіх основних вузлів. Так само даний блок здійснює розподіл адресного простору мікроконтролера.

Логічні функції покладені на блок:

- прив'язка сигналів інтерфейсу мікроконтролера до загальної тактової частоти;

- формування логіки роботи двунаправленної шини даних мікроконтролера;

- узгодження прийому й передачі інформації від мікроконтролера до зовнішніх пристроїв і назад;

- формування безперервного адресного простору, у якому будуть перебувають всі функціональні вузли.

Вхідні сигнали блоку:

шина адреси від мікроконтролера;

двунаправленная шина даних від мікроконтролера;

сигнал читання від мікроконтролера;

сигнал запису від мікроконтролера;

шина даних від блоку обміну із проміжною буферною пам'яттю;

шина даних від блоку обміну з основним накопичувачем;

шина даних від блоку обміну з годинниками реального часу.

Вихідні сигнали блоку:

сигнали керування режимом роботи блоку обміну із проміжною буферною пам'яттю;

сигнали керування режимом роботи блоку обміну з накопичувачем;

сигнали керування автоматом перезапису;

шина адреси мікроконтролера;

шина даних мікроконтролера;

сигнал читання від мікроконтролера;

сигнал запису від мікроконтролера.

Останні чотири сигнали (шина адреси, шина даних, сигнал читання й сигнал запису) є глобальними сигналами системи й з'єднуються з усіма зовнішніми пристроями (проміжна буферна пам'ять, основний накопичувач, годинник реального часу) через блоки перетворення інтерфейсу.

2.1.6 Блок обміну з годинниками реального часу

Даних блок погодить внутрішній інтерфейс передачі й прийому інформації від мікроконтролера з послідовним інтерфейсом годин реального часу.

Вхідні сигнали блоку:

шина даних від блоку обміну з мікроконтролером;

шина адреси від блоку обміну з мікроконтролером;

сигнал запису від блоку обміну з мікроконтролером;

сигнал читання від блоку обміну з мікроконтролером;

вхідні сигнали від годин реального часу.

Вихідні сигнали блоку:

шини даних (часу) для блоку обміну з мікроконтролером;

вихідні сигнали від годин реального часу.

2.1.7 Блок обміну з основним накопичувачем

Блок обміну з основним накопичувачем погодить інтерфейси накопичувача й внутрішнього інтерфейсу передачі інформації. Блок формує роботу накопичувача в спеціалізованих режимах роботи:

- передача інформації зі швидкісної буферної пам'яті в накопичувач без участі мікроконтролера;

- надання мікроконтролеру доступу до осередків накопичувача.

Вхідні сигнали блоку:

шини адреси від блоку обміну з мікроконтролером і автомата перезапису даних;

шина даних від блоку обміну з мікроконтролером і автомата перезапису даних;

сигнали керування режимом роботи від блоку обміну з мікроконтролером;

сигнал читання від блоку обміну з мікроконтролером;

сигнали запису від блоку обміну з мікроконтролером і автомата перезапису даних;

вхідні сигнали від мікросхем накопичувача великого об'єму.

Вихідні сигнали блоку обміну:

вихідна шина даних для блоку обміну з мікроконтролером;

вихідні сигнали для мікросхем накопичувача.

2.1.8 Мікроконтролер

Мікроконтролер є основним керуючим вузлом даної системи. Він здійснює загальне керування роботою розроблювального блоку й забезпечує зв'язок із ПК по засобах USB інтерфейсу. У даній системі мікроконтролер прямо взаємодіє тільки із блоком обміну з мікроконтролером.

Вхідні сигнали блоку:

двунаправлена шина даних;

USB.

Вихідні сигнали блоку:

шина адреси;

сигнал читання;

сигнал запису;

двунаправлена шина даних;

USB.

2.1.9 Накопичувач

Накопичувач являє собою набір мікросхем Flash пам'яті великого об'єму. Даний блок прямо взаємодіє тільки із блоком обміну з накопичувачем.

Вхідні сигнали блоку:

сигнал вибірки;

сигнал запису;

сигнал читання;

шина адреси;

двунаправлена шина даних.

Вихідні сигнали блоку:

сигнал «Вільний/Зайнятий»;

двунаправлена шина даних.

Подальше пророблення функціональних вузлів блоку можливі при обраній елементній базі, що дозволить більш детально визначити режими роботи всієї системи.

2.2 Вибір елементної бази

Для реалізації функціональної схеми проведемо вибір елементної бази. На вибір елементів впливає безліч факторів от деякі з них:

- доступність технічної інформації про елементи;

- доступність самих елементів у продажі в Україні;

- можливість застосування елемента при заданих зовнішніх умовах;

- маса - габаритні характеристики елементів;

- електричні параметри й характеристики.

Складність вузлів, описаних у функціональній схемі, змушує переходити на елементи високого ступеня інтеграції, застосовувати імпортну елементну базу. Нижче представлені елементи і їхні характеристики, на яких зупинився наш попередній вибір.

Основним обчислювачем і керуючою ланкою блоку є мікроконтролер. Так само необхідно щоб він сполучав у собі функції контролера USB інтерфейсу, необхідний для взаємодії з персональним комп'ютером. На сьогоднішній день існує цілий ряд мікроконтролерів різних фірм виробників, які задовольняють цим умовам. Один з найбільш відомих виробників мікроконтролерів - ATMEL і мікроконтролери серії АТ89. Це недорогі мікроконтролери з відомим ядром 8051. Реалізація схеми вимагає мінімум додаткової прив'язки. Немаловажне й наявність безкоштовного асемблера, компілятора мови З, програматора й драйверів для Windows/Linux. Зручна можливість програмування процесора не по SPI, а «прямо» по USB каналі. У даній серії є кілька мікроконтролерів з інтерфейсом USB, зупинимося на АТ89С5131. До складу даного мікроконтролера входять:

- 32 Кбайт убудованої флэш-пам'яті із внутрісхемним програмуванням через USB або UART інтерфейси;

- 4 Кбайт EEPROM для завантажувального сектора (3 Кбайт) і даних (1 Кбайт);

- 1 Кбайт убудованого розширеного ОЗУ;

- USB 1.1 і USB 2.0 FS модуль із перериванням на завершення передачі.

Мікроконтролер AT89C5131 містить спеціальний апаратний модуль, що дозволяє йому забезпечити обмін даними по USB інтерфейсі. Структурна схема USB модуля мікроконтролера АТ89С5131 наведена на малюнку 2.2. Для роботи даного модуля необхідні опорні синхроімпульси із частотою 48 Мгц, які виробляються контролером синхронізації. Ці синхроімпульси використовуються для формування 12 Мгц тактових імпульсів із прийнятого диференціального потоку даних на високій швидкості, що відповідає вимогам до USB пристроїв.

Малюнок 2.2 - Структурна схема USB модуля мікроконтролера АТ89С5131

Мікросхема RTC4543 є мікросхемою годин реального часу. Дана мікросхема має здатність зберігати дані в дуже широкому діапазоні напруг, крім того, у неактивному режимі має вкрай мале енергоспоживання, що дозволяє застосовувати для підтримки їхньої працездатності батареї малих габаритів. Мікросхема годин має наступні характеристики:

– точність роботи годин (макс.) – 1 хв/мес. при температурі 25 °С;

– температурний робочий діапазон – від мінус 40 до +85 °С;

- час доступу до даних пам'яті - від 70 нс;

- напруга живлення - від 2,5 до 5,5 У;

- корекція ходу календаря на 100 років;

- автоматична корекція високосного року.

У якості швидкісної буферної пам'яті буде використана мікросхема IDT71V424S15YI, що являє собою високошвидкісне статичне ОЗУ організоване 512 до ? 8 біт. Вона зроблена по фірмовій високопродуктивній і дуже надійній технології фірми Integrated Device Technology (IDT). У неактивному режимі має низьке енергоспоживання. Основні характеристики мікросхеми:

- мінімальна тривалість сигналу запису - 15 нс;

- час вибірки адреси - не більше 12 нс;

- напруга живлення 3,3 У;

- час переходу в активний/неактивний режим - 6 нс;

– температурний діапазон зберігання даних – від мінус 55 до +125 °С.

Цифрова частина системи виконана на базі ПЛИС. Це зручна в освоєнні й застосуванні елементна база, альтернативи якої в цьому випадку не існує. Останні роки характеризуються різким ростом щільності впакування елементів на кристалі й різкому падінні цін на ПЛИС, що дозволило широко застосовувати ПЛИС у системах обробки сигналів. Висока швидкодія й упакування на кристалі достатнього об'єму пам'яті однозначно визначили вибір ПЛИС.

У розробленій системі застосована мікросхема ПЛИС EPF10K30AQI240-3 фірми Altera Corporation сімейства FLEX 10KA. Такий вибір обумовлений тим, що сімейство FLEX10KA є найбільш доступним. Тільки це сімейство має градацію швидкості 3, що задовольняє необхідним вимогам. Обрана ПЛИС має 6 убудованих блоків пам'яті ємністю 2048 біт, корпус TQFP-240 комерційного виконання. Напруга живлення мікросхеми EPF10K30AQI240-3 становить +3,3 У. Дана мікросхема забезпечує достатню швидкодію й володіють необхідним для системи реєстрації даних об'ємом убудованих блоків пам'яті ЕАВ. Мікросхеми EPF10K30AQI240-3 підтримує програмування в системі, це означає, що програмування проходить у складі системи без використання програматора на змонтованій платі, причому програмування ПЛИС або конфігураційного ПЗУ може вироблятися багаторазово. Програмування виробляється по стандартному JTAG інтерфейсі (використовується стандарт IEEE Std. 1149.1-1990). Для програмування й завантаження конфігурації ПЛИС використовується кабель ByteBlasterMV.

Тому що обрана мікросхема ПЛИС виконаний за технологією SRAM, що вимагає завантаження конфігурації при включенні живлення, у системі необхідно використовувати конфігураційне ПЗУ. У якості конфігураційного ПЗУ була обрана мікросхема EPC2TI32, що, так само як і ПЛИС, підтримує програмування в системі по стандарті JTAG.

Основний накопичувач виконаний на базі мікросхеми ФЛЕШ K9K49G08U0M ємністю 4 Гбит з резервом ємністю 128 Мбит організовані як 512 М ? 8 біт. Технологія Й-НЕ забезпечує найкраще співвідношення « ціна-якість» на ринку напівпровідникових запам'ятовувальних пристроїв. Операція запису сторінки об'ємом 2112 байт може бути виконана за 200 мкс. Операція стирання блоку об'ємом 128 Кбайт може бути виконана за 2 мс. Дані зі сторінки даних можуть бути прочитані циклами по 30 нс на байт. Висновки I/O служать як двунаправлений порт для уведення команд, адреси й уведення/висновку даних. Внутрішній контролер запису автоматизує всі функції запису й стирання, включаючи частоту повторення імпульсів там, де це необхідно, а також внутрішню верифікацію й обмеження даних. Навіть інтенсивно записуючі системи можуть скористатися перевагами розширеної вірогідності 100 K циклов запису/стирання K9K4G08U0M, забезпечуючи ЕСС (код виправлення помилок) по алгоритму відображення в реальному часі. Мікросхеми K9K4G08U0M є оптимальним рішенням для застосування в розроблювальній системі реєстрації даних у якості твердотельного накопичувача великого об'єму пам'яті.

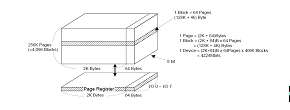

Мікросхема K9K4G08U0M - це пам'ять об'ємом 4224 Мбит, організована як 262144 рядка (сторінки) по 2112?8 стовпців. Запасні 64 стовпця перебувають по адресах почата з 2048 по 2111. 2112-ти байтовий регістр даних і 2112-ти байтовий кеш-регістр послідовно з'єднаний з іншими. Ці послідовно з'єднані регістри з'єднані з масивом комірок пам'яті, для узгодження передачі даних між I/O буферами й комірками пам'яті при операції читання або запису сторінки. Масив пам'яті складається з 32-х осередків, послідовно з'єднаних для формування структури. Кожна з 32 осередків перебувають на різних сторінках. Блок складається з 2 рядків з І-НЕ структурою. І-НЕ структура складається з 32 осередків. Усього в блоці 1081344 І-НЕ осередків. Операції читання й записи виконуються посторінково, тоді, як операція стирання виконується поблочне. Масив пам'яті складається з 4096 блоків, що стираються окремо, об'ємом 128 Кбайт. Структура мікросхеми K9K4G08U0M наведена на малюнку 2.3.

Малюнок 2.3 - Структура мікросхеми K9K4G08U0M

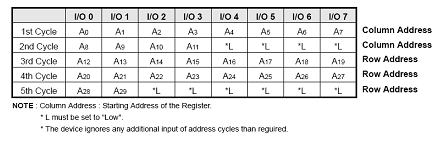

Адреса K9K4G08U0M мультиплексирован на 8 висновків (таблиця 2.1). Така схема істотно зменшує число висновків і допускає подальше підвищення щільності зі збереженням погодженості на системній платі. Команди, адреса й дані записуються через входи/виходи перекладом WE у низький рівень при низькому рівні на вході РЄ. Дані зберігаються по фронті сигналу WE. Сигнали дозвіл запису команди (CLE) і дозвіл запису команди адреси (ALE) використовуються для націлити команд і адреси відповідно із прихожих на входи/виходи даних. Деякі команди вимагають одного шинного циклу, наприклад, команда скидання, команда читання стану й т.д. Для інших команд, таких як читання сторінки, стирання блоку й запис сторінки, необхідно 2 цикли: один на установку й іншої - на виконання команди. 512 Мбайт фізичного об'єму вимагають 30-розрядної адреси, таким чином, необхідно 5 циклів запису адреси: 2 цикли для адресації по стовпцях (Column) і 3 цикли для адресації по рядках (Row).

Таблиця 2.1 – Адресація мікросхеми K9K4G08U0M

Для операції читання й запису сторінки так само необхідні 5 циклів запису адреси, що випливають за потрібною командою. Однак для операції стирання блоку потрібно всього 3 цикли запису адреси (адреса сторінки). Операції із пристроєм вибираються записом спеціальних команд у командний регістр (таблиця 2.2).

Таблиця 2.2 – Список команд мікросхеми K9K4G08U0M

| Функція | 1 цикл | 2 цикл | Позачергова команда |

| Читання | 00h | 30h | |

| Читання для перезапису | 00h | 35h | |

| Читання сигнатури | 90h | - | |

| Скидання | FFh | - | V |

| Запис на сторінку | 80h | 10h | |

| Запис у кеш | 80h | 15h | |

| Перезапис | 85h | 10h | |

| Стирання блоку | 60h | D0h | |

| Довільне уведення даних* | 85h | - | |

| Довільний висновок даних* | 05h | E0h | |

| Читання статусу | 70h | - | V |

* Довільне уведення/висновок даних можливий у межах 1 сторінки.

Прискорити запис даних можна за допомогою кеш-регістра об'ємом 2112 байт. Запис у кеш-регістр може бути зроблена під час перезапису даних з регістра даних у комірки пам'яті (під час програмування). Після закінчення програмування, при наявності даних у кеш регістрі, внутрішній контролер мікросхеми перепише дані з кеш-регістра в регістр даних і почне запис нової сторінки.

Пристрій реалізує функцію автоматичного читання при включенні живлення, що забезпечує послідовний доступ до даних першої сторінки після включення живлення без уведення команди й адреси.

На додаток до розширеної архітектури й інтерфейсу пристрій включає функцію резервного копіювання даних з однієї сторінки на іншу без використання зовнішньої буферної пам'яті. Так як трудомісткі цикли послідовного доступу й уведення даних виключені, то продуктивність системи для застосування в напівпровідникових дисках значно поліпшена.

Пристрій може містити неприпустимі блоки при першому використанні. Під час використання мікросхеми кількість неприпустимих блоків може зрости. Неприпустимі блоки - це блоки, які містять 1 або більш споконвічно непрацездатних битов, надійність яких не гарантується компанією Samsung. Пристрою з неприпустимими блоками мають той же рівень якості й ті ж динамічні й статичні характеристики, як і пристрою без таких блоків. Неприпустимі блоки не впливають на роботу нормальних блоків, тому що вони ізольовані від розрядної шини й загальної шини живлення транзистором вибору. Система спроектована таким чином, що в неприпустимих блоків блокуються адреси. Відповідно, до некоректних биток попросту немає доступу. Перший блок, що поміщається в 00-й адреса, повинен використовуватися для зберігання завантажувальної інформації. SAMSUNG запевняє, що він буде гарантовано припустимим, не потребуючим виправлення помилок протягом 1 К циклів запису/читання.

Споконвічний уміст всіх осередків мікросхеми стерте (FFh), за винятком осередків, де зберігається інформація про неприпустимі блоки, записана до цього. Допустимість блоку визначається 1-ым байтом запасного простору. Samsung запевняє, що 1 або 2 сторінка кожного неприпустимого блоку за адресою стовпця 2048 містить дані, що відрізняються від FFh. Тому що інформація про неприпустимі блоки є що стирається, то в більшості випадків стирання її неможливо відновити. Тому, у системі повинен бути закладений алгоритм, здатний створити таблицю неприпустимих блоків, захищену від стирання й засновану на первісній інформації про браковані блоки. Будь-яке навмисне стирання інформації про неприпустимі блоки заборонено.

Отже є ймовірність виходу з ладу блоків мікросхеми під час експлуатації системи, що може привести до втрати інформації. Для підвищення надійності зберігання інформації варто збільшити об'єм основний накопичувач у два рази до 8 Гб.

Похожие работы

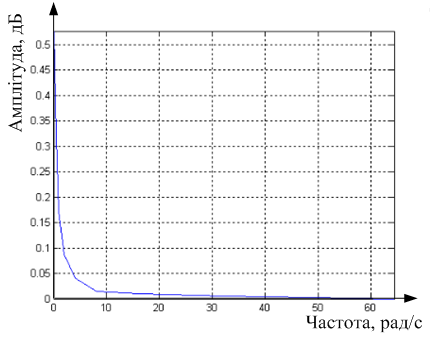

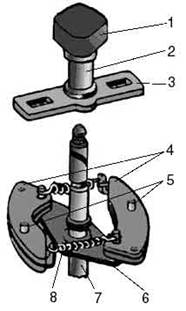

... 4 виконавців, тривалість виконання робіт складає 153 днів, ціна теми складає 7. Забезпечення життєдіяльності і питання екології 7.1 Аналіз шкідливих і небезпечних чинників В даній дипломній роботі і досліджений сервопривод урахуванням нелінійності. Основним місцем роботи була науково-виробнича дослідницька лабораторія (НВДЛ) №402, кафедри №301. При проведенні робіт в лабораторіях поді ...

... і над плановим. Відомо, що собівартість є одним з головних джерел резервів підвищення ефективності роботи підприємства. Звідси сформуємо мету і задачі даної роботи. Метою даної роботи є підвищення ефективності роботи підприємства ВАТ «Дніпрополімермаш» шляхом управління собівартістю продукції. Відповідно, для досягнення поставленої мети необхідно вирішити наступні задачі: 1. Проаналізувати ...

... ією палива, підвищенням продуктивності автомобіля в цілому і окремих його вузлів; збільшенням його ресурсу й в остаточному підсумку підвищенням коефіцієнта готовності парку. Витрати на діагностику системи запалення включають капіталовкладення на придбання й установку діагностичного встаткування, вартість займаних їм виробничих площ і експлуатаційні витрати, пов'язані із проведенням діагностики ( ...

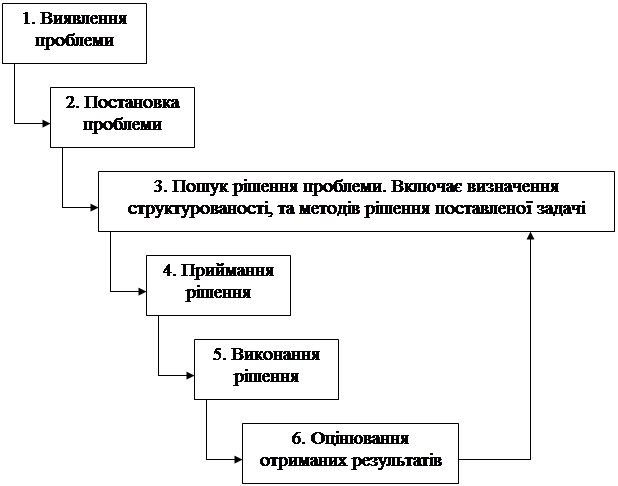

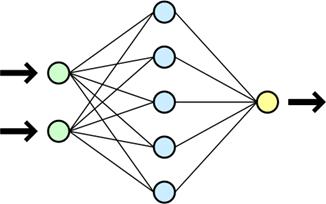

... . Про це можна судити з того, що тема штучного розуму, що захопив світ є досить розповсюдженою і популярною. Але окремі особистості, що схильні глибше іти у своєму пізнанні і розумінні проблеми штучного інтелекту, натикаються на величезну кількість етичних і глибоко філософських проблем, що він підіймає самою можливістю свого існування. Частина ІІІ. Гностична діяльність штучного інтелекту ...

0 комментариев