Навигация

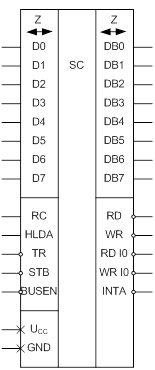

Системный контроллер и шинный формирователь КР580ВК28

3.3 Системный контроллер и шинный формирователь КР580ВК28

Рис 3.3 Системный контроллер и шинный формирователь КР580ВК28

Системный контроллер и шинный формирователь КР580ВК28 предназначен для фиксации слова-состояния МП, выработки системных управляющих сигналов, буферизации шины данных МП и управлением передачи данных. Системный контроллер формирует управляющие сигналы по сигналам состояния микропроцессора при обращении к ЗУ: RD и WR; при обращении к УВВ: RD IO и WR IO, а также обеспечивает прием и передачу 8-разрядной информации между каналом данных микропроцессора по выводам D7-D0 и системным каналом по выводам DB7-DB0. Регистр состояния по входному сигналу STB фиксирует информацию состояния микропроцессора в первом такте каждого машинного цикла. Дешифратор управляющих сигналов формирует один из управляющих сигналов в каждом машинном цикле: RD, WR, RD IO, WR IO, INTA. Асинхронный сигнал BUSEN управляет выдачей данных с буферной схемы и управляющих сигналов: при напряжении высокого уровня все выходы микросхемы переводятся в высокоомное состояние.

Назначение выводов микросхемы приведено в таблице 3.3.

Таблица 3.3. Назначение выводов микросхемы

| Вывод | Обозначение | Тип вывода | Функциональное назначение выводов |

| 1 | STB | Вход | Стробирующий сигнал состояния (от ГТИ) |

| 2 | HLDA | Вход | Подтверждение захвата |

| 3 | TR | Вход | Выдача информации |

| 4 | RC | Вход | Прием информации |

| 5,7 9,11, 13,16, 18,20, | DB4,DB7, DB3,DB2, DB0,DB1, | Вход/выход | Канал данных системы |

| 6,8,10, 12,15,17, 19,21 | D4,D7,D3, D2,D0,D1, D5,D6 | Входы/выходы данных со стороны МП | |

| 14 | GND | — | Общий |

| 22 | BUSEN | Вход | Управление передачей данных и выдачей сигналов |

| 23 | INTA | Выход | Подтверждение запроса прерывания |

| 24 | RD | Выход | Чтение из ЗУ |

| 25 | RD IO | Выход | Чтение из УВВ |

| 26 | WR | Выход | Запись в ЗУ |

| 27 | WR IO | Выход | Запись в УВВ |

| 28 | UCC | Вход | Напряжение питания +5В |

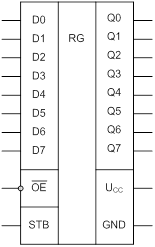

3.4 Буферный регистр КР580ИР82

Рис 3.4 Буферный регистр КР580ИР82

Буферный регистр КР580ИР82, выполняет роль буфера между МП и шиной данных. Буферный регистр КР580ИР82 представляет собой 8-разрядный параллельный регистр с трехстабильными выходами. Обладает повышенной нагрузочной способностью.

Таблица 3.4. Назначение выводов микросхемы

| Вывод | Обозначение | Тип вывода | Функциональное назначение выводов |

| 1 | D0-D7 | Вход | Информационная шина |

| 2 | OE | Вход | Разрешение передачи (управление 3-м состоянием) |

| 10 | GND | — | Общий |

| 11 | STB | Вход | Стробирующий сигнал |

| 12-19 | Q0-Q7 | Выход | Информационная шина |

| 20 | UCC | — | Напряжение питания +5В |

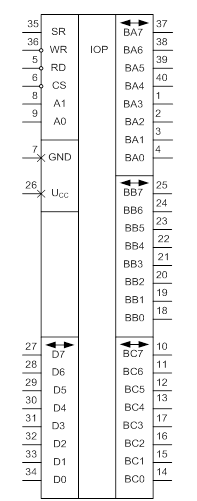

Произведя запись управляющего слова в РУС, можно перевести микросхему в один из трех режимов работы. При подаче SR РУС устанавливается в состояние, при котором все каналы настраиваются на работу в режиме 0 для ввода информации. Формат управляющего слова определения режима работы показан в таблице 3.51.

Параллельный интерфейс КР580ВВ55А предназначен для ввода/вывода параллельной информации различного формата. БИС программируемого параллельного интерфейса (ППИ) может использоваться для сопряжения микропроцессора со стандартным периферийным оборудованием.

В состав БИС входят: двунаправленный 8-разрядный буфер данных (BD), связывающий ППИ с системной шиной данных; блок управления записью/чтением (RWCU), обеспечивающий управление внешними/внутренними передачами данных, управляющих слов и информации о состоянии ППИ; три 8-разрядных канала ввода/вывода (PA, PB, PC) для обмена информацией с внешними устройствами. Режим работы каждого из каналов определяется содержимым регистра управляющего слова (РУС).

Таблица 3.51 Формат управляющего слова, определяющего режим работы:

| Разряд УС | Значение разряда УС | Задаваемый режим работы |

| D7 | 1 | - |

| D6D5 | 00 | Режим 0 для канала ВА и 4-7 разрядов канала ВС |

| 01 | Режим 1 для канала ВА и 4-7 разрядов канала ВС | |

| 1X | Режим 2 для канала ВА и 4-7 разрядов канала ВС | |

| D4 | 0 | Вывод из канала ВА |

| 1 | Ввод в канал ВА | |

| D3 | 0 | Вывод из 4-7 разрядов канала ВС |

| 1 | Ввод в 4-7 разряд канала ВС | |

| D2 | 0 | Режим 0 для канала ВВ и 0-3 разрядов канала ВС |

| 1 | Режим 1 для канала ВВ и 0-3 разрядов канала ВС | |

| D1 | 0 | Вывод из канала ВВ |

| 1 | Ввод в канал ВВ | |

| D0 | 0 | Вывод из 0-3 разрядов канала ВС |

| 1 | Ввод в 0-3 разряды канала ВС |

Рис 3.5 Параллельный интерфейс КР580ВВ55А

Назначение выводов микросхемы приведено в таблице 3.52.

Таблица 3.52. Назначение выводов микросхемы

| Вывод | Обозначение | Тип Вывода | Функциональное назначение вывода |

| 1-4, 37-40 | BA3-BA0, BA7-BA4 | Входы/ Выходы | Информационный канал А |

| 5 | RD | Вход | Чтение информации |

| 6 | CS | Вход | Выбор микросхемы |

| 7 | GND | - | Общий |

| 8,9 | A1,A0 | Вход | Младшие разряды адреса |

| 10-17 | BC7-BC4 BC0-BC3 | Входы/ Выходы | Информационный канал C |

| 18-25 | BB0-BB7 | Входы/ Выходы | Информационный канал B |

| 26 | Ucc | - | Напряжение питания |

| 27-34 | D7-D0 | Входы/ Выходы | Канал данных |

| 35 | SR | Вход | Установка в исходное состояние |

| 36 | WR | Вход | Запись информации |

В нашем случае получено управляющее слово 89h – 10001001 – переводит DD7 в режим ввода/вывода (режим 0). Соответственно данное УС определяет: каналы ВА и ВВ – вывод, а все восемь бит канала ВС – ввод.

Похожие работы

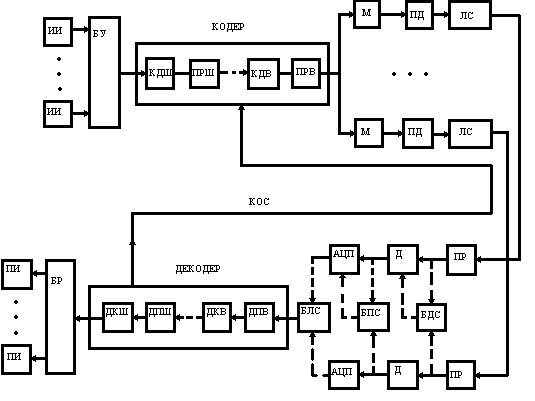

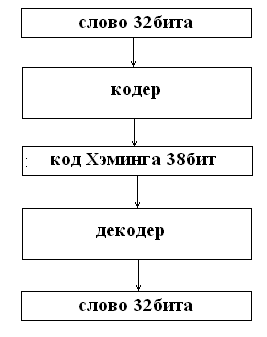

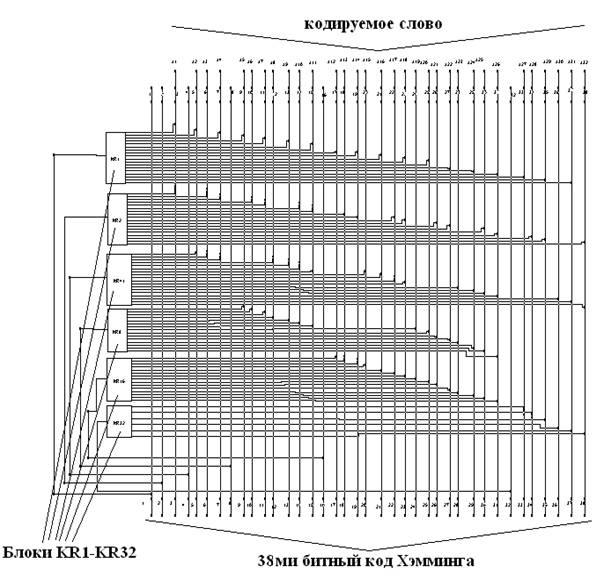

... кодирования можно разработать устройство, которое поможет понять принцип работы метода Хэмминга. Кодер – декодер будем разрабатывать на основе ИМС К555ВЖ1. 2.1 Разработка устройства кодирования информации методом Хемминга Кодер, преобразует 32х битное слово в 38ми разрядный код Хэмминга, после чего слово хранится в памяти или передаётся по шинам и т.д. В процессе передачи или хранения в ...

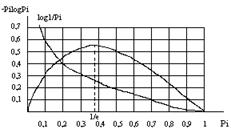

... , работавших в области электротехники, заинтересовалась возможностью создания технологии хранения данных, обеспечивающей более экономное расходование пространства. Одним из них был Клод Элвуд Шеннон, основоположник современной теории информации. Из разработок того времени позже практическое применение нашли алгоритмы сжатия Хаффмана и Шеннона-Фано. А в 1977 г. математики Якоб Зив и Абрахам Лемпел ...

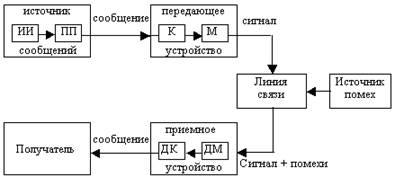

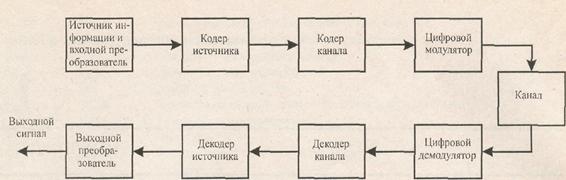

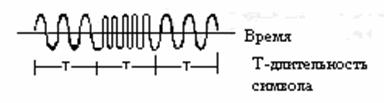

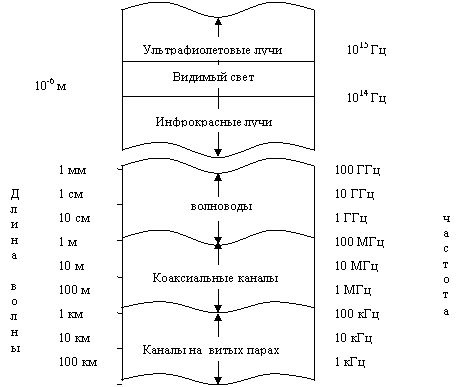

... за которым следует устройство дискретизации (рисунок 4.2), подастся известный сигнал s(t) плюс шум AWGN n(t). 4.4 Межсимвольная интерференция На рисунке 4.3 а) представлены фильтрующие элементы типичной системы цифровой связи. В системе - передатчике, приемнике и канале - используется множество разнообразных фильтров (и реактивных элементов, таких как емкость и индуктивность). В передатчике ...

0 комментариев