Навигация

Особенности построения цифровых узлов средств отображения информации

КОНТРОЛЬНАЯ РАБОТА ПО ТЕМЕ:

Особенности построения цифровых узлов СОИ

1. Буферные запоминающие устройства буквенно-цифровых СОИ

Буферные запоминающие устройства (БЗУ) выполняют как модули ОЗУ с произвольной выборкой на основе полупроводниковых накопителей – БИС ОЗУ НК, объединяемых в прямоугольную матрицу из mC рядов по mP БИС в каждом ряду. Такая организация обеспечивает требуемые число ячеек памяти ЗУ NЗУ и их разрядность nЗУ. В модуль ЗУ входят также схемы согласования выходных и входных информационных и адресных сигналов и схема дешифратора адреса.

Требуемая разрядность nЗУ БЗУ и число ячеек памяти NЗУ определяется в соответствии с выражениями

nЗУ = nа; NЗУ = NЗНС * NТС,

а информационная емкость -

CБЗУ = NЗУ * nЗУ.

Требуемое быстродействие (разрешающая способность) определяется исходя из требуемого времени выборки относительно адреса:

tА £ bГ (1 - aС) / (NЗНТС fС) – tвПЗУ – tDCrA - tDСОГЛ,

где tвПЗУ - время выборки ПЗУ знакогенератора; tDCrA и tDСОГЛ - время задержки в счетчике адреса и согласующих схем.

Выбор типа БИС ОЗУ из выпускаемых промышленностью определяется требуемым быстродействием и информационной емкостью БЗУ. Разрядность накопителя nНК должна быть кратна разрядности БЗУ nЗУ. Коэффициент кратности определяет число БИС ОЗУ НК mP в ряду матрицы накопителей и должно быть целочисленным:

nНК = nЗУ / mP.

Аналогичные условия накладываются относительно числа ячеек памяти накопителя NНК:

NНК = NЗУ / mСТ.

Тогда общее количество БИС ОЗУ НК, входящих в модуль ЗУ

m = mP * mСТ.

При mP ¹ 1 и mС ¹ 1 организуют ЗУ (форматирование информационных входных и выходных цепей модуля), объединяя все одноименные информационные входы Di и выходы Qi mC БИС входящих в один столбец матрицы накопителей. Объединение информационных входов осуществляют непосредственно, объединение же информационных входов зависит от типа выходных цепей БИС: для БИС с ТТЛ-выходами объединение производят с помощью логической схемы “ИЛИ”; выходы с открытым коллектором объединяют по схеме “монтажного ИЛИ”; выходы БИС с высокоимпедансным состоянием объединяют непосредственно (рекомендуется применять).

Адресацию ячеек памяти организуют по двухкоординатному принципу – выбор ряда матрицы накопителей осуществляется по входам выбора микросхем ВК (вход обеспечения высокоимпедансного состояния), выбор же ячеек памяти в ряду – по адресным входам БИС, объединяя одноименные адресные разряды. При этом из k = ] log2 NЗУ [ адресных разрядов модуля ЗУ k1 = ] log2 NНК [ разряд выделяют для адресации ячеек памяти в пределах одного ряда матрицы накопителей, а k2 = k – k1 старших разрядов - для адресации рядов матрицы. Для реализации последней применяют дешифратор k2 - разрядного кода в унитарный десятичный код. Каждый выход дешифратора подключают к объединенным входам выбора микросхем ВК одного ряда накопителей. Для реализации последней применяют дешифратор k2 – разрядного кода (дешифратор двоичного кода в унитарный десятичный). Каждый выход дешифратора подключается к объединенным входам ВК одного ряда матрицы накопителей

Чтобы определиться с требуемой нагрузочной способностью микросхем определяют токи и емкость нагрузки:

по информационным входам –

![]() ,

,

где ![]() и

и ![]() - входные токи при “0” и “1” на одном информационном входе ИМС; С1вх - входная емкость по одному входу; С0вх - паразитная входная емкость, включая монтажную;

- входные токи при “0” и “1” на одном информационном входе ИМС; С1вх - входная емкость по одному входу; С0вх - паразитная входная емкость, включая монтажную;

по информационным выходам БИС ОЗУ НК с высокоимпедансным состоянием

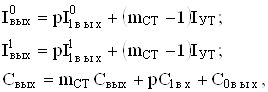

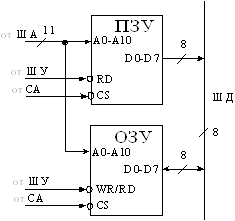

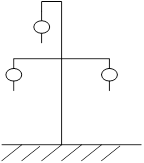

Приведем пример функциональной схемы модуля БЗУ емкостью 3Кх8, построенного с использованием БИС ОЗУ НК емкостью 1Кх4 (рис. 1). Здесь разрядность кода знака – 8, разрядность адреса – 12, mСТ = 3, mP = 2, k1 = 10, k2 = 2. Заметим, что для сокращения числа выводов следует использовать ОЗУ с двунаправленными информационными шинами вход/выход, коммутируемыми сигналом Зп/Чт.

Похожие работы

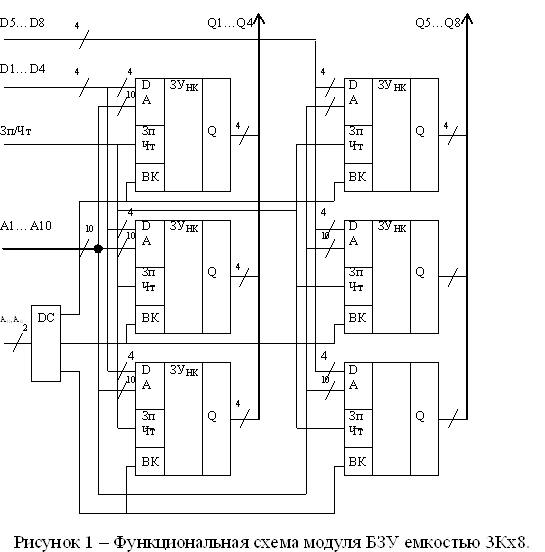

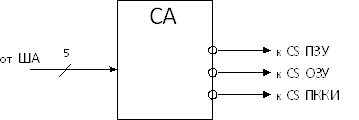

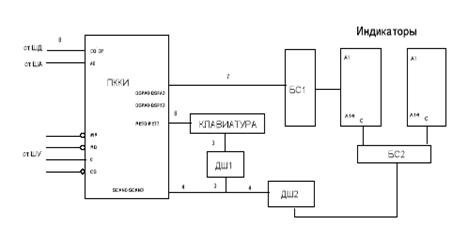

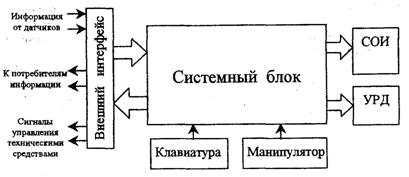

... ОЗУ – оперативное запоминающее устройство; СА – селектор адреса; ШУ – шина управления; ША – шина адреса; ШД – шина данных Рисунок 1 – Структурная схема микропроцессорного устройства Основным узлом разрабатываемого устройства отображения информации является ЦП. В его функции входит управление всеми остальными узлами устройства. Отдельные блоки соединяются между собой линиями, объединяемыми по ...

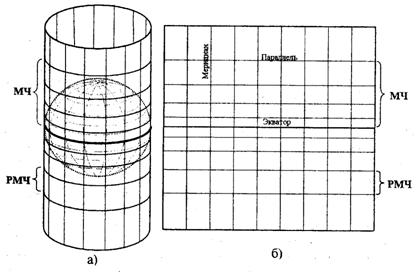

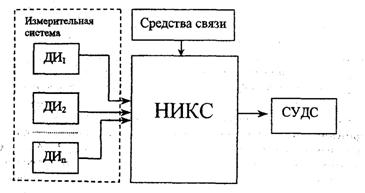

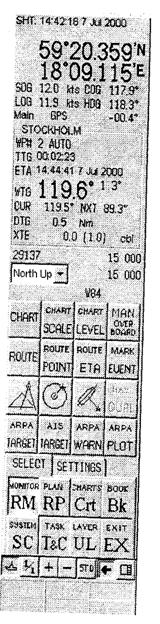

... информации. Набираемая информация отображается на дисплее, что позволяет контролировать ее правильность. Клавиатура и дисплей АИС должны быть независимыми от других навигационных устройств. Судовыми системами отображения АИС могут быть система отображения электронных карт (ECDIS, ECS, RCDS), РЛС, САРП или дисплей персонального компьютера. АИС и связанные с ней датчики информации питаются от ...

... 9С467-2 позволяет осуществлять тренировку боевого расчета. Для организации режима тренажа служит прибор 209Н, который управляется ЭВМ. Изделие 9С467-2 имеет возможности выдачи информации на выносное рабочее место. 1.3. Тракты прохождения информации Тракт первичной информации. Сопряжение КСА с РЛС и ПРВ осуществляется с помощью устройства коммутации сигналов "СССП" УКМ (коробка КР14), устройства ...

... 1.5 Уровни помех и линейных затуханий 1.5.1 Электрические помехи в каналах ВЧ связи по ВЛ Электрические помехи имеются в любом канале связи. Они являются основным фактором, ограничивающим дальность передачи информации из-за того, что сигналы, принимаемые приемником, искажаются помехами. Для того чтобы искажения не выходили за пределы, допустимые для данного вида информации, должно быть ...

0 комментариев