Навигация

Описание работы проектируемого блока по схеме электрическая принципиальная

4.3 Описание работы проектируемого блока по схеме электрическая принципиальная

На входы регистров Рг.1 микросхем DD1 и DD2 поступает число [А] с 10-и разрядной шины данных в прямом коде на входы D0-D7 микросхемы DD1 и входы D0-D1 микросхемы DD2, с управляющим сигналом CS1.

Аналогично поступает число [B] на микросхемы DD3,DD4.

После, число [А] и [В] в прямом коде поступают на преобразователи кодов построенных на элементах " искл. или " и реализованных на микросхемах DD5-DD10, где операнды [А] и [В] из прямого кода преобразуются в обратно модифицированный код ( в знаковой области поятся второй разряд и число будет 11 разрядное с 2 разрядами в знаковой части ).

Далее операнды поступают на сумматор в обратно модифицированном коде, реализованный тремя четырёх разрядными АЛУ выполняющими операцию сложения (для нормальной работы сумматора на входы Е0 и Е4 уровень логического "0", а на входы М, Е2, Е3 подаём уровень логической "1", в случае переполнения, с выхода С0 на вход С4 следующего АЛУ будет произведён перенос логической "1", в противном случае "0").

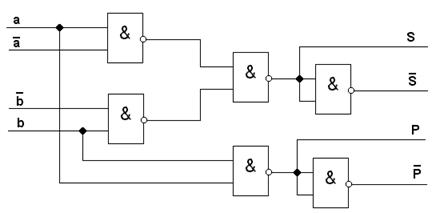

Затем происходит проверка результата в обратно модифицированном коде на наличие переноса, данный блок реализован на элементе "искл. или", на входы подаются два разряда из знаковой области результата, и в случае переполнения на выходе будет уровень логической "1", в противном случае "0".

Далее результат в обратно модифицированном коде попадает в преобразователь кода, который построен по такой же технологии что и преобразователь кода описанный ранее.

Далее результат в прямом коде поступает на входы десяти разрядного регистра Рг3 реализованном как сказано выше, на двух восьми разрядных регистрах, с управляющим сигналом CS3.

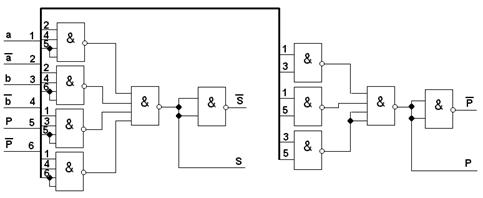

Затем происходит определение флагов S, P, Z:

Флаг Z – реализован на 3 элементах "3ИЛИ-НЕ" объединённых в один корпус и 1 элементом "3И-НЕ" и 1 элементе "НЕ".

Флаг P - реализован на 6 элементах "искл. или" и 1 элементе "НЕ".

Флаг S – это знак результата.

Эти данные вносятся в четырёх разрядный регистр флагов с управляющим сигналом CS3.

5. Расчетная часть

В данном разделе выполняется расчет:

- времени выполнения операции в разработанном блоке;

- мощности потребляемой блоком;

- параметров надежности блока.

5.1 Расчет времени выполнения операции в БСДЧСПЗ

Основой для расчета послужили:

1. Схема электрическая принципиальная.

2. Таблица 2. Параметры микросхем.

3. Временные диаграммы, разработанные для схемы электрической функциональной.

4. Формулы, выведенные для проведенных ВД.

Время срабатывания для схемы электрической функциональной определяется по формуле:

t1= τзад.Рг1 = 30,5 [нс]

t2 = τзад.Рг2+τзад.ЛП5+ τзад.,DD11 + τзад.DD121 + τзад.DD13 + τзад.,Лп5 =

= 30,5 + 27,5+50+50+50+27,5 = 235,5 [нс]

t3 = τзад.Рг3 + τзад.ЛП5(DD21) + τзад.ЛП5(DD22) + τзад.ЛП5(DD22) + τзад.ЛП5(DD22) +

+τзад.ЛН1 =30,5+27,5+27,5+27,5+27,5+8,5 = 149 [нс]

t4 = τзад.Рг4 = 30,5 [нс]

Tвып.операции = t1 + t2 + t3 + τ4=30,5+205+149+30,5= 445,5 [нс]

5.2 Расчёт потребляемой мощности

РпотрИР13 = 0,116*5 = 0,58 Вт

РпотрЛП5 = 0,05*5 = 0,25 Вт

РпотрИП3 = 0,15*5 = 0,75 Вт

РпотрЛЕ4 = 0,068*5= 0,034 Вт

РпотрЛА4 = 0,0165*5 = 0,082 Вт

РпотрЛН1 = 0,033*5 = 0,165 Вт

РпотрИР13 = 0,116*5 *7= 4,06 Вт

РпотрЛП5 = 0,05*5*12 = 3 Вт

РпотрИП3 = 0,15*5*3= 2,25 Вт

РпотрЛЕ4 = 0,068*5*1 = 0,034 Вт

РпотрЛА4 = 0,0165*5*1 = 0,082 Вт

РпотрЛН1 = 0,033*5*1 = 0,165 Вт

Рпотр БСДЧфз = 4,06+3+2,25+0,034+0,082+0,165 = 9,5 Вт

5.3 Расчёт параметров надёжности

Надёжность - это комплексное свойство машин, технических устройств, систем, приборов, заключающееся в его способности выполнять заданные функции, сохраняя при этом свои характеристики при определённых условиях эксплуатации, в установленных пределах.

Критерии надёжности:

1. Вероятность безотказной работы - это вероятность того, что при определённых условиях эксплуатации в заданном пределе времени не произойдёт ни одного отказа.

Р(t) = е-λΣ*t

2. Интенсивность отказов - это отношение числа отказавших изделий в единицу времени к среднему числу изделий, исправно работающих в данный отрезок времени.

![]()

Похожие работы

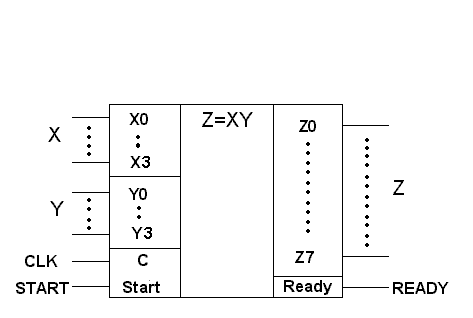

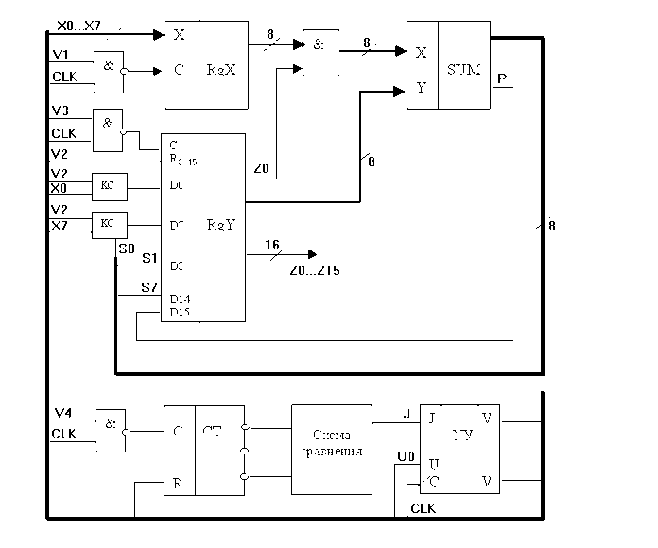

... RgХ и RgY имеют как прямые, так и инверсные выходы , что позволяет уменьшить количество элементов в сумматоре. Рисунок 2.2 Структурная схема АЛУ для умножения двоичных чисел. Как видно из схемы активный уровень сигналов управления - высокий, и устройство управления тактируется по фронту импульса, а исполнительные устройства - по спаду, что позволяет избежать гонок в схеме. 3 Синтез ...

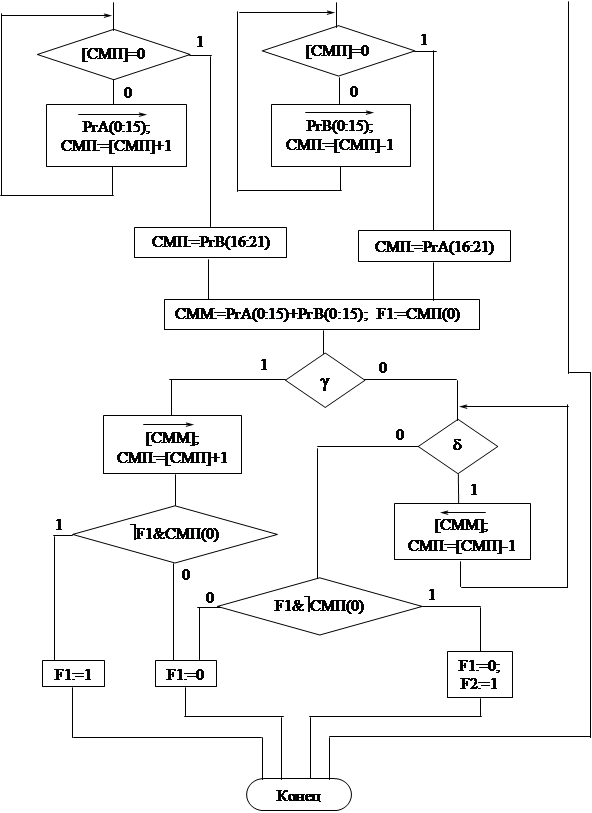

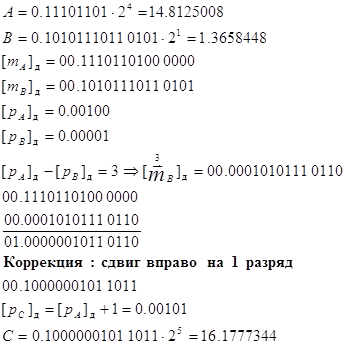

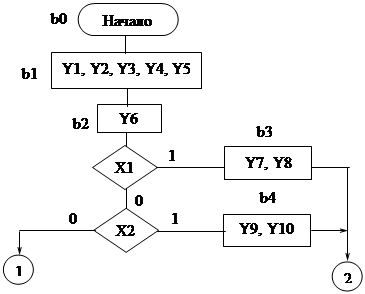

... . . . . . . . . . 14 Задание Разработать управляющую часть автомата для сложения двух чисел с плавающей запятой в дополнительном коде с помощью модели Мура. Логическую схему реализовать в базисе «И-НЕ» на D-триггерах. Раздел 1. Разработка машинного алгоритма выполнения операции. Шаг 1. Сравнить порядки чисел A ...

... в широкую практику разработки программ объектно-ориентированного программирования, впитавшего в себя идеи структурного и модульного программирования, структурное программирование стало фактом истории информатики. Билет № 9 Текстовый редактор, назначение и основные функции. Для работы с текстами на компьютере используются программные средства, называемые текстовыми редакторами или текстовыми ...

... быть выведены на печать. На экране рисунки могут быть статическими (неподвижными) или динамическими (движущимися). В последнее время машинная графика выделилась в самостоятельный раздел информатики с многочисленными приложениями. Средствами машинной графики создается не только печатная продукция, но и рекламные ролики на телевидении, мультфильмы. Объясним, как кодируется изображение в памяти ...

0 комментариев