Навигация

Разработка устройств сопряжения для магистрали ISA

2.5 Разработка устройств сопряжения для магистрали ISA

Магистраль ISA была разработана специально для персональных компьютеров типа IBM PC AT (начиная с процессора i80286) и относится к демультиплексированным (то есть имеющим раздельные шины данных и адреса) 16-разрядным системным магистралям среднего быстродействия [6]. Обмен осуществляется 8- или 16-разрядными данными. На магистрали реализован раздельный доступ к памяти компьютера и к устройствам ввода-вывода (для этого имеются специальные сигналы). Максимальный объём адресуемой памяти составляет 16 Мбайт (24 адресные линии). Максимальное адресное пространство для устройств ввода-вывода – 64 Кбайт (16 адресных линий), хотя практически все выпускаемые платы расширения используют только 10 адресных линий (1 Кбайт). Магистраль поддерживает регенерацию динамической памяти, радиальные прерывания и прямой доступ к памяти. Допускается также захват магистрали.

Разъём магистрали ISA разделён на две части, что позволяет уменьшать размеры 8-разрядных плат расширения. Назначение контактов разъёма ISA в виде таблицы представлено в ПРИЛОЖЕНИИ 1.

В режиме программного обмена информацией на магистрали ISA выполняется четыре типа циклов:

- цикл записи в память;

- цикл чтения из памяти;

- цикл записи в устройство ввода-вывода

- цикл чтения из устройства ввода-вывода.

Циклы различаются используемыми сигналами и протоколами обмена, поэтому при проектировании аппаратуры для сопряжения с ISA необходимо учитывать временные диаграммы используемых циклов обмена. Другими словами должна быть реализована информационная совместимость.

Помимо циклов программного обмена на магистрали ISA могут выполняться также циклы прямого доступа к памяти. Так как на магистрали имеются раздельные стробы чтения и записи для устройств ввода-вывода и для памяти, пересылка данных в режиме ПДП производится за один машинный цикл. То есть если данные необходимо переслать из устройства ввода-вывода в память, то одновременно производится чтение данных из устройства ввода-вывода (по сигналу –IOR) и их запись в память (по сигналу –SMEMW).

При проектировании устройств сопряжения для ISA надо учитывать также электрические характеристики сигналов. Стандарт магистрали определяет требования к входным токам приёмников и источников сигналов каждой из плат расширения. Не соблюдение этих требований может нарушить функционирование компьютера.

Выходные каскады передатчиков магистральных сигналов должны выдавать ток низкого уровня не меньше 24 мА, а ток высокого уровня – не меньше 3 мА. Входные каскады приёмников магистральных сигналов должны потреблять входной ток низкого уровня не больше 0,8 мА, а входной ток высокого уровня – не больше 0,04 мА.

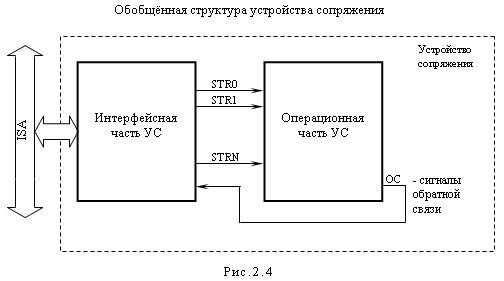

В структуре любого устройства сопряжения можно выделить две части: интерфейсную и операционную (рис.2.4). Интерфейсная часть обеспечивает непосредственное сопряжение данного устройства с ISA, то есть обеспечивает необходимые параметры сигналов с соблюдением протокола обмена. Операционная часть несёт на себе функции, ради которых, собственно, и создавалось устройство сопряжение. Подходы к проектированию этих двух частей имеют принципиальные отличия.

Операционные части различных устройств могут быть самыми разнообразными в зависимости от решаемых задач. Интерфейсные части практически у всех устройств одинаковы или очень похожи между собой, так как интерфейсные функции жёстко определяются протоколом выбранного стандартного интерфейса (в данном случае ISA).

В соответствии с определением интерфейса, в число главных функций интерфейсной части входит обеспечение информационной, электрической и конструктивной совместимости. Информационная совместимость предполагает точное выполнение протоколов обмена и правильное использование сигналов магистрали. Электрическая совместимость подразумевает согласование уровней входных, выходных и питающих напряжений и токов. Вопрос о конструктивной совместимости в основном касается конечного этапа разработки устройства – проектирования печатной платы и сводится к точному соблюдению всех размеров платы, разъёмов и крепёжных элементов.

К основным функциям интерфейсной части можно отнести:

- буферирование сигналов магистрали;

- селектирование или дешифрация линий адреса;

- выработка внутренних стробирующих сигналов.

Буферирование сигналов применяется для электрического согласования и выполняет две основные функции: электрическая развязка (для всех сигналов) и передача сигналов в нужном направлении (только для двунаправленных сигналов). Иногда с помощью буферирования реализуется также мультиплексирование сигналов [6].

Другой основной функцией интерфейсной части является селектирование и дешифрация адреса. Эту функцию выполняет узел, называемый селектором адреса, который должен выработать сигналы, соответствующие выставлению на шине адреса магистрали кода адреса, принадлежащего данному устройству, или одного из зоны адресов данного устройства. Важно, чтобы адреса проектируемого устройства не перекрывались с адресами, занятыми другими устройствами компьютера. В том случае если устройство сопряжения работает в адресном пространстве памяти селектор адрес должен обрабатывать 20 разрядов адресной шины (при полном объёме памяти до 1 Мбайт) или больше при бóльшем объёме памяти.

Выработка внутренних стробирующих сигналов должна происходить синхронно с магистральными командными сигналами (-IOR, -IOW, -SMEMR, -SMEMW и др.). Для организации асинхронного обмена по шине ISA в низких скоростных характеристик устройства, используется сигнал I/O CH RDY, снятие которого, установка в состояние логического нуля, говорит о неготовности к циклу чтения (записи).

2.6 Обмен данными с компьютеромСуществует четыре основных способа обмена данными с компьютером:

- по опросу флага готовности

- в режиме прерывания программы

- в режиме прямого доступа к ОЗУ компьютера

- с использованием автономного контроллера с буферной памятью в качестве накопителя.

Перечисленные способы обмена данными отличаются различными скоростями передачи данных и уровнем сложности аппаратуры, необходимой для их реализации.

Обмен экспериментальных данных с компьютером, работающим по опросу флага готовности внешнего устройства, требует минимальных затрат на разработку и изготовление дополнительной аппаратуры. Данный способ обмена характеризуется достаточно высокой скоростью реакции на обслуживание. Однако это обходится постоянной занятостью процессора тривиальными операциями опроса флага [3].

Если необходимость в обмене возникает достаточно редко, то наиболее приемлемым будет способ обмена с использованием прерывания. Реализация режима прерывания программы требует некоторого усложнения интерфейса связи с объектом, но это позволяет освободить процессор от периодического опроса устройства сопряжения и он в этом случае может заниматься другими задачами. Однако, использование аппаратных прерываний ни в коем случае не увеличивает скорости обмена с устройством сопряжения, наоборот, уменьшает её. Это связано с тем, что реакция на прерывание гораздо медленнее, чем на выставление флага готовности, т.к. чтобы обслужить прерывание процессор должен завершить текущий цикл, сохранить в стеке текущие значения своих регистров и только потом инициализировать контроллер прерываний и перейти на программу обработки прерывания [3,6].

Прямой доступ к памяти предназначен для быстрого обмена данными между устройством ввода-вывода и системной памятью компьютера. Использование режима ПДП весьма специфично. Во-первых, это связано с тем, что максимальный темп выдачи и приёма информации возможен только при передачи большого массива данных и даже в режиме блочной передачи пересылка одного байта (слова) требует нескольких тактов SYSCLC и занимает около 1 мкс. Как известно в поле адресов устройств ввода-вывода свободных адресов крайне мало, поэтому на практике возможен только последовательный доступ к буферному ОЗУ устройства ввода-вывода, что дополнительно снижает скорость обмена, и требует усложнения аппаратуры.

Наибольшую скорость выдачи или приёма данных обеспечивают не устройства сопряжения с прямым доступом, а устройства с так называемой разделяемой памятью, в которых быстрая буферная память, расположенная на плате устройства сопряжения доступна как со стороны внешнего устройства, так и со стороны магистрали ISA. При этом процессор рассматривает эту буферную память, как часть системного ОЗУ. В этом случае приём информации в ОЗУ компьютера или выдача её может осуществляться со скоростью до 50 Мбайт/с и выше.

Рассматривая устройства сопряжения имеющие буферные ОЗУ, можно выделить две большие группы:

- устройства сопряжения с непрерывным режимом обмена с внешним устройством. В этом случае буферное ОЗУ непрерывно выдаёт на внешнее устройство или принимает от него данные, а процессор в определённые моменты соответственно записывает или считывает необходимые ячейки этого ОЗУ.

- устройства сопряжения с периодическим режимом обмена. Буферное ОЗУ может находиться в одном из двух режимов: в режиме обмена с компьютером (запись или чтение содержимого ОЗУ) или в режиме обмена с внешним устройством (приём или выдача).

По методу доступа к буферному ОЗУ со стороны компьютера устройства сопряжения могут быть разделены на следующие группы:

- устройства с параллельным доступом к буферному ОЗУ;

- устройства с последовательным доступом к буферному ОЗУ.

Схематически оба метода представлены на рисунке 2.5.

При параллельном доступе каждой ячейке буферного ОЗУ соответствует свой адрес в адресном пространстве компьютера. В этом случае любой задатчик магистрали (процессор, контроллер ПДП и т.д.) может общаться с буферным ОЗУ как с системным, используя для этого все средства, все методы адресации, команды обработки строк. Данные, с точки зрения программиста, накапливаются непосредственно в памяти компьютера.

Естественно это наиболее быстрый метод общения с буферным ОЗУ (а также и с внешним устройством), так как в данном случае не требуется времени для перекачки данных из системной памяти в буферное ОЗУ или наоборот. Адресное пространство устройств ввода-вывода в данном случае использовать нецелесообразно, так как в нем нет достаточно больших непрерывных зон свободных адресов. Кроме того, возможности процессора по работе с памятью гораздо богаче, чем по общению с устройствами ввода-вывода.

При последовательном доступе данные буферного ОЗУ по очереди проецируются в один из адресов в адресном пространстве компьютера (или реже в несколько адресов). То есть задатчик при обращении по одному и тому же адресу в разное время общается с разными ячейками буферного ОЗУ. Главный недостаток этого подхода резкое снижение темпа обмена, а очевидное преимущество – экономия адресов магистрали [6].

3. РАЗРАБОТКА ЦИФРОВЫХ УСТРОЙСТВ НА БАЗЕ ПЛИС 3.1 Современные и перспективные ИС со сложными программируемыми структурамиРазмеры плат микро-PC составляют всего 114×124 мм, поэтому для создания крупных систем нужно использовать микросхемы высокой степени интеграции и стараться разметить всю схему в минимальное число корпусов элементов.

Наряду со стандартными, в системе накопления, как и в любой другой системе, присутствуют и нестандартные части, специфичные для данной разработки. Это могут быть различные схемы управления, схемы реализации заданного алгоритма и т.п. Процесс реализации нестандартной части устройства, как правило, связан применением микросхем малой и средней степени интеграции. Применение малых и средних ИС неизбежно приводит к росту числа корпусов ИС, усложнением монтажа и отладки, снижением быстродействия и надёжности схем. Заказать для системы специализированные ИС высокого уровня интеграции затруднительно, т.к. это связано с большими затратами средств и времени. Существующее противоречие может быть разрешено путём применения современных программируемых логических интегральных схем [7].

Первыми представителями программируемых ИС явились программируемые логические матрицы ПЛМ, программируемая матричная логика ПМЛ и базовые матричные кристаллы БМК, называемые также вентильными матрицами. ПМЛ и ПЛМ в английской терминологии часто объединяются термином PLD, Programmable logic Devices.

Развитие БИС/СБИС с программируемой и репрограммируемой логикой оказалось настолько перспективным направлением, что привело к созданию новых эффективных средств разработки цифровых систем, таких

как CPLD (Complex PLD), FPGA (Field Programmable Gate Array) и SPGA (System Programmable Gate Array).

Основой программируемых логических матриц служит последовательность элементов И и ИЛИ. В структуру также входят блоки входных и выходных буферных каскадов (рис. 3.1)

Входные буферы, как правило, предназначены для преобразования однофазных входных сигналов в парафазные и формирования сигналов необходимой мощности для питания матрицы элементов И.

Выходные буферы обеспечивают необходимую нагрузочную способность выходов, разрешают или запрещают выход ПЛМ на внешние шины с помощью сигнала OE, а иногда выполняют и более сложные действия.

Переменные x1…xm подаются через входные буферные каскады на входы элементов И, и в матрице И образуют L термов. Терм – это конъюнкция, связывающая входные переменные, представленные в прямой или инверсной форме. Число формируемых термов равно числу выходов матрицы И.

Термы подаются далее на входы матрицы ИЛИ, т.е. на входы дизъюнкторов формирующих выходные функции. Число дизъюнкторов равно числу вырабатываемых функций N. Воспроизводимые функции являются комбинациями из любого числа термов, формируемых матрицей И. Какие именно термы будут выработаны и какие комбинации этих термов составят входные функции, определяется программированием. Таким образом, ПЛМ способна реализовать систему N логических функций от M аргументов, содержащую не более L термов.

Принцип программирования основан на том, что в матрицах имеются системы горизонтальных и вертикальных связей , в узлах которых при программировании создаются или ликвидируются связи. В качестве узлов связей используются диоды. До программирования все перемычки целы и диоды связи размещены во всех узлах координатной сетки. При программировании в схеме остаются только необходимые элементы связи, а ненужные устраняются пережиганием перемычек.

Логическая мощность ПЛМ зачастую используется не полностью. Это проявляется, в частности, при воспроизведении типичных функций, не имеющих больших пересечений друг с другом по одинаковым термам. В таких случаях возможность использования выходов любых конъюнкторов любыми дизъюнкторами становится излишним усложнением. Отказ от этой возможности означает использование не программируемой, а заданной матрицы ИЛИ. Структура в которой выходы матрицы И жёстко распределены между элементами ИЛИ получила название ПМЛ. В сравнении с ПЛМ схемы ПМЛ имеют меньшую гибкость, т.к. матрица ИЛИ фиксирована, но их изготовление дешевле и использование проще.

Отдельной ветвью в развитии программируемых интегральных схем являются базовые матричные кристаллы (вентильные матрицы с масочным программированием). Основа первых БМК – совокупность регулярно расположенных на кристалле базовых ячеек (БЯ), между которыми имеются свободные зоны (каналы) для создания соединений. БЯ занимают внутреннюю область БМК, в которой они расположены по столбцам, и содержат группы нескоммутированных элементов (транзисторов, резисторов и др.). В периферийной области размещены ячейки ввода-вывода. Потребитель может реализовать на основе БМК некоторое множество устройств определённого класса, задав тот или иной вариант рисунка межсоединений компонентов. Основной характеристикой БМК помимо числа эквивалентных вентилей является трассировочная способность, которая определяется площадью отводимой для межэлементных связей в ортогональных направлениях. Недостаточная трассировочная способность приводит к уменьшению числа задействованных при построении базовых ячеек. Избыточная трассировочная способность ведёт к нерациональному использованию кристалла, что понижает уровень интеграции БМК и повышает его стоимость. Для решения подобных проблем строятся многослойные БМК, при этом число слоёв межсоединений может составлять от 2 до 6 и более.

Ранее перечисленные архитектуры ПЛИС, содержащие небольшое количество ячеек, к настоящему времени морально устарели и применяются для реализации относительно простых устройств, для которых не существует готовых ИС средней степени интеграции [8]. Для реализации крупных проектов они не пригодны.

Развитие технологий, опыт использования программируемых интегральных логических схем (ПЛИС) приводит к выводу, что это максимально удобная в освоении и применении элементная база, альтернативы которой зачастую не найти. Последние годы характеризуются резким ростом плотности упаковки элементов на кристалле, многие ведущие производители либо начали серийное производство, либо анонсировали ПЛИС с эквивалентной ёмкостью более одного миллиона эквивалентных вентилей на кристалл.

Современные ПЛИС классифицируются по конструктивно-технологическому типу программируемых элементов. Число программируемых двухполюсников (программируемых точек связи ПТС) в ПЛИС зависит от сложности и может доходить до нескольких миллионов. Наиболее характерны следующие виды программируемых ключей:

- перемычки типа antifuse

- ЛИЗМОП транзисторы с двойным затвором

- ключевые транзисторы, управляемые триггерами памяти конфигурации (теневым ЗУ) [7].

Программирование с помощью перемычек antifuse является однократными. Высококачественные перемычки фирмы Actel компактны, имеют очень малые токи в первоначальном (непроводящем) состоянии (порядка10-15А). Перемычка образована трёхслойным диэлектриком с чередованием слоёв оксид-нитрид-оксид. Программирующий импульс напряжения пробивает перемычку и создаёт проводящий канал из поликремния между электродами. Величина тока, создаваемого импульсом программирования, влияет на диаметр проводящего канала (например ток 5 мА создаёт перемычку с сопротивление 600 Ом, ток 15мА – 100 Ом) [7].

Элементы EPROM и EEPROM на ЛИЗМОП (МОП-структуры с лавинной инжекцией заряда) транзисторах с плавающих затвором используются в ПЛИС, где с помощью программируемой памяти задаётся конфигурация схемы. Стирание старой конфигурации в ПЛИС на основе EPROM требует длительного (около 1 часа) облучения УФ-излучением. Такие микросхемы имеют ограничение количества циклов перепрограммирования из-за деградации свойств полупроводниковых материалов под воздействием ультрафиолета. Технология EEPROM, для обновления не требует извлечения микросхемы, допускает достаточно большое число циклов стирания (104…106). Процесс стирания и обновления конфигурации занимает время порядка миллисекунд. В последнее время схемотехника EEPROM совершенствуется и всё больше вытесняет схемотехнику EPROM. Технология программируемой памяти применяется в ПЛИС типа CPLD.

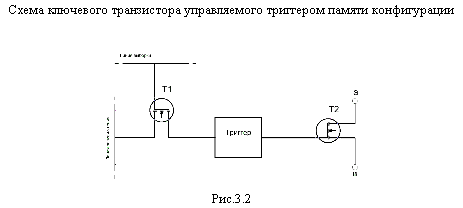

В качестве программируемого элемента связи в ПЛИС FPGA используется транзисторный ключ, управляемый триггером, показанный на рис.3.2

В качестве программируемого элемента связи в ПЛИС FPGA используется транзисторный ключ, управляемый триггером, показанный на рис.3.2

Ключевой транзистор Т2 замыкает или размыкает участок АВ в зависимости от состояния триггера. При программировании на линию выборки подаётся высокий потенциал, и транзистор Т1 включается. С линии записи-чтения подаётся сигнал, устанавливающий триггер в состояние «1» и «0».

Загрузка соответствующих данных в память конфигурации программирует ПЛИС. Быстрый процесс оперативного программирования может производиться неограниченное число раз. При выключении питания конфигурация теряется. Каждый раз при включении питания необходим процесс инициализации (конфигурирования) схемы - загрузка данных из энергонезависимой памяти [1].

ИС класса ПЛМ и ПМЛ имеющие структуру весьма удобную для построения цифровых автоматов положили начало развития архитектуры программируемых коммутируемых матричных блоков (ПКМБ), которые представляют собой ПЛИС содержащую несколько матричных логических блоков, объединённых коммутационной матрицей. ПЛИС типа ПКМБ, как правило, имеют высокую степень интеграции (до 10 тыс. эквивалентных вентилей). К этому классу относятся ПЛИС семейства MAX5000, MAX7000 фирмы Altera, схемы XC7000, XC9500 фирмы Xilinx и др. ПЛИС класса ПКМБ в зарубежной литературе получили название CPLD (Complex PLD).

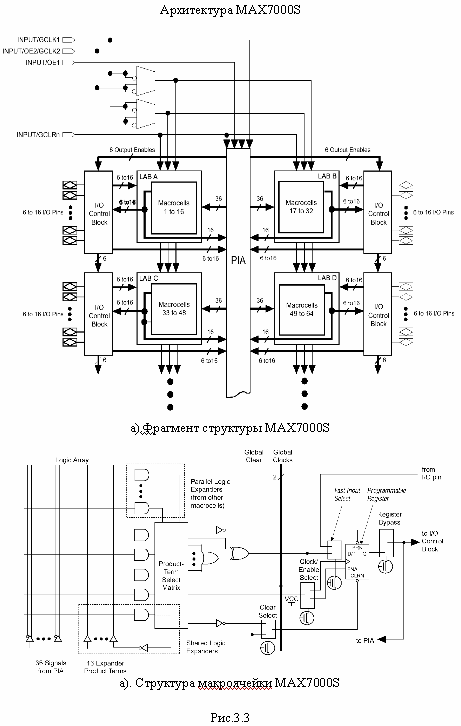

Архитектурно CPLD состоят из центральной коммутационной матрицы, множества функциональных блоков ФБ (макроячеек) и блоков ввода-вывода на периферии кристалла. Система коммутации построена на основе непрерывных связей, что даёт хорошую предсказуемость задержек сигналов в связях. Программируемая матрица соединений (PIA) позволяет соединить выход любого ЛБ с входами других и обеспечить связи с вертикальными и горизонтальными линиями. Как и во всех ПЛИС, логические операции производятся в ЛБ, которые соединяются в единую систему с помощью ПМС. Каждый ЛБ содержит 16 макроячеек. Классическим представителем CPLD являются микросхемы семейства MAX7000, фирмы Altera, имеющими память конфигурации типа EEPROM. В настоящее время выпускаются ПЛИС MAX7000, MAX7000A, MAX7000B, MAX7000E, MAX7000S. Семейства MAX7000A и MAX7000B рассчитаны на работу в системах с напряжением питания 3,3 и 2,5В соответственно, ПЛИС MAX7000S является дальнейшим развитием 5-вольтового MAX7000, с возможностью программирования в системе (ISP, In-system programmability) и периферийного сканирования в соответствии со стандартом IEEE Std. 1194.1 JTAG. Фрагмент структуры CPLD MAX7000S дающий достаточно полное представление о ней изображён на рисунке 3.3а.

В отличие от архитектуры MAX7000 ПЛИС MAX7000S имеют дополнительную возможность использования двух глобальных тактовых сигналов GCLK1 и GCLK2 и сброса GCLR, а также сигналы разрешения выходов ОЕ.

Логический блок обеспечивает построение как комбинационных цепей, так и схем с элементами памяти. Одна из макроячеек логического блока изображена на рисунке 3.3б.

При недостатке собственных термов внутри макроячейки, можно воспользоваться дополнительными ресурсами двух типов логических расширителей общего (разделяемого) и параллельного.

Блок ввода-вывода даёт возможность гибкого управления разрешением выходного буфера. ПМС формирует глобальные сигналы разрешения выходов ОЕ, допуская возможность перевода выходов ПЛИС в третье состояние. ПЛИС MAX7000S поддерживают аппаратную эмуляцию выходов с открытым коллектором, кроме того, может программироваться и скорость изменения выходов сигналов с целью предупреждения возможных паразитных колебаний при переключении.

Продолжением линии БМК стали программируемые пользователем вентильные матрицы ППВМ (FPGA). Логические блоки таких ПЛИС состоят из одного или нескольких относительно простых логических элементов (коммутируемых логических блоков КЛБ), в основе которых лежит таблица перекодировки, программируемый мультиплексор, D-триггер и цепи управления. Таких простых элементов может быть достаточно большое количество (у современных ПЛИС ёмкостью до 1 миллиона вентилей число логических элементов достигает нескольких десятков тысяч). Таким образом, архитектуру ППВМ можно представить в виде структуры БМК, где вместо базовых ячеек находятся КЛБ. В английской терминологии данный класс микросхем называется FPGA (Field Programmable Gate Array). К наиболее известным FPGA относятся ПЛИС семейства XC2000, XC3000, XC4000, XC5000 и Spartan, Virtex фирмы Xilinx, ACT1,ACT2 фирмы Actel, а также семейства FLEX8000 фирмы Altera, некоторые ПЛИС Atmel и Vantis [8].

В качестве КЛБ могут использоваться:

- транзисторные пары, простые логические вентили и т.п.

- логические модули на основе мультиплексоров

- логические модули на основе программируемых ПЗУ

Наиболее важные характеристики КЛБ отражаются двумя параметрами зернистость и функциональность.

Первое свойство связано с тем, какие минимальные единицы логики (транзистор, вентиль, логический модуль) можно применить для составления нужной схемы. Второе свойство показывает насколько велики логические возможности КЛБ. Т.о. оба параметра взаимопротивоположны. Мелкозернистые ЛБ фирмы Crosspoint Solution содержат цепочки транзисторов. Между цепочками транзисторов имеются трассировочные каналы, в которых могут быть реализованы необходимые межсоединения. Крупнозернистый блок в микросхемах XC4000E фирмы Xilinx в качестве основы имеет три функциональных логических преобразователя, ряд программируемых мультиплексоров и два триггера. Такой блок способен реализовать более сложные функции, что ведёт к упрощению программируемой части межсоединений. Иными словами, меняя зернистость можно выиграть в одном и проиграть в другом.

Системы межсоединений, как и логические блоки, реализуются в широком диапазоне архитектурных и технологических решений. Линии связи в FPGA как правило сегментированы, т.е. составлены из сегментов различной длины, соединённых программируемыми связями.

Короткие сегменты затрудняют реализацию длинных связей, длинные – коротких. Поэтому применяют иерархическую систему связей с несколькими типами межсоединений для передачи на разные расстояния, такое решение позволяет строить системы с максимальной коммутируемостью КЛБ при минимальном количестве ключей и задержки сигналов, а также предсказуемость последних, что облегчает программирование [7].

Критерий трассировочной способности системы межсоединений отображает возможность создания в FPGA множества схем типового применения (только с помощью программируемых перемычек).

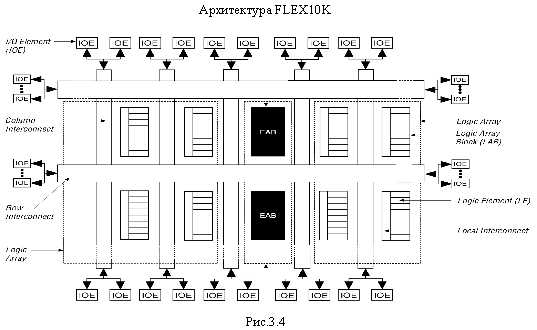

Объединение достоинств FPGA и CPLD привело к созданию ПЛИС смешанной архитектуры (общего названия для этого типа ПЛИС пока не придумано, фирма Altera пользуется термином Field Programmable Gate Arrays FLEX). Микросхемы FLEX содержат реконфигурируемые модули памяти РМП. Впервые такая встроенная память появилась в семействе FLEX

10K [7] (рис.3.4).

Логические элементы (ЛЭ) объединяются в группы – логические блоки. Внутри логических блоков ЛЭ соединяются посредством глобальной программируемой матрицы соединений. Локальная и глобальная матрицы соединений имеют непрерывную структуру – для каждого соединения выделяется непрерывный канал.

Дальнейшее развитие архитектур идёт по пути создания комбинированных архитектур, сочетающих удобство реализации оперативно реконфигурируемых систем, характерных для FPGA структур и многоуровневых ПЛИС с удобством реализации цифровых автоматов на CPLD архитектурах. В продукции наиболее известных производителей ПЛИС можно выделить микросхемы APEX 20K/KE (рис.3.5) фирмы Altera и Virtex фирмы Xilinx. Стоит отметить, что при всех своих достоинствах такие ПЛИС пока мало популярны из-за высокой стоимости [7].

В таких микросхемах уровень интеграции доведён до нескольких миллионов эквивалентных вентилей, а быстродействие до тактовых частот 500…600 МГц. На таких кристаллах можно поместить целую систему (в зарубежной литературе принят термин System-On-Chip, SOC), включающую процессорную часть, память, интерфейсные схемы и др.

Компоненты этих систем разрабатываются отдельно и хранятся в виде файлов параметризованных модулей. На базе таких виртуальных компонентов с помощью систем автоматизированного проектирования электронных устройств EDA (Electronic Design Automation) создаётся окончательная структура SOC-микросхем.

3.2 Методы и средства проектирования устройств с программируемой логикойХарактер проектирования существенно зависит от вида применяемой элементной базы. Небольшие устройства для реализации которых используются ПЛИС малой степени интеграции разрабатываются, как правило «вручную», когда проектирование сводится к построению таблицы программирования (прошивки), на основании которой обеспечиваются необходимые межсоединения.

Все современные методики проектирования ЦУ на базе схем программируемой логики высокой сложности основаны на применении САПР. Новейшие САПР предоставляют широкий набор инструменты для проектирования на этапах описания, компиляции, отладки, функционального и временного моделирования, конфигурирования, физического моделирования и программирования [7].

В настоящее время к наиболее распространенным универсальным способам описания, применимым для проектов любого уровня относят графический и текстовый. Реже используются непосредственная разводка схем в редакторе топологии, описания в виде требуемых временных диаграмм, а также описания путём построения графов.

Графический способ разработки дизайна подразумевает макетное построение схемы с использованием библиотечных элементов САПР, которые могут быть представлены в виде примитивов, в виде макрофункций в базисе элементов стандартных серий ТТЛ(Ш) или в виде параметризованных модулей. Главное достоинство графического способа – его традиционность и наглядность.

Использование текстового представления проекта допускает описание устройства, как с точки зрения поведения, так и с точки зрения структуры. Удобство текстового описания проявляется при создании систем, содержащих большое количество повторяющих фрагментов. Важными достоинствами являются текстового описания компактность и относительная простота автоматизации любых преобразований, включая начальную генерацию описания проекта.

Использование стандартных универсальных языков описания аппаратуры (HDL, Hardware Description Languages) обеспечивает простоту переноса проекта с одной аппаратной платформы на другую и переход от одной САПР к другой [7]. Текстовые описания имеют две основные разновидности – языки низкого уровня (аналоги языков программирования типа ассемблера) и высокого уровня. Примерами таких языков могут служить язык AHDL (Altera HDL) и ABEL (фирмы Xilinx). Языки высокого уровня менее связаны с аппаратными платформами и поэтому более универсальны. Среди них наиболее распространены языки VHDL и Verilog [7].

Описание в виде граф-схемы переходов (диаграммы состояний) является наиболее распространённым вариантом задания цифровых автоматов. Графические редакторы для создания автоматов включаются в состав средств задания исходных проектов современных САПР (например, в САПР Foundation фирмы Xilinx разработки фирмы ALDEC).

После составления описания проекта производится его компиляция. Данная процедура разбивается на ряд последовательных действий: сборка базы данных проекта, контроль соединений, логическая минимизация проекта, формирование загрузочного (конфигурационного) файла и др. Результат компиляции – загрузочный файл.

Тестирования проекта часто производится путём работы с редактором временных диаграмм. В данном варианте анализ производится на основе созданного генератора воздействия. Например в САПР MAX+PLUS II предусмотрено автоматическое вычисление трёх основных классов временных параметров:

- минимальных и максимальных задержек между источниками (входными сигналами) и приёмниками (выходными сигналами), информация о которых выдаётся в виде матрицы задержек;

- максимально возможной производительности устройства (пропускной способности) в виде максимальной частоты тактирования элементов памяти, используемых в проекте.

- времён предустановки и выдержки сигналов, гарантирующих надёжную работу схем при фиксации сигналов в синхронных элементах памяти [7].

Многие САПР позволяют также выделять критические пути передачи и преобразования информации для схемного или топологического представления проекта.

При выборе той или иной элементной базы не маловажным критерием является наличие достаточно развитых и удобных средств разработки проектов на её основе.

Ряд фирм предлагает бесплатные версии САПР, представляющих собой базовый набор инструментов для проектирования ЦУ на базе ПЛИС. Примерами могут служить САПР MAX+PLUS II BASELINE – среда проектирования устройств на базе ПЛИС фирмы Altera, WebPACK ISE – версия САПР для ПЛИС фирмы Xilinx. Среди бесплатных САПР Xilinx следует также выделить систему WebFITTER, первый в своем роде продукт, основанный на использовании Internet.

Многие крупные фирмы-производители САПР интегральных схем активно включились в процесс создания программного обеспечения, поддерживающего ПЛИС различных производителей. Это позволяет проводить разработку алгоритмов, пригодных к реализации на ПЛИС не только разных семейств, но и различных производителей, что облегчает переносимость алгоритма и ускоряет процесс разработки. Примером таких систем являются продукты серии FPGA Express фирмы Synopsys, OrCAD Express фирмы OrCAD, продукты фирм VeryBest, Aldec, Cadence Design Systems и многих других. САПР фирмы Altera поддерживает интерфейс со многими из названных продуктов.

3.3 САПР MAX+PLUS II

Система MAX+PLUS II разработана фирмой Altera и обеспечивает многоплатформенную архитектурно независимую среду создания дизайна, легко приспосабливаемую для конкретных требований пользователя.

Название MAX+PLUS II является аббревиатурой от Multiple Array MatriX Programmable Logic User System (пользовательская система программирования логики упорядоченных структур). Система MAX+PLUS II имеет полный спектр возможностей логического дизайна: разнообразные средства описания проектов с иерархической структурой, мощный логический синтез, компиляцию с заданными временными параметрами, разделение на части (использование нескольких кристаллов), функциональное и временное тестирование (симуляцию), тестирование нескольких связанных устройств, анализ временных параметров системы, автоматическую локализацию ошибок, а также программирование и верификацию устройств [8]. Процедуру разработки нового проекта от концепции до завершения можно упрощённо представить следующим образом:

1) создание нового файла проекта или иерархической структуры нескольких файлов проекта с помощью любого сочетания редакторов в системе MAX+PLUS II, то есть графического, текстового и сигнального редакторов;

2) задание имени файла - проекта верхнего уровня в качестве имени проекта;

3) назначение семейства ПЛИС для проекта;

4) компиляция проекта. По желанию пользователя можно подключить модуль извлечения временных параметров проекта Timing SNF Extractor для создания файла, используемого при временном моделировании;

5) в случае успешной компиляции возможен временной анализ в окне Timing Analyzer и симуляция в окне Simulator

6) программирование с использованием программатора MPU (Master Programming Unit) или подключение загрузочных устройств BitBlaster, Byte-Blaster или FLEX Download Cable к устройству, программируемому в системе;

ПО системы MAX+PLUS II содержит 11 приложений и главную управляющую программу. Различные приложения, обеспечивающие создание проекта, могут быть активизированы мгновенно, что позволяет пользователю переключаться между ними щелчком мыши или с помощью команд меню. В это же время может работать одно из фоновых приложений, например, компилятор, симулятор, анализатор синхронизации и программатор. Одни и те же команды разных приложений работают одинаково, что облегчает задачу разработки логического дизайна.

В таблице 1 приведено краткое описание приложений.

В САПР MAX+PLUS II легко доступны все инструменты для создания проекта. Разработка проекта ускоряется за счёт имеющихся стандартных функций, в том числе примитивов, мегафункций, библиотеки параметризованных модулей (LPM) и макрофункций устаревшего типа микросхем 74 серии.

Таблица 1 Приложения системы MAX+PLUS II.

| Приложение | Выполняемая функция |

| Hierarchy Display | Обзор иерархии - отображает текущую иерархическую структуру файлов в виде дерева с ветвями, представляющими собой подпроекты. |

| Graphic Editor | Графический редактор - позволяет разрабатывать схемный логический проект в формате реального отображения на экране WYSIWYG. |

| Symbol Editor | Символьный редактор - позволяет редактировать существующие символы и создавать новые. |

| Text Editor | Текстовый редактор - позволяет создавать и редактировать текстовые файлы логического дизайна, написанные на языках AHDL, VHDL, Verilog HDL. |

| Waveform Editor | Сигнальный редактор - выполняет двойную функцию: инструмент для разработки дизайна и инструмент для ввода тестовых векторов и наблюдения результатов тестирования. |

| Floorplan Editor | Поуровневый планировщик - позволяет графическими средствами делать назначения контактам устройства и ресурсов логических элементов. |

| Compiler | Компилятор - обрабатывает логические проекты. |

| Simulator | Симулятор - позволяет тестировать логические операции и внутреннюю синхронизацию проектируемой логической цепи. |

| Timing Analyzer | Временной анализатор - анализирует работу проектируемой логической цепи после того, как она была синтезирована и оптимизирована компилятором. |

| Programmer | Программатор - позволяет программировать, конфигурировать, проводить верификацию и тестировать ПЛИС фирмы ALTERA. |

| Message Processor | Генератор сообщений - выдает сообщения об ошибках, предупреждающие и информационные сообщения. |

В системе MAX+PLUS II есть три редактора для разработки проекта: графический, текстовый и сигнальный, а также два вспомогательных редактора: поуровневый планировщик и символьный редактор.

Графический редактор (Graphic Editor) обеспечивает проектирование в реальном формате изображения (WYSIWIG). Графические файлы проекта (.gdf) или схемные файлы OrCAD (.sch), созданные в данном графическом редакторе, могут включать любую комбинацию символов примитивов, мегафункций и макрофункций. Символы могут представлять собой любой тип файла проекта (.gdf .sch .tdf .vhd .v .wdf .edf .xnf .adf .smf).

Символьный редактор (Symbol Editor) позволяет просматривать, создавать и редактировать символ. Символьный файл имеет то же имя, что и проект, и расширение “.sym”. Команда Creat Default Symbol меню File, которая есть в графическом, текстовом и сигнальном редакторах, создает символ для любого файла проекта. Символьный редактор обладает следующими характеристиками: можно переопределить символ, представляющий файл проекта, создавать и редактировать выводы и их имена, используя входные, выходные и двунаправленные выводы, а также задавать варианты ввода символа в файл графического редактора, задать значения параметров и их значения по умолчанию; сетка и направляющие помогают выполнить точное выравнивание объектов, в символе можно вводить комментарии.

Текстовый редактор (Text Editor) является инструментом для создания текстовых файлов проекта на языках описания аппаратуры: AHDL (.tdf), VHDL (.vhd), Verilog HDL (.v). Все перечисленные файлы проекта можно создавать в любом текстовом редакторе, однако данный редактор имеет встроенные возможности ввода файлов проекта, их компиляции и отладки с выдачей сообщений об ошибках и их локализацией в исходном тексте или в тексте вспомогательных файлов; кроме того, существуют шаблоны языковых конструкций для AHDL, VHDL и Verilog HDL, выполнено окрашивание синтаксических конструкций. В данном редакторе можно вручную редактировать файлы назначений и конфигурации (.acf), а также делать установки конфигурации для компилятора, симулятора и временного анализатора.

Пользуясь данным текстовым редактором, можно создавать тестовые векторы (.vec), используемые для тестирования, отладки функций и при вводе сигнального проекта. Можно также создавать командные файлы (.cmd — для симулятора и .edc — для EDIF), а также макробиблиотеки (.lmf).

Сигнальный редактор (Waveform Editor) служит инструментом создания описания проекта, ввода тестовых векторов и просмотра результатов тестирования. Пользователь может создавать сигнальные файлы проекта (.wdf), которые содержат временные диаграммы, описывающие логику работы проекта, а также файлы каналов тестирования (.scf), которые содержат входные вектора для тестирования и функциональной отладки. Разработка описания проекта в сигнальном редакторе является альтернативой его создания в графическом или текстовом редакторах. Здесь можно графическим способом задавать комбинации входных логических уровней и требуемых выходов. Созданный таким образом файл WDF может содержать как логические входы, так и входы цифрового автомата, а также выходы комбинаторной логики, счётчиков и цифровых автоматов. Способ разработки дизайна в сигнальном редакторе лучше подходит для цепей с чётко определёнными последовательными входами и выходами, то есть для цифровых автоматов, счётчиков и регистров.

Поуровневый планировщик (Floorplan Editor) предназначен для назначения ресурсов физических устройств и просмотра результатов разводки, сделанных компилятором. В окне поуровневого планировщика могут быть представлены два типа изображения:

- Device View (Вид устройства) показывает все контакты устройства и их функции;

- LAB View (Вид логического структурного блока) показывает внутреннюю часть устройства, в том числе все логические структурные блоки (LAB) и отдельные логические элементы.

После выполнения всех назначений и задания проекта приступают к его компиляции. Сначала компилятор извлекает информацию об иерархических связях между файлами проекта и проверяет проект на простые ошибки ввода описания проекта.

Компилятор применяет разнообразные способы увеличения эффективности проекта и минимизации использования ресурсов устройства. Если проект слишком большой, чтобы быть реализованным в одном устройстве, компилятор может автоматически разбить его на части для реализации в нескольких устройствах того же самого семейства, при этом число соединений между устройствами минимизируется. В файле отчёта (.rpt) затем будет отражено, как проект будет реализован в одном или нескольких устройствах.

Кроме того, компилятор создает программирующие файлы, используемые программатором для программирования одного или нескольких устройств. У разработчика также есть возможность настроить обработку проекта. Например, можно задать стиль логического синтеза проекта по умолчанию и другие параметры логического синтеза в рамках всего проекта. Кроме того, можно ввести требования по синхронизации в рамках всего проекта, точно задать разбиение большого проекта на части для реализации в нескольких устройствах и выбрать варианты параметров устройств, которые будут применены для всего проекта в целом. Загрузку готового проекта в ПЛИС или конфигурационное ПЗУ выполняют с помощью программатора (Programmer).

4. ПОИСК СХЕМОТЕХНИЧЕСКИХ РЕШЕНИЙ

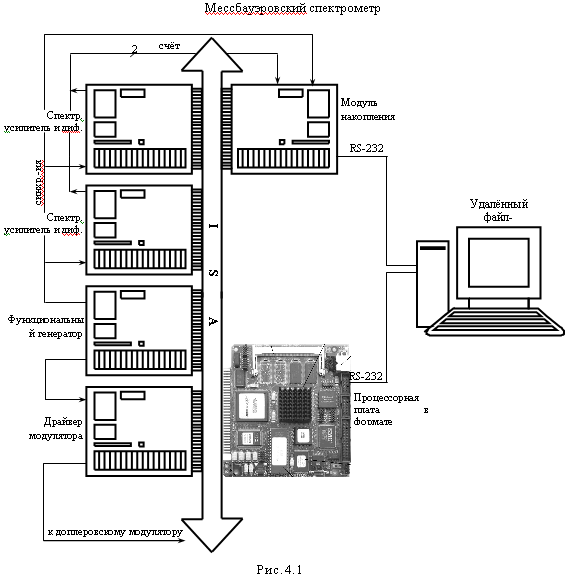

Модульный принцип построения системы накопления подразумевает создание набора встраиваемых плат расширения для персонального компьютера либо систем стандарта микро-PC с магистралью ISA. Развивая и усовершенствуя весь мессбауэровский спектрометр возможно создание полноценного автоматизированного комплекса с реализацией всех узлов электронного блока спектрометра в виде модулей (рис.4.1).

Модульность системы накопления даёт возможность оперативно менять конфигурацию. Путём добавления необходимого числа модулей можно выстроить систему независимых спектрометрических трактов. Таким образом, модульная концепция системы накопления – есть средство реализации многоканальности.

Система, удовлетворяющая многомерным задачам мессбауэровской спектрометрии должна укладываться в критерии многоканальности. Т.е. аппаратура для многомерных задач должна быть также модульной.

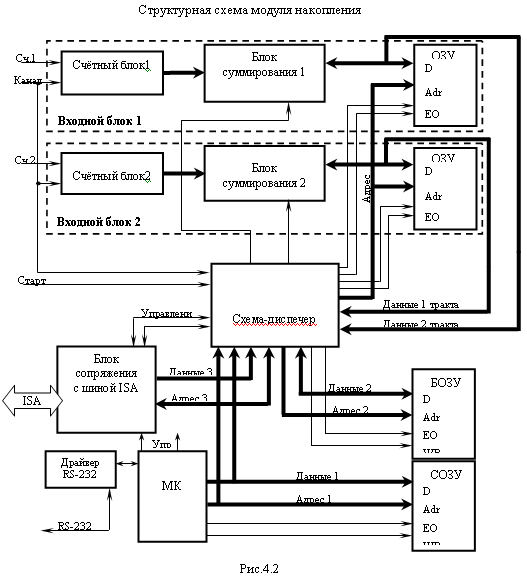

Суммируя вышеперечисленные условия (и ряд других) наиболее удобным представляется построение модуля накопления с возможностью сбора данных от двух синхронных трактов регистрации и накопления 24-битного результата. Такой модуль можно успешно применять для снятия данных в многомерных гамма-оптических схемах эксперимента в составе многоканальной системы накопления.

Схема модуля накопления должна содержать микроконтроллер. Это связано, прежде всего, с тем, что модуль накопления является оператором данных большой разрядности (24 бит) и необходимо построить систему с максимально упрощённым алгоритмом доступа к банку данных со стороны магистрали ISA. Другое дело задача об оптимальном (по ряду критериев) распределении функций между аппаратурными средствами и программным обеспечением. При этом в самом общем случае необходимо исходить из того, что перенесение всех функций на аппаратурные средства обеспечивает высокое быстродействие системы в целом, но приводит к значительному усложнению схемы и сопряжено с увеличением стоимости конечного изделия. Кроме того, в данном случае исчезает возможность создания автономной системы. Бóльший удельный вес программного обеспечения позволяет сократить сложность аппаратурных средств, но это приводит к снижению быстродействия и увеличению затрат и сроков разработки и отладки прикладных программ. Время жизни изделия, в котором большая часть функций реализована в программном обеспечении, многократно возрастает за счет того, что срок "морального старения" изделия может быть существенно отодвинут путём совершенствования и перестроения программного обеспечения. Программная реализация основных элементов алгоритма работы накопителя допускает его модификацию относительно простыми средствами. Это и есть главный критерий построения гибких реконфигурируемых систем.

Учитывая широкие возможности микроконтроллера по работе с памятью, предполагается использование его системного ОЗУ (СОЗУ) для хранения и накопления спектрометрических данных. Объём СОЗУ должен быть достаточным для хранения банка 2х24х4096 бит, а также промежуточных данных. Наибольшие скоростные требования предъявляются к той части схемы, где реализуется алгоритм накопления первого байта (счётные блоки, блоки суммирования и т.д.), поэтому данная часть должна быть исполнена аппаратно с использованием быстрой статической памяти. Накопление старших байтов можно производить с использованием программных средств микроконтроллера. Из всех рассмотренных ранее способов обмена с компьютером наиболее подходящим является применение разделяемой памяти. В этом случае трансляция накопленных в СОЗУ данных должна производиться с использованием буферного ОЗУ доступного как со стороны шины ISA, так и со стороны микроконтроллера. Кроме того, БОЗУ может применяться для быстрого (в течение нерабочего режима системы регистрации, составляющего 11 мс) чтения данных собранных в системе накопления первого байта. Такой подход (совместно с другими положениями) позволяет организовать систему с непрерывным процессом накопления. Помимо ISA в качестве внешнего интерфейса может использоваться последовательный порт микроконтроллера (например, в случае автономной работы модуля накопления).

Преследуя принцип минимизации количества корпусов микросхем на малогабаритной плате необходимо предельно использовать возможности ПЛИС. Практически вся аппаратная часть, в том числе схема блока сопряжения, может быть реализована на одном кристалле ПЛИС. Использование наиболее популярных серий ПЛИС с доступными средствами автоматизированного проектирования позволяет строить надёжные устройства при помощи современных методов моделирования на функциональном и физическом уровне. Предлагаемый модуль накопления содержит два входных блока осуществляющих накопление данных первого байта. Каждый блок, в свою очередь, состоит из счётного блока и схемы промежуточного хранения (рис.4.2).

Использование буферного ОЗУ позволяет построить следующий алгоритм работы устройств на схеме модуля накопления. С приходом стартового импульса начинается очередной цикл регистрации данных. Входные импульсы с двух трактов регистрации поступают на входы счётных блоков 1 и 2, где производится их подсчёт за время равное периоду следования канальных импульсов системы регистрации.

По приходу очередного канального импульса происходит выдача данных на входы блоков суммирования и обнуление счётчиков для импульсов следующего временного окна. В тоже время блок выработки адреса схемы-диспетчера осуществляет выборку данных в ячейках ОЗУ соответствующих очередному номеру импульса «Канал». Блоки суммирования производят их сложение с данными, поступившими со счётных блоков. Результаты сложения возвращаются в ОЗУ по тому же адресу.

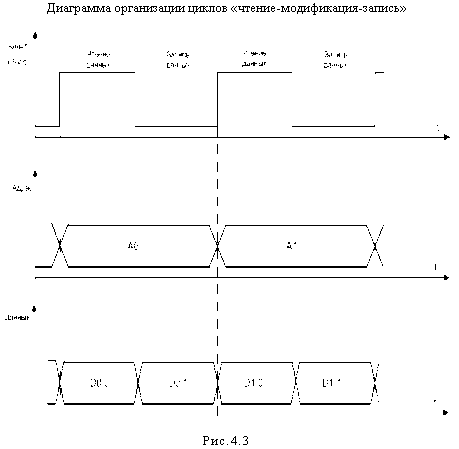

Так продолжается накопление данных в 4096 каналов после чего следует период нерабочего состояния системы регистрации длительностью 11 мс. За это время может быть произведена быстрая автоматическая трансляция в буферное ОЗУ данных накопленных в ОЗУ1 или ОЗУ2. Процесс передачи данных не обязательно должен производится в конце каждого цикла регистрации. Периодичность обмена определяется степенью загрузки трактов. Даже при высоких параметрах загрузки порядка 106 имп./с чтение ОЗУ необходимо производить в конце каждого десятого цикла регистрации. Таким образом работа с данными в накопительных ОЗУ (ОЗУ1 и ОЗУ2) производится по принципу «чтение-модификация-запись» (рис.4.3) Это относится и к режиму накопления и к режиму автоматической трансляции. В последнем случае на место прочитанных и переданных в буферное ОЗУ данных записывается нуль.

Данные, переданные в буферное ОЗУ, находятся в распоряжении микроконтроллера, который, выполняя подпрограмму суммирования, производит накопление трёхбайтного массива данных в системном ОЗУ.

Результат накопления спектров первого и второго тракта хранятся в системном ОЗУ и могут быть по запросу переданы на шину ISA. Передача данных производится блоками по 4 К байт с использованием буферного ОЗУ доступного со стороны ISA. Компьютер либо другая управляющая система (host) передают команды управления (запросы на доступ к банку данных, параметры накопления) используя либо буферное ОЗУ, либо последовательный порт с протоколом RS-232, либо регистры доступные со стороны магистрали ISA в поле адресов устройств ввода-вывода.

5. РАСЧЁТНАЯ ЧАСТЬ

При разработке модуля накопления необходимо исходить из принципа максимальной простоты эксплуатации. С этой точки зрения схема должна позволять осуществлять программирование микроконтроллера, как инструмента накопления данных и управления ресурсами, с учётом необходимой и достаточной степени доступа к конечной аппаратуре.

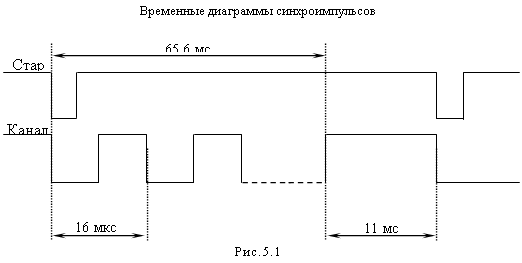

Модуль накопления для задач многомерной мессбауэровской спектрометрии спроектирован с учётом следующих условий:

- Синхронизация накопителя с системой доплеровской модуляции осуществляется внешними тактовыми импульсами “старт” и “канал”, имеющими стандартные ТТЛ уровни (рис.5.1).

- Основным внешним интерфейсом накопителя является магистраль ISA. Доступ к данным осуществляется в режиме разделяемой памяти с использованием буферного ОЗУ.

- Накопление мессбауэровского спектра осуществляется в режиме последовательного многоканального пересчета, при котором количество импульсов, подсчитанное за последовательные равные интервалы времени заносятся в последовательные каналы (ячейки памяти).

- Модуль производит подсчёт входных импульсов, накопление 24-разрядных данных в 4096 каналов и обеспечивает их хранение.

5.1 Разработка проекта на базе ПЛИСКак уже отмечалось, центральной и наиболее трудоёмкой частью разработки является проектирование ПЛИС. На кристалл размещены практически все функциональные блоки модуля накопления, за исключением микроконтроллера и элементов оперативной памяти.

За основу принята серия MAX7000S фирмы Altera – это ПЛИС класса CPLD с возможностью внутрисистемного программирования, и не требующих внешней памяти конфигурации.

Микросхемы семейства MAX7000 характеризуются высокими параметрами быстродействия: максимальная глобальная тактовая частота не ниже 125 МГц. Матрица соединений имеет непрерывную структуру, что позволяет реализовать время задержки распространения сигнала до 5 нс.

Разработка кристалла ПЛИС осуществлялась в системе проектирования MAX+PLUS II – до последнего времени единственной САПР для большинства ПЛИС фирмы Altera.

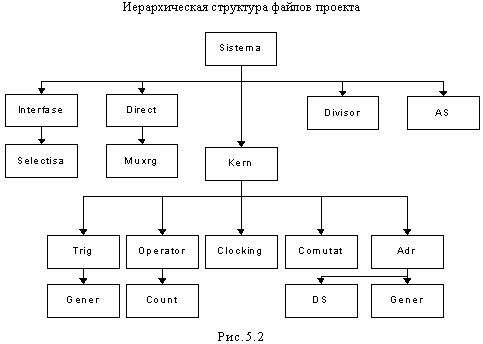

Дизайн проекта выполнен в виде иерархической структуры файлов созданных в графическом редакторе системы MAX+PLUS II (рис.5.2). Для тестирования, как отдельных узлов, так и всего проекта использовался сигнальный редактор.

Файлом верхнего уровня (файлом проекта) является файл Sistema.gdf. Этот файл обрабатывается компилятором. Он содержит логику проекта и выполнен в виде иерархической структуры. Структурное разделение в целом соответствует функциональному.

Блок схема отражает наличие лишь наиболее значимых частей (файлов) проекта. Так, например, в схеме часто используются элементы задержки, составленные из соответствующих примитивов MAX+PLUS II. Кроме того, при составлении схем применялись модули параметризованных функций, поставляемые фирмой Altera.

Основные функции работы модуля накопления реализованы в блоке Kern. Он содержит в себе операционный блок (Operator) в котором, совместно с внешними, относительно ПЛИС, элементами ОЗУ выполняется алгоритм накопления первого байта данных. Кроме того, блок Kern включает в себя схему выработки адреса ячеек ОЗУ (Adr), работающую в режиме последовательного пересчёта.

Сопряжение модуля накопления с магистралью ISA производится интерфейсным блоком (файл Interfase), содержащим дешифраторы линий адреса, узел выработки прерываний и регистры доступные в пространстве адресов устройств ввода-вывода компьютера.

Узел Direct используется для выработки сигналов управления доступом к буферному ОЗУ со стороны внешних устройств согласно, установленного микроконтроллером, режима работы, а также для выполнения некоторых интерфейсных функций.

На схеме присутствует несколько регистров доступных со стороны микроконтроллера и необходимых для управления. Для их адресации выделено три линии порта микроконтроллера (всего 8 адресов). Роль селектора адреса выполняет элемент AS.

5.1.1 Реализация основного алгоритмаВходные блоки модуля накопления выполняют накопление и промежуточное хранение данных первого (младшего) байта. Основными структурными элементами здесь являются счётные блоки, блоки суммирования, и накопительные ОЗУ. Адресация ячеек ОЗУ происходит синхронно канальным импульсам системы регистрации. Накопление происходит непрерывно в каждом цикле регистрации. Число каналов накопления может быть задано. В соответствии с алгоритмом программы микроконтроллера периодически (один раз за несколько циклов регистрации) должна происходить быстрая автоматическая трансляция данных одного из накопительных ОЗУ в буферное ОЗУ.

Описанный механизм реализуется в блоке Kern совместно с внешними микросхемами ОЗУ. В соответствующем схемном файле Kern.gdf объединены счётные блоки, блоки суммирования, адресный блок и необходимые схемы управления.

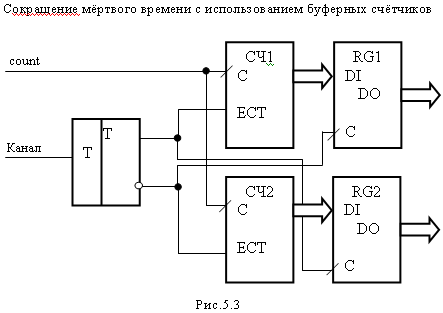

Для реализации счётного блока с минимальными значениями параметра мёртвого времени на канал используется схема, состоящая из двух буферных счётчиков. Переключение потока входных импульсов между счётчиками производится управляющим триггером синхронно канальным импульсам системы регистрации (рис.5.3).

В то время, когда один из счетчиков находится в режиме счета приходящих на его вход импульсов, данные со второго счетчика через регистр и далее через мультиплексор поступают в последующее устройство обработки информации. Таким образом, мертвое время на канал сокращается до значения равного времени переключения триггерной ячейки внутри ПЛИС. Быстродействие счетчиков характеризуется собственным значением мертвого времени, которое определяет время нечувствительности счетчика, возникающее после регистрации им входного импульса. Параметр регистровой (триггерной) задержки в ПЛИС серии MAX7000S не превышает 2 нс. Это позволяет говорить о том, что предельная входная загрузка может с многократным запасом превышать 107 имп./с.

Счётный блок реализован файлом Count.gdf в графическом редакторе системы MAX+PLUS II. При составлении схемы использованы параметризованные модули (LPM) счётчиков и регистров, а также другие примитивы для комбинационных и последовательных участков схемы. Схемный файл Count.gdf находится в ПРИЛОЖЕНИИ 2.

Суммирование выходных данных счётных блоков с данными ОЗУ выполняется в блоке и одноимённом файле Operator. На рисунке 5.4 представлена функциональная схема сложения данных для одного тракта регистрации. В Operator структурно входит два счётных блока, данные с которых, поступают на входы параметризованных модулей сумматоров. На второй вход сумматоров поступают данные ОЗУ, предварительно зафиксированные в регистрах. Фиксация в регистрах необходима для разделения во времени двунаправленных шин данных внешних микросхем ОЗУ.

Управление регистрами осуществляется от внешнего блока Clocking. Кроме указанных элементов на схеме присутствует логика управления и схема перевода выходов сумматоров в третье (высокоимпедансное) состояние.

Полный вариант схемы в виде файла Operator.gdf представлен в ПРИЛОЖЕНИИ 2.

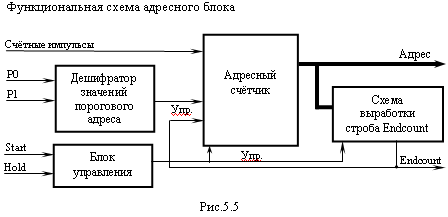

Выборка ячеек внешних микросхем ОЗУ производится адресным блоком, построенным в схемном файле Adr.gdf. Значение адреса генерируется 12-ти разрядным адресным счётчиком на вход, которого подаются, в зависимости от режима работы, канальные импульсы (в процессе накопления) либо тактовые импульсы с частотой 400 кГц (в режиме быстрой автоматической трансляции данных в буферное ОЗУ). Сброс адресного счетчика происходит по приходу стартового импульса схемы регистрации или по приходу сигнала Hold со стороны триггерного блока Trig. Сигнал Hold устанавливается в начале нерабочего режима системы регистрации в том случае, если микроконтроллер программно установил флаг запроса трансляции данных первого байта в буферное ОЗУ (рис.5.5)

Адресный счёт начинается с 000h. Последним на шину выдаётся пороговый адрес. Далее вырабатывается строб окончания счёта Endcount поступающий на вход триггерного блока. Значение порога для адресного счетчика может быть установлено микроконтроллером. Для этого используются дешифратор значений порогового адреса с входами установки P0 и P1. По умолчанию пороговым является адрес 4095 (FFFh), для нужд эксперимента программно могут быть установлены значения 2047 (7FFh), 1023 (3FF) и 511 (1FF).

Схемный файл адресного блока Adr.gdf находится в ПРИЛОЖЕНИИ 2.

В процессе автоматической трансляции данных в младшие 12 разрядов 13-ти разрядной шины адреса буферного ОЗУ подключается шина адреса накопительных ОЗУ. Сигнал Selram устанавливаемый микроконтроллером и формируемый триггерной схемой Trig определяет выбор микросхем ОЗУ1 или ОЗУ2 для передачи их данных в конце текущего цикла регистрации. Этот же сигнал подаётся на 13-й (старший) разряд шины адреса буферного ОЗУ. Таким образом происходит разделение пространства памяти буферного ОЗУ на два банка, каждый из которых предназначен для временного хранения данных ОЗУ1 и ОЗУ2.

Триггерная схема (файл Trig.gdf) выполняет роль набора регистров управления элементами блока Kern со стороны микроконтроллера. Схема построена из набора D-триггеров и дополнительных примитивов MAX+PLUS II. Непосредственно микроконтроллером устанавливаются сигналы P0, P1 и Selram. Управляющий сигнал Hold устанавливается через определённое время задержки в ответ на сигнал Endcount адресного блока и осуществляет перевод блока Kern и других вышестоящих узлов в режим работы с буферной памятью. Задержка необходима для завершения последней операции записи-чтения ячеек накопительных ОЗУ с пороговым адресом. Функция задержки реализована с использованием четырёхразрядного счётчика, тактируемого внешним сигналом Read.

Файл Trig.gdf графического редактора системы MAX+PLUS II находится в ПРИЛОЖЕНИИ 2.

Корректная работа с микросхемами быстрой статической оперативной памяти невозможна без стогового соблюдения протоколов обмена в соответствии с технической документацией.

Наиболее важным параметром статических ОЗУ является время выборки. Оно характеризует максимальную частоту операций чтения или записи. Современные микросхемы памяти имеют время выборки порядка 30 – 100 нс, что удовлетворяет требованиям проекта. Данный параметр является качественной характеристикой, но наряду с ним существуют и другие параметры, которые необходимо учитывать разработчику при проектировании систем использующих оперативную память. В частности к ним относятся:

- минимальное время удержания активного уровня сигнала CS (выбор кристалла);

- минимальное время удержания активного уровня сигнала WE (разрешение записи) в режиме записи данных;

- минимальное время удержания активного уровня сигнала ОЕ (разрешение выходов) в режиме чтения данных

- минимальное время подачи управляющего сигнала записи с момента установления данных в режиме записи

- минимальное время удержания данных на входах ОЗУ после снятия управляющего сигнала записи в режиме записи

- минимальное время подачи управляющего сигнала чтения с момента установления адреса в режиме чтения и др.

Помимо непосредственного соблюдения протокола обмена синхронных ОЗУ в модуле накопления, нужно учесть и другие особенности их применения. Наличие двунаправленной шины данных между блоками суммирования и микросхемами ОЗУ (рис.4.2) заставляет обратить особое внимание на необходимость правильного разделения во времени потоков данных. Речь идёт о недопустимости одновременного (даже кратковременного) наличия на разделяемой шине данных, двух источников сигналов. То есть между сигналами разрешающими выход данных со стороны двух присутствующих на шине устройств, работающих в режиме непрерывного обмена, должен быть определённый временной интервал.

Всего модуль накопления должен содержать 4 элемента ОЗУ: буферное ОЗУ объёмом 8 Кбайт, системное ОЗУ объёмом 32 Кбайт и два элемента ОЗУ для накопления данных первого байта (ОЗУ1 и ОЗУ2) с объёмом 4 Кбайт каждая. Выработка управляющих сигналов «чтение», «запись» для накопительных ОЗУ в режимах накопления и автоматической трансляции данных, а также сигнала «запись» для буферного ОЗУ в режиме трансляции, происходит в схеме тактирования Clocking (схемный файл Clocking.gdf).

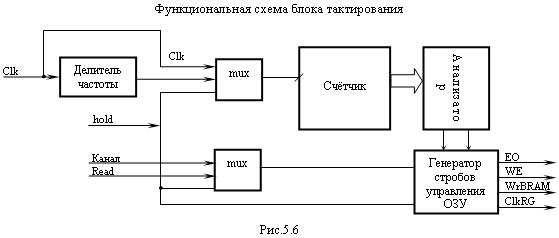

![]() Схема (блок) тактирования производит выдачу управляющих сигналов в соответствии с алгоритмом «чтение-модификация-запись» (рис.4.3) Для соблюдения требуемого протокола обмена, учитывающего все параметры, в схеме организована специальная сетка тактирования с использованием четырёхразрядного счётчика. Определённые выходные значения интерпретируются аналитической схемой как маркерные точки для своевременной установки или снятия сигналов OE, WE, CS микросхем накопительной памяти и сигнал WrBRAM микросхемы буферной памяти. Генератор управляющих стробов выдаёт указанные сигналы синхронно импульсам Canal или Read в соответствии с состоянием сигнала Hold, формируемого триггерной схемой. Помимо перечисленных сигналов блок тактирования генерирует строб приёма данных ClkRG для регистров операторного блока Operator. Положительный фронт сигнала ClkRG соответствует времени появления действительных данных на выходах накопительных ОЗУ.

Схема (блок) тактирования производит выдачу управляющих сигналов в соответствии с алгоритмом «чтение-модификация-запись» (рис.4.3) Для соблюдения требуемого протокола обмена, учитывающего все параметры, в схеме организована специальная сетка тактирования с использованием четырёхразрядного счётчика. Определённые выходные значения интерпретируются аналитической схемой как маркерные точки для своевременной установки или снятия сигналов OE, WE, CS микросхем накопительной памяти и сигнал WrBRAM микросхемы буферной памяти. Генератор управляющих стробов выдаёт указанные сигналы синхронно импульсам Canal или Read в соответствии с состоянием сигнала Hold, формируемого триггерной схемой. Помимо перечисленных сигналов блок тактирования генерирует строб приёма данных ClkRG для регистров операторного блока Operator. Положительный фронт сигнала ClkRG соответствует времени появления действительных данных на выходах накопительных ОЗУ.

Тактовый, меандровый сигнал с частотой 20 МГц подаётся на счётчик от внешнего, относительно ПЛИС генератора. В режиме накопления сигнал тактирования дополнительно проходит через делитель частоты на 5, выполненный на базе четырёхразрядного счётчика из набора макрофункций системыMAX+PLUS II.

Принцип работы блока тактирования отражён на функциональной схеме (рис.5.6).

Схемный файл блока тактирования Clocking.gdf находится в ПРИЛОЖЕНИИ 2.

Тестирование блока проведено в сигнальном редакторе системы MAX+PLUS II. В качестве входных тестовых векторов введены сигналы: сlk (сигнал тактирования частотой 20 МГц), сanal (канальные импульсы системы регистрации), read (сигнал тактирования режима быстрой трансляции) и hold (сигнал перевода в режим быстрой трансляции).

В режиме накопления блок тактирования генерирует сигналы управления eo (enable output) и write синхронно импульсам сanal, в режиме быстрой трансляции дополнительно генерируется сигнал записи буферного ОЗУ wrBRAM синхронно импульсам read. Результаты тестирования обоих режимов приведены на рисунке 5.7. Временные интервалы на диаграмме указаны в микросекундах.

Адресный блок вырабатывает значение адреса ячеек накопительного ОЗУ по отрицательному фронту импульса canal или read в зависимости от режима работы. Сигналы разрешения выходов формируются не ранее 120 нс. Выдача сигнала защёлкивания (чтения) данных в обоих случаях происходит не ранее чем через 200 нс после импульса ео. Послестояние данных при операциях записи ОЗУ составляет не менее 19 нс. Такие временные параметры призваны обеспечить устойчивую работу модуля накопления.

В режиме быстрой трансляции необходимо проводить запись нулевых байтов в ячейки накопительного ОЗУ, данные которых, уже перенесены в буферное ОЗУ.

За время нерабочего режима системы регистрации может быть произведена трансляция данных только одной из микросхем накопительного ОЗУ (в соответствии со значением сигнала Selram). При этом незанятое накопительное ОЗУ должно находится в режиме хранения данных.

Таким образом, необходимо обеспечить раздельную выдачу команд управления (EO, WR) для каждого накопительного ОЗУ.

Функции разделения команд, а также дополнительные функции выдачи сигналов обнуления на формирователи шин данных накопительных ОЗУ реализованы в блоке формирования Form. Соответствующий схемный файл Form.gdf графического редактора MAX+PLUS II находится в приложении 2.

Помимо рассмотренных устройств, в блоке Kern присутствуют дополнительные элементы, не включённые ни в один внутриструктурный файл этого блока. К ним относятся схема формирователя шины данных для буферного ОЗУ, управляемая сигналами hold и Selram, и триггер разрешения счёта импульсов от внешних трактов регистрации.

Триггер разрешения счёта должен использоваться для работы модуля в режиме снятия амплитудных спектров, для запуска счёта на очередном этапе сканирования.

Файл Kern.gdf графического редактора системы MAX+PLUS II находится в приложении 2.

5.1.2 Связь с внешними устройствамиНаличие буферной памяти, как средства взаимодействия нескольких источников и приёмников данных, требует построения соответствующей системы управления разделяемым ресурсом. Основным устройством управления на схеме модуля накопления является микроконтроллер. Выполняя программу накопления данных, он должен постоянно отслеживать и задавать режимы использования буферного ОЗУ. Всего предполагается 3 режима использования БОЗУ:

- запись-чтение данных со стороны микроконтроллера;

- запись-чтение данных со стороны магистрали ISA;

- запись данных из системы накопления первого байта.

Кроме контроля режимов работы БОЗУ микроконтроллер должен осуществлять конфигурирование и управление схемой, используя:

- триггер разрешения счёта входных импульсов;

- триггер флага трансляции данных в БОЗУ ( используемый для запуска сигнала hold в ближайшем нерабочем режиме системы регистрации);

- триггер выбора банка данных в пространстве БОЗУ;

- триггеры установки порогового адреса.

Алгоритм работы модуля накопления позволяет организовать попарную адресацию триггеров.

Для функций управления предполагается использовать один 8-битный порт микроконтроллера. В этом случае удобно построить двухразрядную шину данных и трёхразрядную шину адреса. Один бит порта необходимо использовать для стробирования данных.

Элементы входящие в систему управления реализованы в ПЛИС.

Обработка адресных линий микроконтроллера производится адресным селектором, выполненным в виде файла Asmc.gdf. По приходу положительного фронта тактирующего сигнала «с» микроконтроллера на выходах селектора формируются стробы защёлкивания данных с линий Dmc0 и Dmc1 для соответствующих пар триггеров. Распределение адресов устройств представлено в таблице 2.

Таблица 2 Распределение адресов регистров управления

| Адрес Бит данных | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

| Dmc0 | Установка значений порогового адреса 00 – 511 01–1023 10–2047 11–4095 | Установка флага hold (выдача в БОЗУ данных 1-го байта) | Установка режимов использования БОЗУ 00 – МК 01 – ISA 10 – система накопления 1-го байта | триггер разрешения счёта | Флаги в поле адресов ввода-вывода | Резерв | Резерв | Резерв |

| Dmc1 | Установка сигнала Selram | триггер иницициализации запроса прерывания |

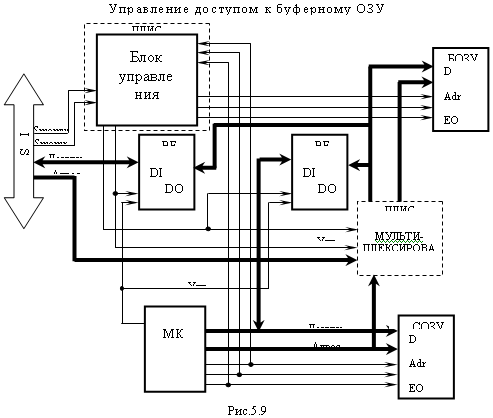

Адресный селектор выполнен в виде дешифратора. Схемный файл Asmc.gdf находится в ПРИЛОЖЕНИИ 2. Блок выдачи сигналов управления буферного ОЗУ (управляющий блок) выполнен в файле Direct.gdf. Блок выполняет мультиплексирование входящих сигнальных линий чтения и записи со стороны внешних устройств, исходя из состояния триггеров управления режимом использования БОЗУ (см. таблицу 2). Непосредственно триггеры установки режимов и мультиплексоры сигналов расположены во внутренней структуре в виде блока Muxrg.gdf. Помимо сигналов управления БОЗУ, управляющий блок генерирует сигналы разрешения выходов внешних двунаправленных шинных формирователей, обеспечивающих связь БОЗУ с микроконтроллером, а также с 8-битной шиной данных магистрали ISA. Те же сигналы используются для подключения внешних адресных линий заведённых через ПЛИС, к шине адреса БОЗУ (рис.5.9).

Схемные файлы Direct.gdf и Muxrg.gdf находятся в ПРИЛОЖЕНИИ.

Доступ к буферному ОЗУ со стороны магистрали ISA осуществляется по принципу разделяемой памяти. То есть ячейки буферного ОЗУ находятся в некотором поле адресов памяти компьютера. Для осуществления доступа требуется обработка всех 20 адресных линий шины ISA. 12 младших линий непосредственно адресуют ячейки БОЗУ, другие 8 используются для установки пространства памяти.

Интерфейсный блок Interfase выполняет обработку адресных линий и вырабатывает сигнал AdrE разрешения доступа к БОЗУ, поступающий на вход блока управления Direct.

Для осуществления быстрой связи между микроконтроллером и компьютером в интерфейсном блоке предусмотрено две пары триггеров. Триггера могут выполнять роль флагов, например, для выставления запроса на передачу накопленных данных в компьютер.

Для селектирования адресов пространства памяти, и триггеров расположенных в поле устройств ввода-вывода интерфейсный блок содержит схему дешифрации линий адреса Selectisa. Здесь можно задать селектируемые адреса путём добавления (удаления) примитивов логического отрицания NOT на входах соответствующих линий (см. файл Selectisa.gdf в ПРИЛОЖЕНИИ 2).

Микроконтроллер может инициализировать прерывание в компьютере установив специальный триггер в интерфейсном блоке. Обращение к буферному ОЗУ со стороны магистрали ISA расценивается, как реакция на прерывание и триггер сбрасывается.

Схемный файл Interfase.gdf находится в ПРИЛОЖЕНИИ 2.

Тактирование блока Kern осуществляется сигналами read и clk. Меандровый сигнал clk частотой 20 МГц поступает от внешнего кварцевого генератора на вход глобального тактового сигнала GCLK1 ПЛИС. Для получения меандрового сигнала read с частотой 400 кГц, на базе шестиразрядного счётчика и вспомогательной комбинационной схемы, построен делитель частоты Divisor. Его схема в виде файла Divisor.gdf представлена в ПРИЛОЖЕНИИ 2.

Структура, составленная из блоков Kern, Asmc, Direct, Interfase, Divisor и других элементов представляет собой единый проектный файл Sistema.gdf. Этот файл обрабатывается компилятором MAX+PLUS II, который создаёт загрузочный код для программирования ПЛИС. Проект Sistema может быть размещён на одном кристалле ПЛИС EPM7256SRC208-7 с логической ёмкостью 5000 эквивалентных вентилей. Из 256 макроячеек микросхемы использовано 251, что составляет 98% ёмкости.

5.2 Разработка принципиальной схемы модуля накопленияВ модуле накопления используется 8-битный микроконтроллер AT89c51 содержащий 4 Кб FLASH-памяти программ, 128 байт ОЗУ и содержащий 32 программируемые линии ввода-вывода. Линии ввода-вывода объединены в четыре 8-разрядных двунаправленных порта, два из которых используются в качестве шины адреса/данных для доступа к внешней памяти программ и данных. Один из портов имеет дополнительные функции (последовательный порт, входы внешних прерываний, входы счётчиков, выходы стробирующих сигналов записи-чтения во внешнюю память данных).

Использование внешней памяти программ не предполагается.

Накопление и хранение данных производится во внешней памяти данных объёмом 32 Кбайт. Для адресации необходимо 15 линий адреса. При обращении к внешнему ОЗУ младшие 8 разрядов адреса выдаются через порт P0, старшие 7 разрядов через порт Р2. Операции чтения-записи данных стробируются сигналами RD и WR микроконтроллера. Для мультиплексирования порта Р0 используется регистр фиксирующий адрес по спаду сигнала ALE. Регистр КР1533ИР23 производит запись по положительному фронту тактирующего сигнала, поэтому сигнал ALE инвертирован в ПЛИС.

Восьмой бит порта Р2 используется для обращения к буферному ОЗУ. При установке линии в лог.0 микроконтроллер обращается к БОЗУ, как к собственной памяти программ (естественно, что БОЗУ должно находится в режиме доступа микроконтроллера). Адресация происходит 12-ю младшими линиями адреса. На вход 13-го бита адреса с ПЛИС подаётся сигнал SelBANC, равный сигналу SelRAM, который устанавливается микроконтроллером (см. таблицу 1). Таким же образом задаётся 13-й бит адреса во всех других режимах использования БОЗУ.

Для управления внешними регистрами используется порт Р1. Два бита данных Dmc0 и Dmc1 выдаётся по линиям Р1.0 и Р1.1 (соответственно нулевой и первый бит порта). Трёхбитный адрес – по линиям Р1.2, Р1.3, Р1.4. Стробирование данных происходит положительным фронтом на линии Р1.5.

Направление передачи данных для шинных формирователей КР1533АП6, используемых для доступа к шине данных буферного ОЗУ со стороны микроконтроллера и магистрали ISA (рис. Ф), логическим уровнем на линии Р1.6 (1 – чтение данных БОЗУ, 0 – запись данных из БОЗУ).

На входы Р3.4, Р3.5 таймеров/счётчиков Т0 и Т1 микроконтроллера подаются соответственно сигналы Start и 7 функционального блока мессбауэровского спектрометра. На линию Р3.2 входа внешних прерываний INT0 подаётся сигнал INT интерфейсного блока выполненного внутри ПЛИС.

Модуль накопления имеет четыре ОЗУ: два ОЗУ объёмом 4 Кбайт в системе накопления первого байта, буферное ОЗУ объёмом 8 Кбайт и системное ОЗУ (внешняя память данных) микроконтроллера объёмом 32 Кбайт. Микросхемы ОЗУ с организацией 4Кх8 серийно не производятся, поэтому вместо них использованы более доступные – 8Кх8. Для корректной работы схемы модуля накопления достаточно оперативной памяти с временем выборки 100 нс.

Шины адреса и данных накопительных ОЗУ, шина адреса буферного ОЗУ, а также сигналы управления подключаются непосредственно к ПЛИС, где происходит установка их задатчика в зависимости от выбранного режима.

Для тактирования ПЛИС использована микросхема-кварц Z544-47, частотой 20 МГц.

Передача данных последовательного порта микроконтроллера происходит по средствам интерфейса обмена RS-232C. Для нормального приёма уровень передаваемых сигналов должен составлять не менее ±10 В. Применение дискретных элементов для построения приемопередатчика нежелательно и наиболее удобным является использование специализированных интерфейсных интегральных схем. Широкая гамма таких кристаллов выпускается фирмой Analog Devices. Они содержат преобразователь напряжения +5 В в напряжение +10 В, инвертор (преобразующий напряжение +10 В в –10 В) и собственно преобразователи уровня сигналов последовательного интерфейса. Для данного проекта использована микросхема ADM232A.

Перечень элементов принципиальной схемы приводится в ПРИЛОЖЕНИИ 4, характеристики – в ПРИЛОЖЕНИЯХ 5,6 и 7.

5.3 Блок-схема программного алгоритмаМикроконтроллер в схеме модуля накопления выполняет следующие основные функции:

- обеспечивает накопление и хранение в системном ОЗУ мессбауэровских спектров в виде 24-разрядных массивов данных;

- контролирует режим доступа к буферному ОЗУ;

- задаёт рабочие параметры модуля накопления;

- обеспечивает режим амплитудного анализа во взаимосвязи с управляющей системой.

Перед началом выполнения основной программы накопления микроконтроллер должен выполнить процедуру инициализации – произвести подготовку системы. Во-первых, необходимо обнулить ячейки памяти данных, и буферного ОЗУ, состояние которых является неопределенным после включения питания. Во-вторых, задать пороговый адрес (число каналов накопления). В-третьих, выдать команду разрешения счёта входных импульсов для счётных блоков в системе накопления первого байта.

Накопление спектрометрических данных должно осуществляться путём реализации алгоритма сложения массивов накопленных в системе накопления первого байта, и переданных в буферное ОЗУ, с данными, хранящимися и накапливаемыми в системном ОЗУ микроконтроллера. Трансляцию (передачу) данных накопленных в системе накопления первого (младшего) байта в буферное ОЗУ инициирует микроконтроллер путём установки флага hold. Выбор накопительного ОЗУ (1 или 2) для передачи осуществляется установкой сигнала Selram (см. таблицу 2). При высоких параметрах загрузки порядка 106 имп./с передачу данных первого байта в буферное ОЗУ необходимо производить в конце каждого десятого цикла регистрации.

Согласно установленной периодичности, либо по запросу данных со стороны задатчика шины ISA (при выставлении соответствующего флага или сигнала прерывания), микроконтроллер должен предоставить накопленные данные используя буферное ОЗУ, доступное задатчику ISA в режиме разделяемой памяти.

Блок-схема алгоритма программы микроконтроллера приводится в ПРИЛОЖЕНИИ 3.

6. БЕЗОПАСНОСТЬ И ЭКОЛОГИЧНОСТЬ 6.1 Характеристика рабочего места

В процессе дипломного проектирования была осуществлена разработка принципиальной схемы автономной системы накопления мессбауэровскго спектрометра. Работы, проводимые в помещении лаборатории мессбауэровской спектрометрии связаны с измерением гамма-резонансных спектров пропускания исследуемых веществ в твердом состоянии, содержащих стабильные нуклиды железо-57 и олово-119 в диапазоне температур 4,2K-1200K с использованием стационарно установленной Мессбауэровской лаборатории типа NE-255. Применяются источники гамма-излучения закрытого типа на радионуклидах кобальт-57 и олово-119М. При проектировании системы накопления использовался персональный компьютер.

В процессе проведения работ присутствуют следующие вредные и опасные факторы:

- ионизирующее излучение;

- повышенное напряжение электрического тока;

- воздействие электромагнитного излучения;

- воздействие шума;

- электростатические поля.

6.2 Безопасность труда 6.2.1 Радиационная безопасностьРаботы, проводимые в помещении лаборатории мессбауэровской спектрометрии, классифицируются как: "Дозиметрические и радиометрические измерения радиоактивных веществ и ионизирующих излучений, а также градуировка дозиметрической и радиометрической аппаратуры".