Навигация

Описание и анализ схемы электрической принципиальной

1.2 Описание и анализ схемы электрической принципиальной

Сигнал от первичных датчиков поступает через фильтр высокочастотных и импульсных помех на вход предварительного усилителя (ПУ), коэффициент передачи которого определяется положением ключей К5, К6 и равен 5 при замкнутом К5 (К6 разомкнут) и 1 при замкнутом К6 (К5 разомкнут). С выхода ПУ сигнал поступает на вход инвертирующего усилителя (ИУ), имеющего фиксированный коэффициент передачи равный 10. Выход ИУ через ключ К7 присоединяется к первому из входов интегратора (ИН). Ко второму входу ИН присоединяется источник опорного напряжения СИ через ключ К8. Параллельно интегрирующей ёмкости ИН присоединен трехступенчатый ключ К8. Параллельно интегрирующей ёмкости ИН присоединен трехступенчатый ключ К9-К11. Интегратор имеет три режима работы: интегрирования- замкнуты ключи К7 или К8 а также ключи К7,К8,К9,К10, замкнут ключ К11; обнуление- разомкнуты К7, К8, К11, замкнуты ключи К9, К10. Ключ К11 служит для компенсации утечки через разомкнутые ключи К9, К10 в режимах интегрирования и хранения.

Выход ИН через резистор подключен к входу компаратора (КМП), к этому же входу через другой резистор подключен СИ, создающий начальное смещение и сдвиг нулевого уровня характеристики АЦП. Выход КМП присоединяется к устройству логического управления (УЛУ) цифровой части АЦП.

Цифровая часть включает также формирователь временных интервалов (ФВИ), счетчик (СЧ), генератор (ГН), регистры управляющего слова (РГ)1, (РГ)2 , дешифраторы, управляющие коммутатором, (ДШ)1, (ДШ)2, а также трансформаторный и оптронные гальванические разделители, через которые осуществляется связь с контроллером.

На ФВИ поступает напряжение сетевой частоты. На выходах ФВИ вырабатываются четыре последовательности прямоугольных импульсов(фазы) Ф1-Ф4. Фронты импульсов каждой из указанных последовательностей совпадают с моментами перехода через сетевого напряжения. ФВИ вырабатывает также импульсы сброса СЧ, следующие с удвоенной по отношению к сети частотой.

Кварцевый генератор меток ГН вырабатывает импульсы длительностью около 0,2 мкс, следующие с частотой 2,5 МГц. Через схему совпадения импульсы поступают на вход 16-разрядного счетчика. С помощью фиксирующих схем, установленных на входах четырех старших разрядах СЧ, вырабатываются 3 последовательности импульсов п1, п2, п3. Передний фронт импульсов п1 соответствует 24576 меткам (6000Н), что соответствует 9,8304 мс, передний фронт п2-16384 меткам (4000Н) или 6,5536мс, передний фронт 8192 меткам (2000Н) или 3,2768 мс, а задний фронт п3 совпадает с передним фронтом п2. Задние фронты п1 и п2 определяются импульсами сброса, вырабатываемыми в моменты прохождения сетевого напряжения через ноль. Первый такт интегрирования задается управляющим сигналом, определяемым логической комбинацией [Ф3*п1]. При единичном значении этого сигнала ИН находится в режиме интегрирования (ключ К7 замкнут),а при нулевом – в режиме хранения (ключ К7 разомкнут). При изменении частоты сети изменяется только положение заданного фронта п1 и соответственно длительности режима хранения ИК. Таким образом, в первом такте интегрирования напряжение на выходе интегратора изменяется под действием входного напряжения и достигает уровня, зависящего только от величины входного сигнала к независящего от периода сетевого напряжения.

Начало второго такта интегрирования происходит по переднему фронту Ф4. При этом замыкается ключ КВ и счетные импульсы начинают проходить через схему гальванического разделение в контроллере. Под действием напряжением ОИ напряжение на выходе ИН изменяется от уровня, достигнутого в конце первого такта, стремясь к нулю и далее в область положительного напряжения. При равенстве напряжений срабатывает КМП и УЛУ останавливает прохождение счётных импульсов в контроллер, фиксируя конец преобразования. Одновременно по сигналу УЛУ интегратор переводится в режим обнуления и в промежуток времени, оставшийся до конца второго такта, конденсатор ИН разряжается до нуля.

В течении второго такта ключ К7 разомкнут и напряжение на входе ПУ и соответственно на выходе ИУ не влияет на работу ИН.

В интервале, когда логический сигнал [Ф1*Ф2*п2] имеет низкий уровень, замкнут ключ К3 и разомкнут ключ К4, при этом от источника Е через ограничительный резистор на вход АЦП протекает тренировочный ток, замыкающий через подключенную пару контактов коммутатора, линию связи с датчиком и внутреннее сопротивление датчика.

Величина тренировочного тока выбирается существенно больше нижней допустимой границы коммутируемоготока, указанной в ТУ на безъякорные реле РКГ15, используемые в коммутаторе, и значительно меньше верхнего предельного значения.

Протекание тренировочного тока через контакты реле препятствует возникновению на них окисных пленок, нарушающих контакт. Импульс тренировочного тока используется одновременно и для контроля исправности линии связи с датчиком. В интервале времени, задаваемом низким уровнем логического сигнала [Ф1*Ф4*п3], УЛУ определяет уровень сигнала в точке «0» структурной схемы. Если цепь датчика оборвана, то в этой точке устанавливается высокий уровень и в УЛУ вырабатывается сигнал “обрыв”, передаваемый далее по линии “флаги” в контроллер. Если цепь датчика исправна, то падение напряжение от импульса тренировочного тока, возникающее в низкоомной (менее 10 кОм) цепи датчика, мало и сигнал “обрыв” не вырабатывается.

Ключ К4 служит для компенсации тока утечки от источника Е на вход АЦП. В течение всего периода работы АЦП, за исключением интервала времени, в который проходит тренировочный импульс, этот ключ замкнут, а ключ КЗ разомкнут и ток утечки от источника Е замыкается на общую точку. В интервале времени, определяемым низким уровнем логического сигнала [Ф1*Ф4*п2], на регистры управляющего слова (РУС) РГ1 и РГ2 переводиться принудительно в состояние высокого уровня. На выходах ДШ1, ДШ2 этому состоянию РУС соответствует комбинация сигналов, обуславливающая замыкание ключа К1 АЦП и размыкание всех контактов коммутатора. Таким образом, в интервале “блокировка РУС” вход АЦП подключен на общую точку, а все каналы коммутатора разомкнуты. В течении этого же интервала контроллер передает по линиям “управляющее слово” и “тактовые импульсы” новое управляющее слово, которое записывается в РГ1 и РГ2. После снятия сигнала “блокировка РУС” это слово поступает на дешифраторы ДШ1, ДШ2 и обеспечивает включение нужного канала коммутатора, а также через выход “К5,К6” РГ2- установку нужного диапазона измерения АЦП. Четыре старших разряда поступают на ДШ1 и задают адрес одного из 10 рабочих каналов, либо адрес вспомогательных каналов – компенсации температуры холодных спаев термопар, коррекция рабочего тока термопреобразователей сопротивления, коррекции нулевого уровня АЦП и калибровки коэффициента передачи АЦП. Три следующих разряда задают адрес требуемого модуля коммутатора, а младший разряд определяет диапазон измерения АЦП. Сдвиг нулевого уровня характеристика, получаемый за счет смещения вводимого на вход КМП от ОИ, обеспечивает возможность обработки сигналов отрицательной полярности для соответствующих видов термопар. Величина выходного кода, соответствующая значению около 45000, вызывает в УЛУ сигнал передачи, воздействующий на интегратор и передающий его в режим обнуления.

Похожие работы

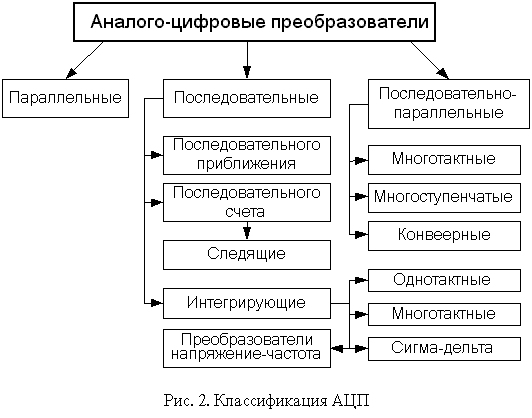

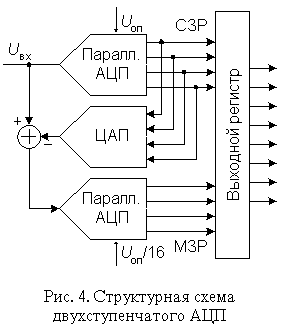

... пределов допускаемой основной погрешности. 3. УСТРОЙСТВО И РАБОТА МОДУЛЯ ПО СТРУКТУРНОЙ СХЕМЕ. УСТРОЙСТВО И РАБОТА МОДУЛЯ ПО ПРИНЦИПИАЛЬНОЙ СХЕМЕ. Структурная схема стробоскопического аналого – цифрового преобразователя, предназначенного для использования в системах с межмодульным параллельным интерфейсом МПИ представлена на рисунке 3.1. Рис. 3.1. Структурная схема стробоскопического АЦП. ...

... и 20-разрядном разрешении составляет 60-80 мс, а минимальное время преобразования АЦП HI-7159 для 18-разрядного разрешения и той же частоты режекции составляет 140 мс. В настоящее время ряд ведущих по аналого-цифровым ИМС фирм, такие как Analog Devices и Burr-Brown, прекратили производство АЦП многотактного интегрирования, полностью перейдя в области АЦ-преобразования высокого разрешения на сигма- ...

... ів 2001 Техническое задание Разработать быстродействующтий многоканальный АЦП с управлением от микроконтроллера. АПЗ.38.098424.003 ТЗ Изм Лит № докум Подпись Дата Аналого цифровой преобразователь Техническое задание Лит Лист ...

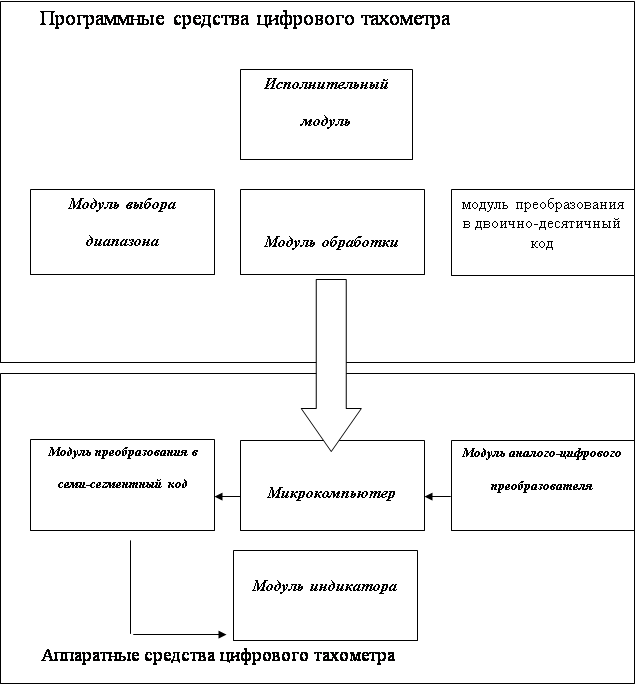

... действия системы. 3. Проектирование аппаратных средств системы 3.1 Разработка принципиальной схемы системы Основу проектируемого устройства составляет центральный процессор (ЦП). В разрабатываемом цифровом тахометре ЦП строится на основе микропроцессора 8086. При разработке структуры блока ЦП возникают задачи разделения (демультиплексирования) шины адреса/данных буферирования шин адреса и ...

0 комментариев