Навигация

Источников прерываний, из них 14 – с программируемым приоритетом

19 источников прерываний, из них 14 – с программируемым приоритетом.

Энергопотребление:

Общее потребление - не более 150 мА на частоте 50 МГц. Имеются режимы с пониженным энергопотреблением: IDLE и POWER DOWN.

Температурный диапазон, корпуса:

Существует четыре разновидности по температурному диапазону работы: коммерческий (0...+70 градусов), расширенный (-40...+85), автомобильный (-40...+125) и военный. Кроме того, микроконтроллеры могут быть подвергнуты динамической электротермотренировке.

ИС устанавливаются в 100-выводные корпуса типов QFP или SQFP.

2.2 Внутренняя архитектура

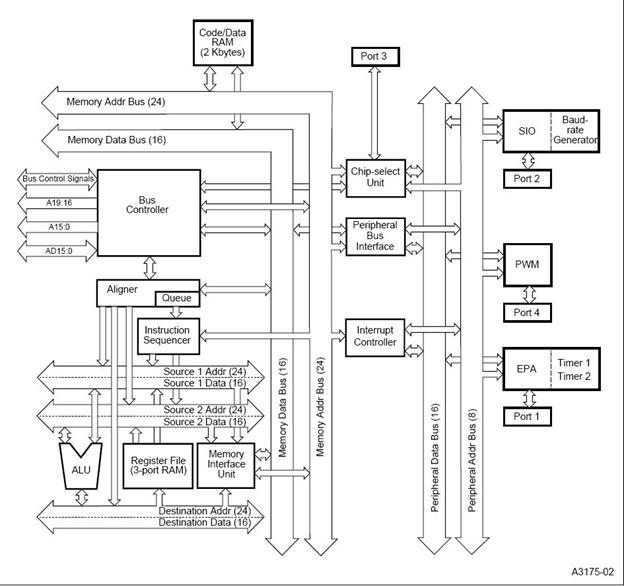

Внутренняя архитектура контроллеров серии 296 показана на рис. 2 (на примере 80296SA). Очевидно, что данные микроконтроллеры спроектированы на основе принстонской архитектуры (основанной на принципах фон Неймана), т.к. память для хранения данных и команд не разделена (единое адресное пространство), а микроконтроллер содержит две шины: данных и адреса.

![]()

![]()

Рис.2 Внутренняя архитектура кристалла 80296SA

На частоте 50 МГц ЦПУ выполняет до 16 млн. оп/с на стандартном наборе команд и до 12,5 млн. оп/с при использовании специальных команд цифровой обработки сигналов. Память ЦПУ имеет одно адресное пространство размером 6 Мбайт, в котором находятся регистры общего назначения, регистры специального назначения, встроенная программная память, внешняя память для программы и данных. ПЗУ имеет объем 2 кбайт и оснащено защитой от несанкционированного доступа. Контроллер памяти работает с 16- и 24-разрядной внешней шиной, причем ширина шины может динамически переключаться, можно вводить циклы ожидания.

Основные компоненты CPU во всех микроконтроллерах семейства MCS-96 — это Регистровый Файл (Register File) и Регистровое Арифметико-Логическое Устройство (Register/Arithmetic Logic Unit - RALU). Регистровый файл - это адресуемое пространство регистров процессора. Ячейки от 00h до 17h - это управляющие регистры ввода-вывода или регистры cпециальных функций (Special Function Registers - SFR). Ячейки 18h и 19h содержат указатель стека, они могут использоваться как обычная RAM-память, когда не выполняются стековые операции. Остальные байты регистрового файла служат как обычная RAM-память, доступная как байт, слово или как двойное слово. CPU выполняет вычисления в RALU. RALU содержит 17-битное арифметико-логическое устройство (ALU), слово состояния программы (PSW), счетчик команд (PC), счетчик циклов и три временных регистра. RALU работает напрямую с регистровым файлом, таким образом, устраняются пересылки через аккумулятор, и обеспечивается прямое управление операциями ввода/вывода через SFR.

Другие составные микропроцессора рассмотрим в пункте 2.3

2.3 Состав встроенных устройств

Таймеры:

Два 16-разрядных таймера TIMER1 и TIMER2 обеспечивают синхронизацию работы устройства ввода-вывода импульсных сигналов с реальным временем и внешними событиями. TIMER1 синхронизируется изнутри, тогда как TIMER2 синхронизируется снаружи.

Генератор сигналов CHIP SELECT (CHIP SELECT UNIT):

Этот узел появился ещё у кристалла 8XC196NP, имеется у 8XC296SA. Он позволяет существенно упростить аппаратуру, необходимую для подключения внешней памяти к процессору, и, тем самым, удешевить систему. Он может генерировать до 6-ти сигналов выборки (Chip Select), с независимо устанавливаемыми циклами ожидания и шириной шины. Кроме того, кристаллы, имеющие Chip Select Unit, имеют демультиплексированную шину, что позволяет отказаться от внешних регистров-защелок и использовать медленную и дешевую память, сохранив при этом быстродействие системы.

Импульсный ввод/вывод EPA (EVENT PROCESSOR ARRAY):

Данный узел пришел на смену HSIO, начиная с кристалла 8XC196KR. EPA имеет более простую архитектуру, чем HSIO, обладая при этом лучшей разрешающей способностью. В HSIO, все входные каналы имеют общую память, 7-уровневое FIFO (first in/first out), в которой запоминаются временные отметки, соответствующие событиям на входах. То же касается выходных линий HSIO - все они имеют общую память (8 ячеек), в которую процессор записывает команды для всех выходных каналов HSIO. Поэтому за один такт HSIO может обработать только один входной и один выходной канал. В EPA, каждый канал имеет свой собственный буфер, а выдача и прием сигналов производятся одновременно по всем каналам. Поэтому разрешающая способность EPA выше, чем у HSIO, в 4 раза. Кроме того, EPA - более гибкий узел: каждый его канал может служить и входом, и выходом, тогда как HSIO имеет 4 выходных, 2 входных, и 2 двунаправленных линии.

Дополнительное ОЗУ (Code RAM):

Это дополнительное ОЗУ, в котором можно размещать исполняемый код. Этот код будет выполняться очень быстро, так как Code RAM имеет 16-разрядный интерфейс с нулевым циклом ожидания. Code RAM может принести существенную пользу в задачах, где требуется максимально быстрое выполнение только небольших фрагментов кода, позволяя при этом использовать сравнительно медленное и дешевое 8-битное ПЗУ для хранения остальной части программы. Конечно, эту память можно использовать и для размещения данных или стека.

MCS-96 содержит полный набор команд, включающий операции с битами, байтами, словами, двойными словами (беззнаковые 32 бит), длинные операции (32 бит со знаком), работу с флагами, а также переходы и вызовы подпрограмм. Все стандартные логические и арифметические команды работают как с байтами, так и со словами. Команды перехода по установке бита (Jump Bit Set) и очистке бита (Jump Bit Clear) могут работать с каким-либо регистром SFR или с другими байтами регистрового файла. Эти быстрые битовые операции позволяют ускорить функции ввода/вывода.

0 комментариев